# Proceedings

## Sisal '93

John T. Feo

editor

October 1993

#### **DISCLAIMER**

**This document was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor the University of California nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial products, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoritism by the United States Government or the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government thereof, and shall not be used for advertising or product endorsement purposes.**

**Work performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract W-7405-Eng-48.**

# Proceedings

## Sisal '93

Editor

John T. Feo

Lawrence Livermore National Laboratory

Livermore, California

Sponsored by

*Computer Research Group*

*Lawrence Livermore National Laboratory*

*Livermore, CA*

October 3-5, 1993

San Diego, California

**MASTER**

**DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED**

*for*

## Contents

|                                                                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Programmability and performance issues: The case of an iterative partial differential equation solver</b><br><i>Chinhyun Kim, Jean-Luc Gaudiot and Wlodek Proskurowski</i> | 1   |

| <b>Implementing the kernal of the Australian Region Weather Prediction Model in Sisal</b><br><i>Greg Egan</i>                                                                 | 11  |

| <b>Even and quarter-even prime length symmetric FFTs and their Sisal Implementations</b><br><i>Jaime Seguel and Dorothy Bollman</i>                                           | 18  |

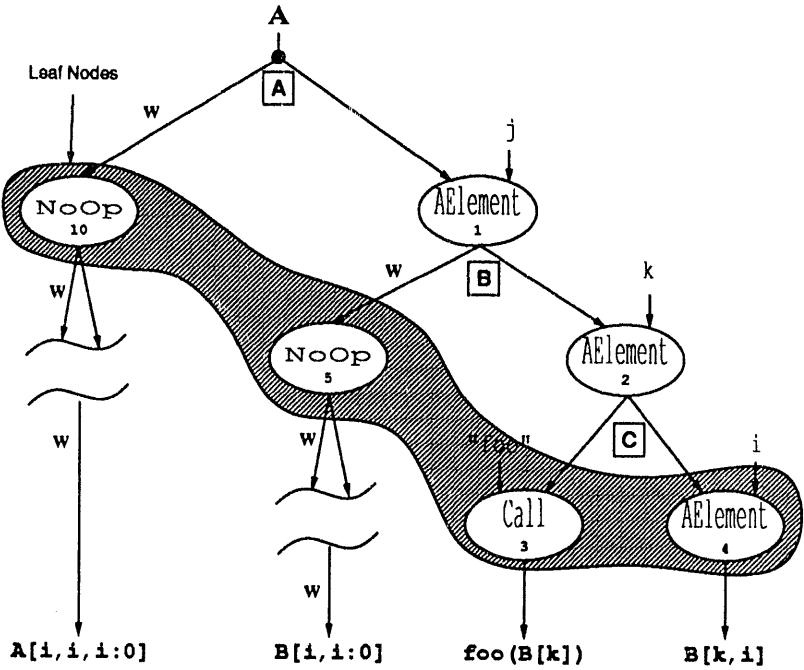

| <b>Top-down thread generation for Sisal</b><br><i>Bhanu Shankar, Wim Böhm and Walid Najjar</i>                                                                                | 25  |

| <b>Overlapping Communications and Computations on NUMA architectures</b><br><i>Richard Wolski and John Feo</i>                                                                | 40  |

| <b>Compiling technique based on dataflow analysis for functional programming language Valid</b><br><i>Eiichi Takahashi, Rin-ichiro Taniguchi and Makoto Amamiya</i>           | 47  |

| <b>Copy elimination for true multidimensional arrays in Sisal 2.0</b><br><i>Steven Fitzgerald</i>                                                                             | 59  |

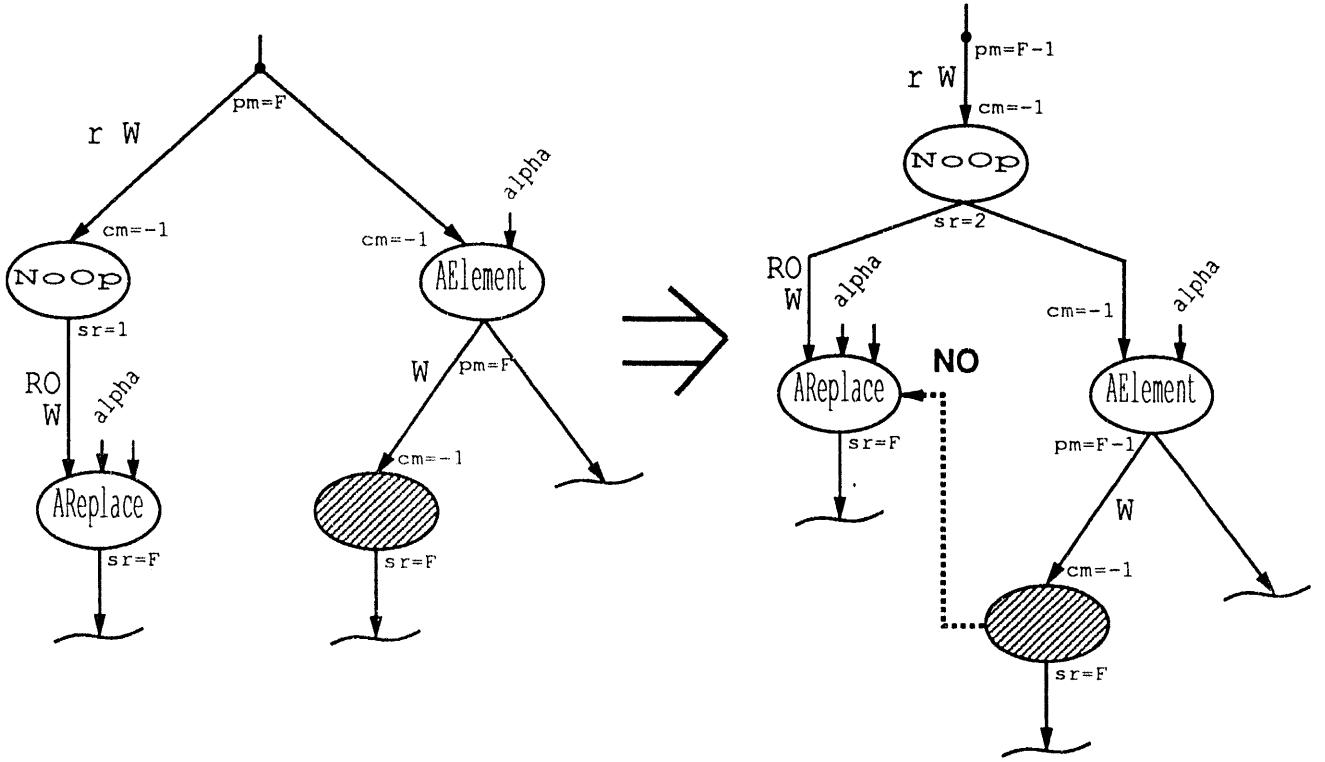

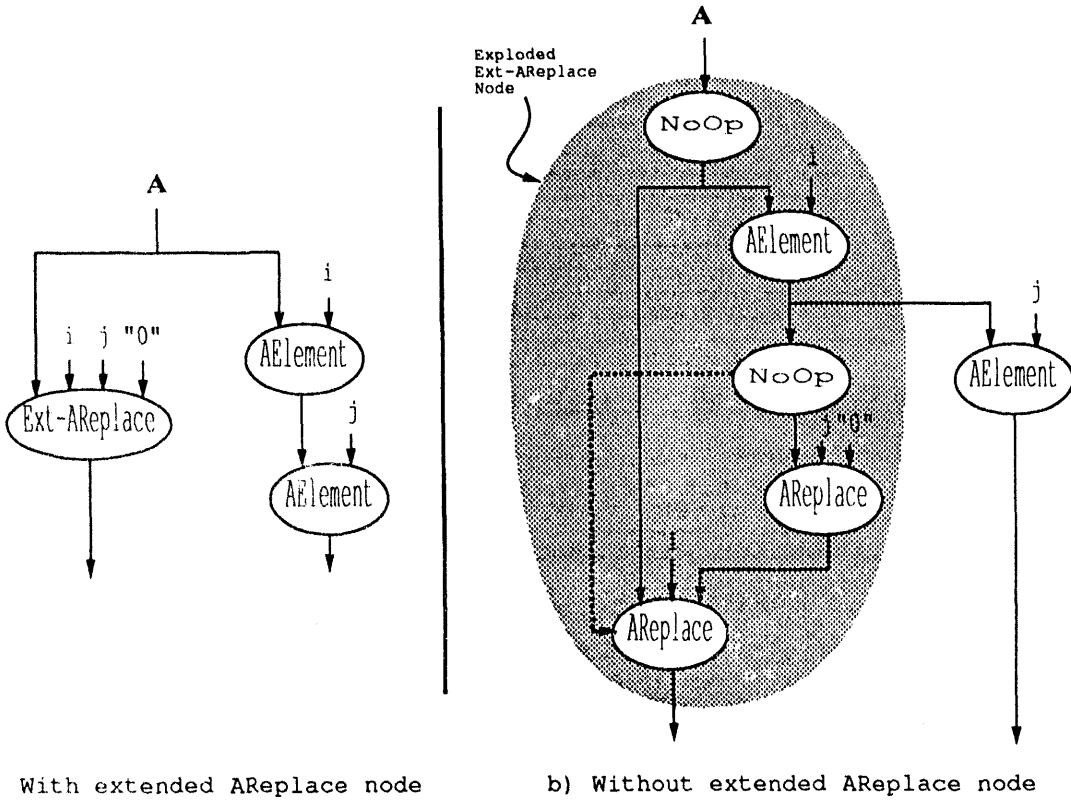

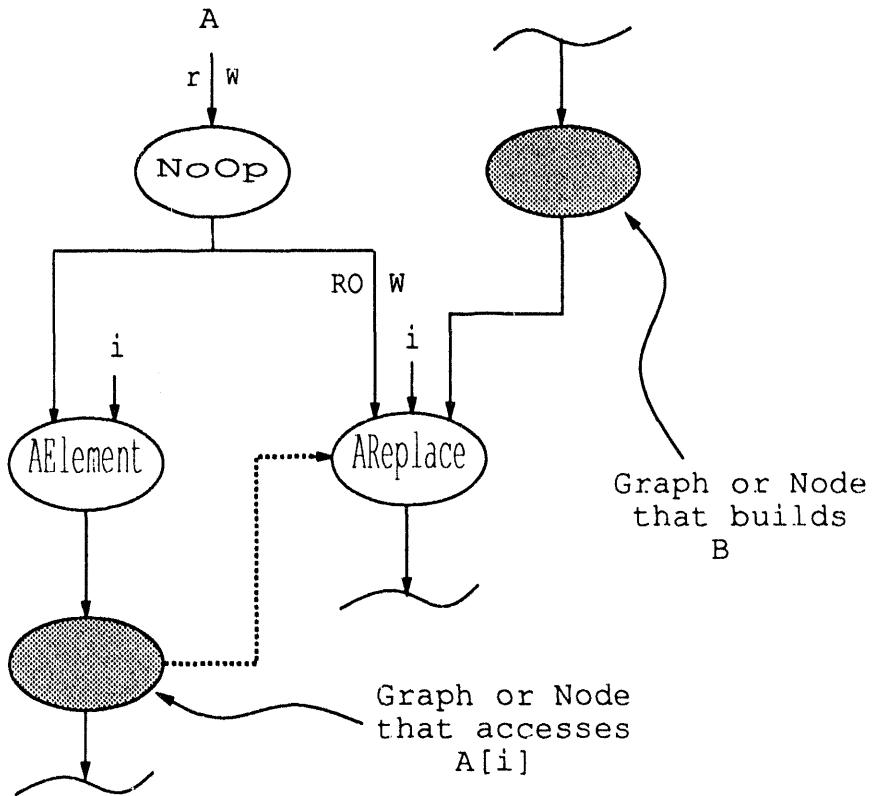

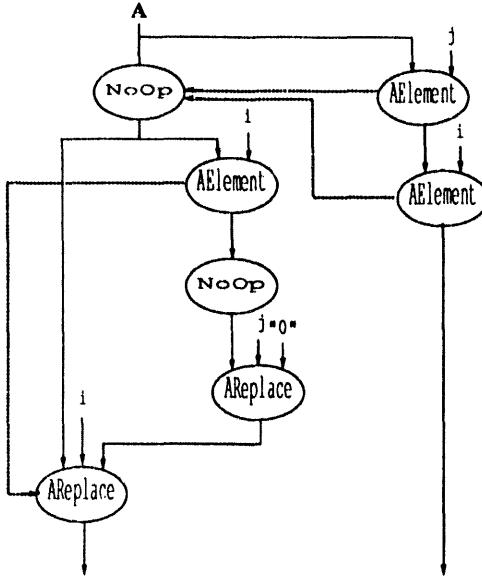

| <b>Increasing Parallelism for an optimization that reduces copying in IF2 graphs</b><br><i>Steven Fitzgerald</i>                                                              | 74  |

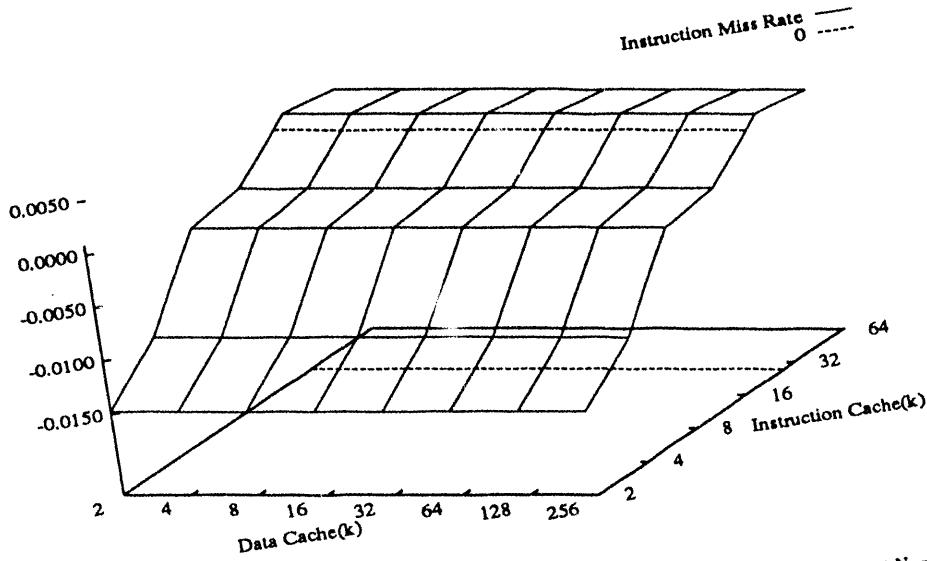

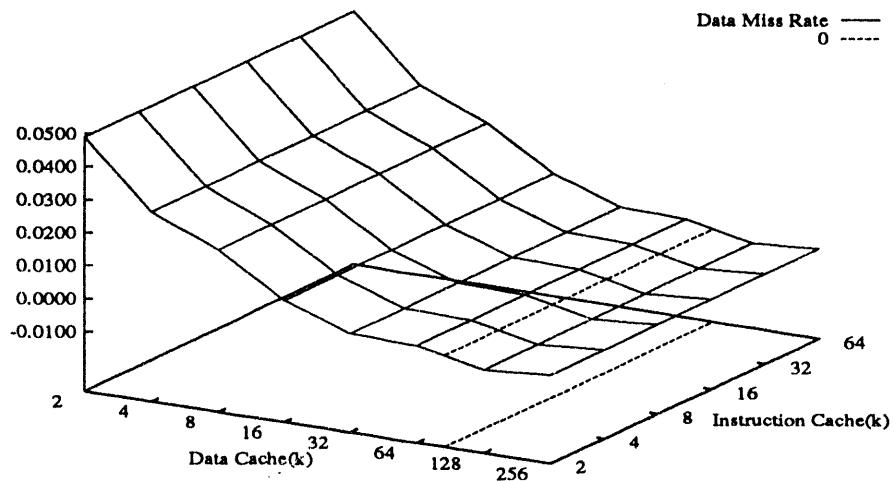

| <b>Caching in on Sisal: Cache performance of Sisal vs. FORTRAN</b><br><i>Phil Nico and Arvin Park</i>                                                                         | 85  |

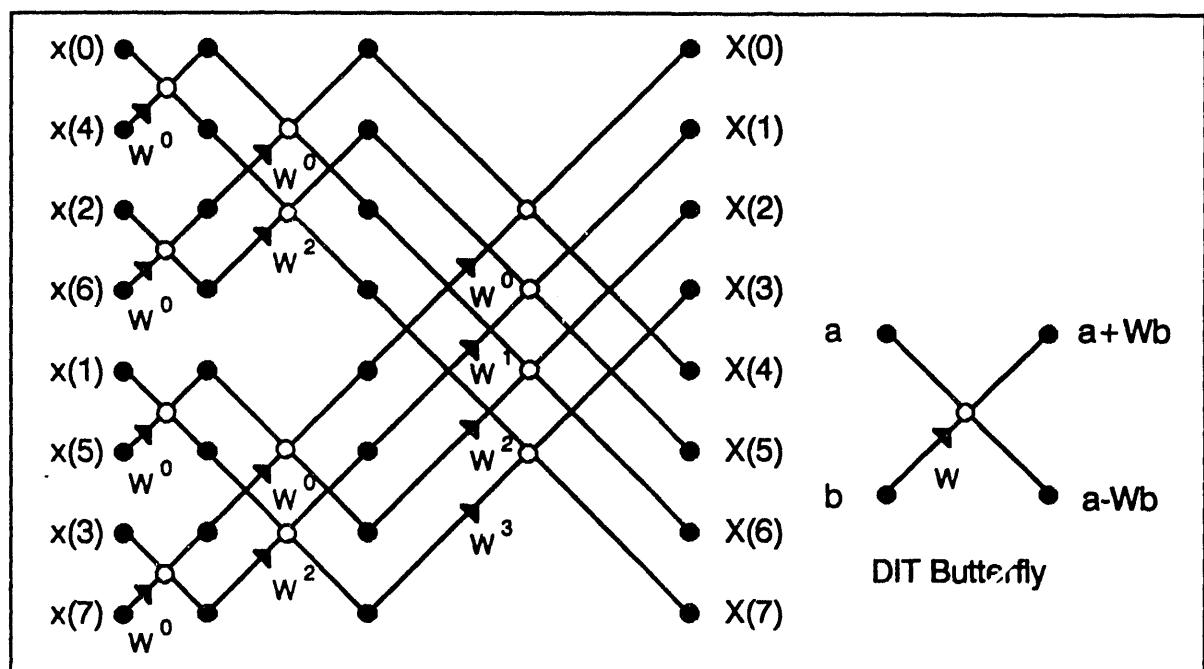

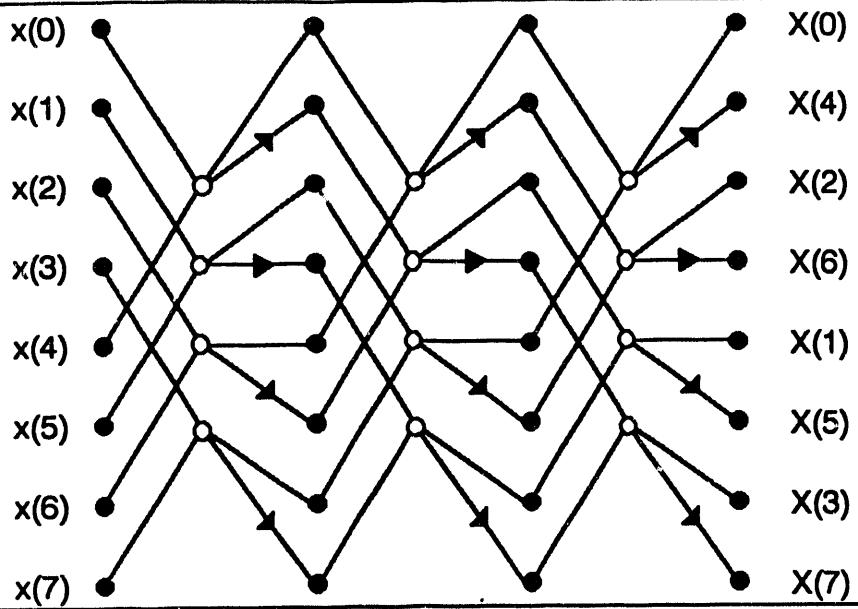

| <b>FFT algorithms on a shared-memory multiprocessor</b><br><i>Anthony Criscenti and Greg Egan</i>                                                                             | 91  |

| <b>A parallel implementation of nonnumeric search problems in Sisal</b><br><i>Andrew Sohn</i>                                                                                 | 103 |

|                                                                                                                                     |     |

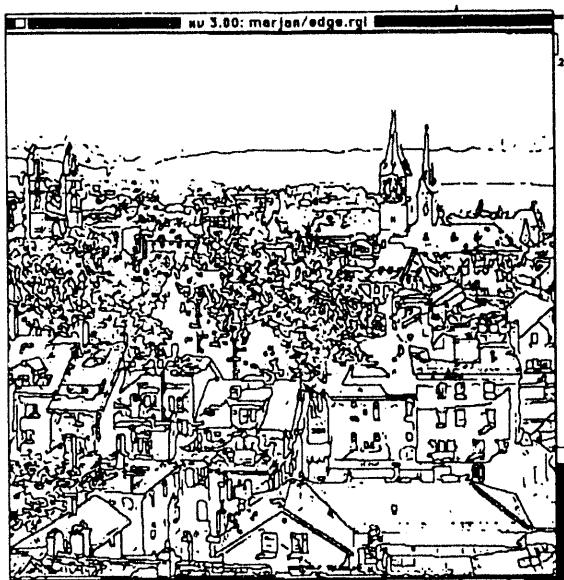

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Computer vision algorithms in Sisal</b><br><i>Srdjan Mitrovic and Marjan Trboina</i>                                             | 114 |

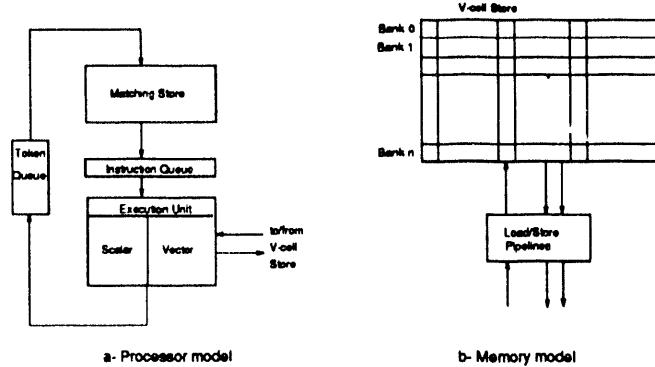

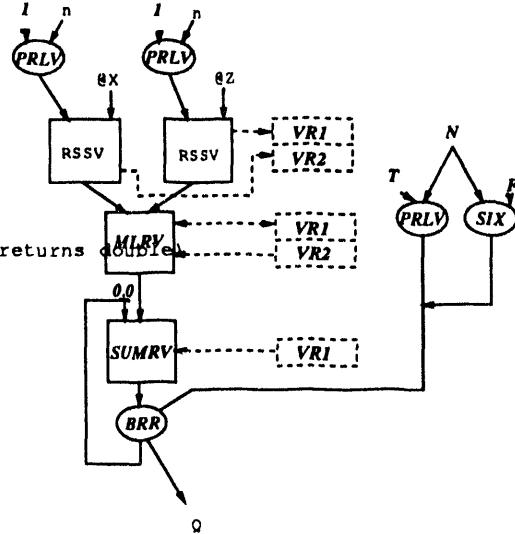

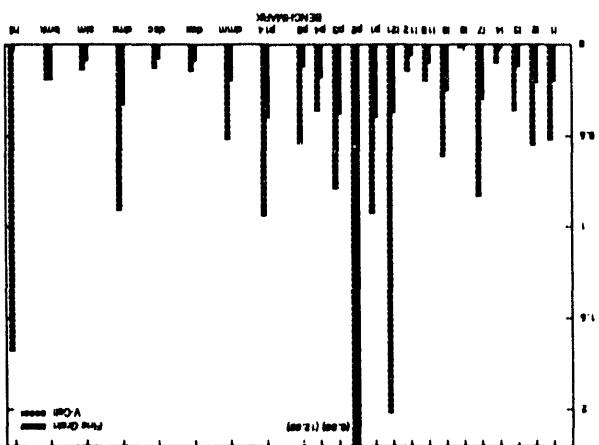

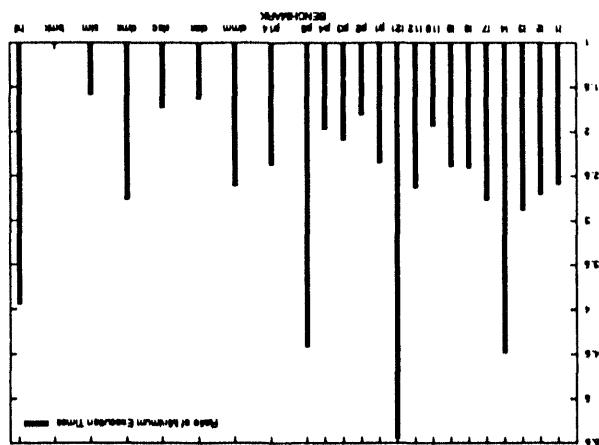

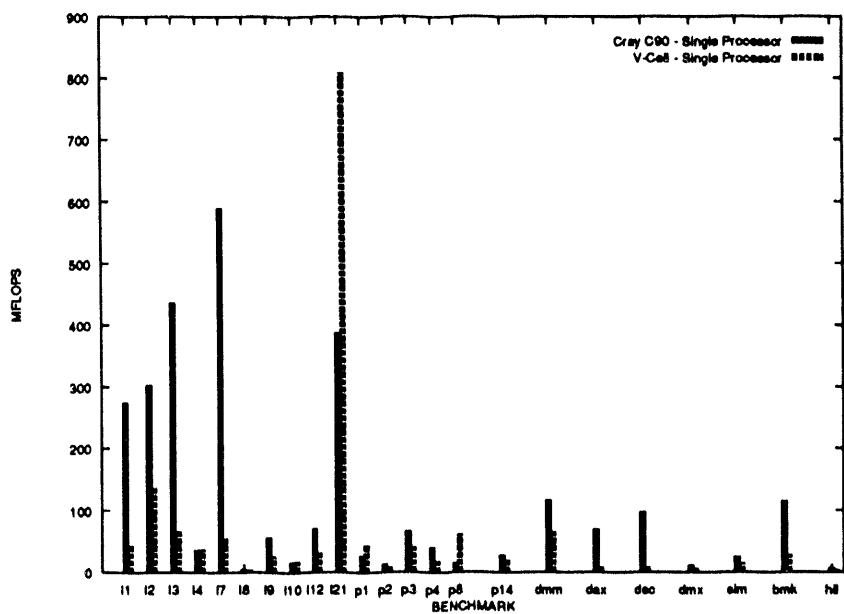

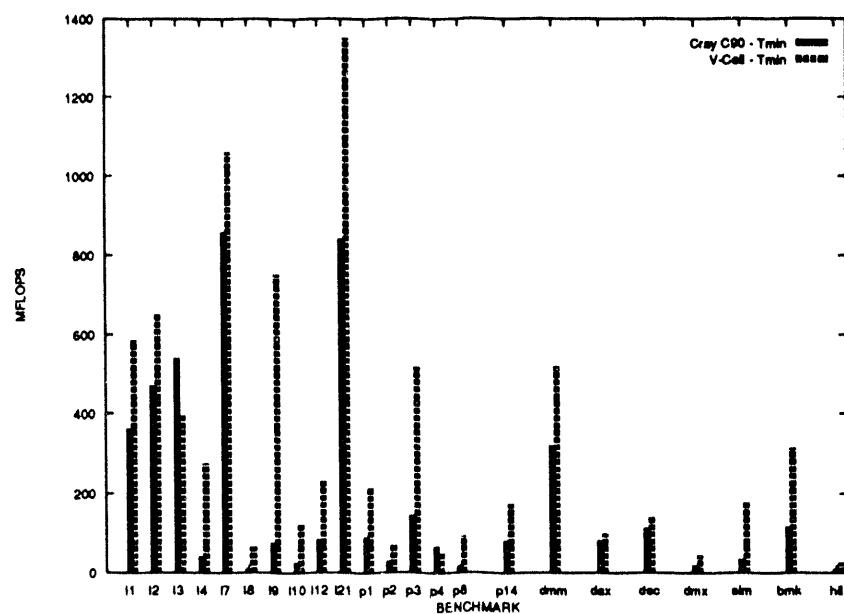

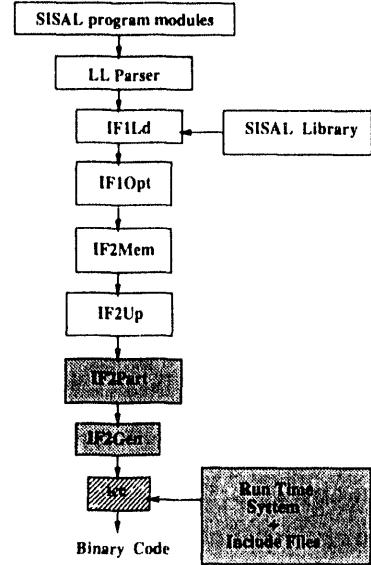

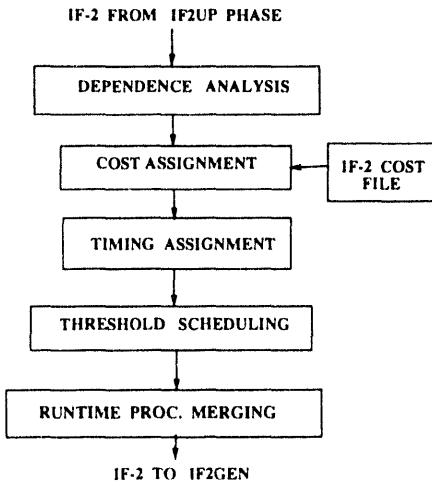

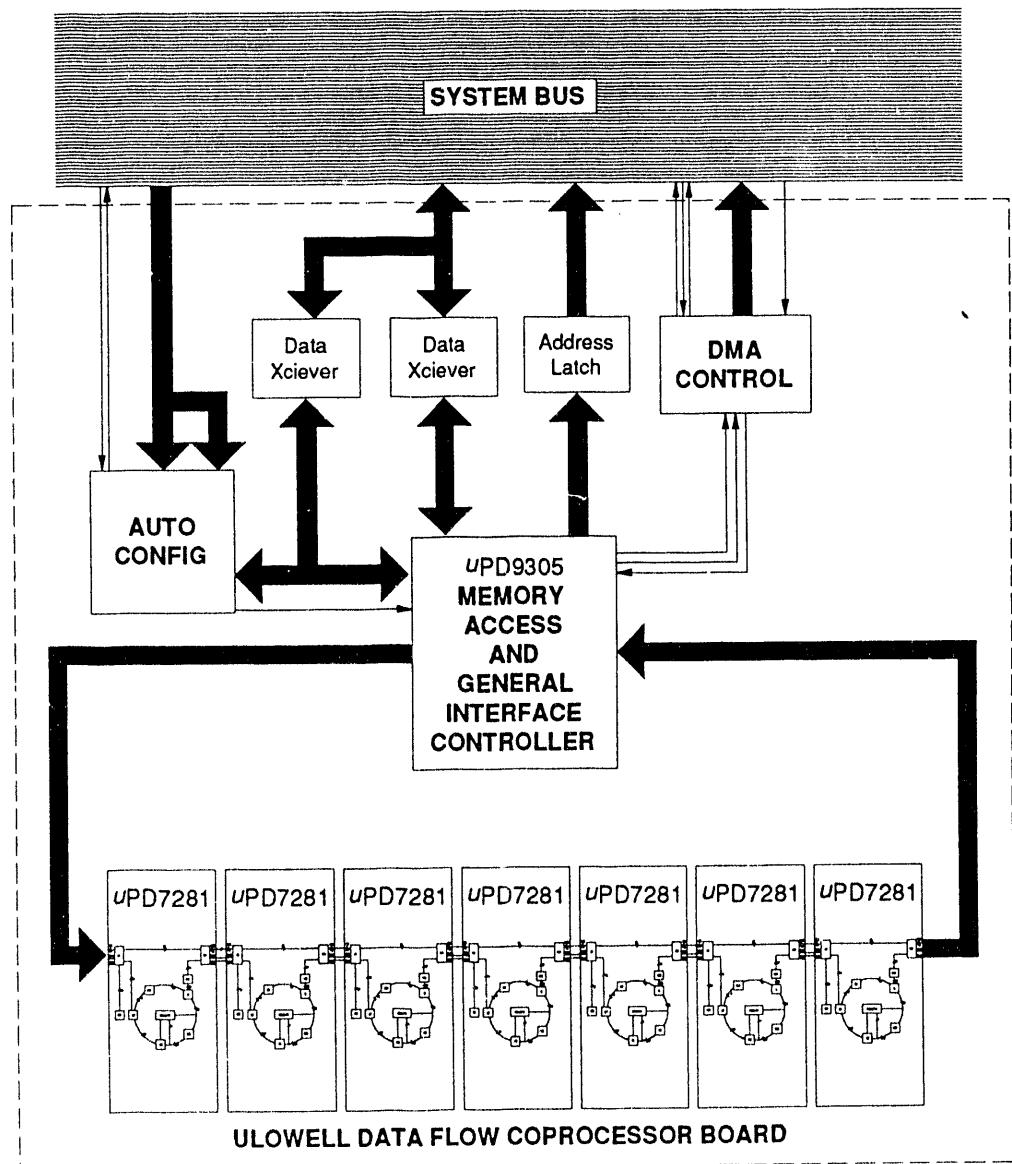

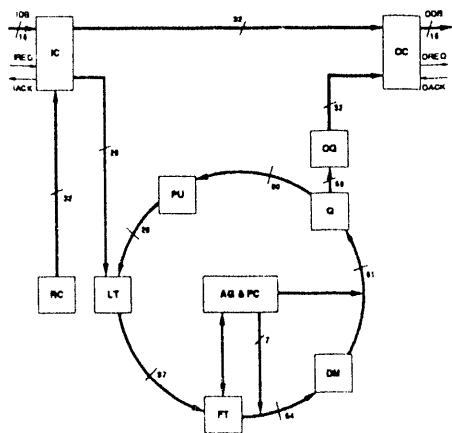

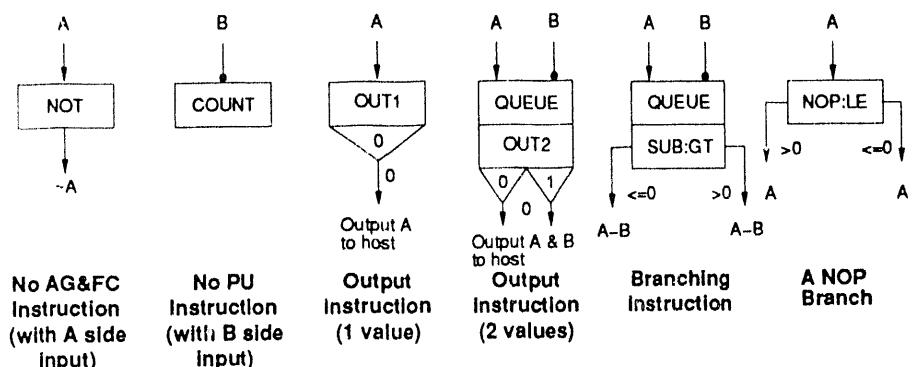

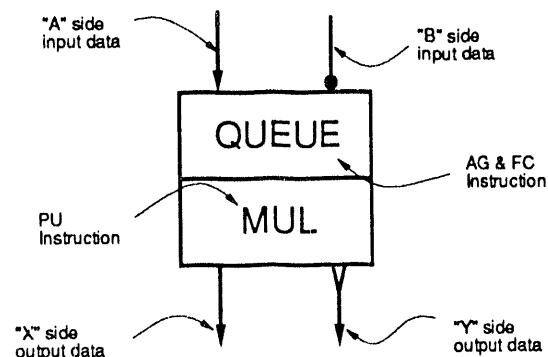

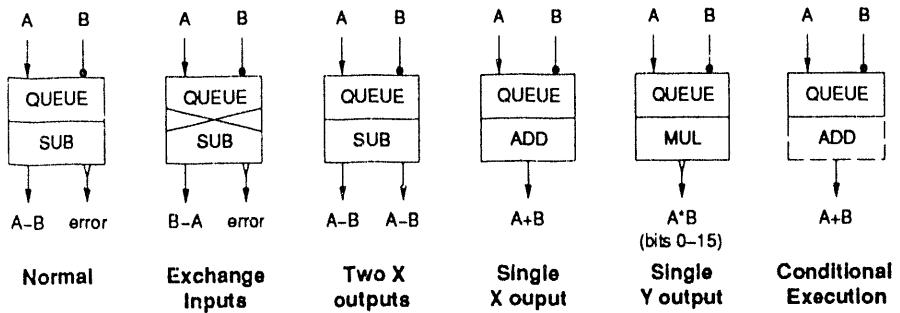

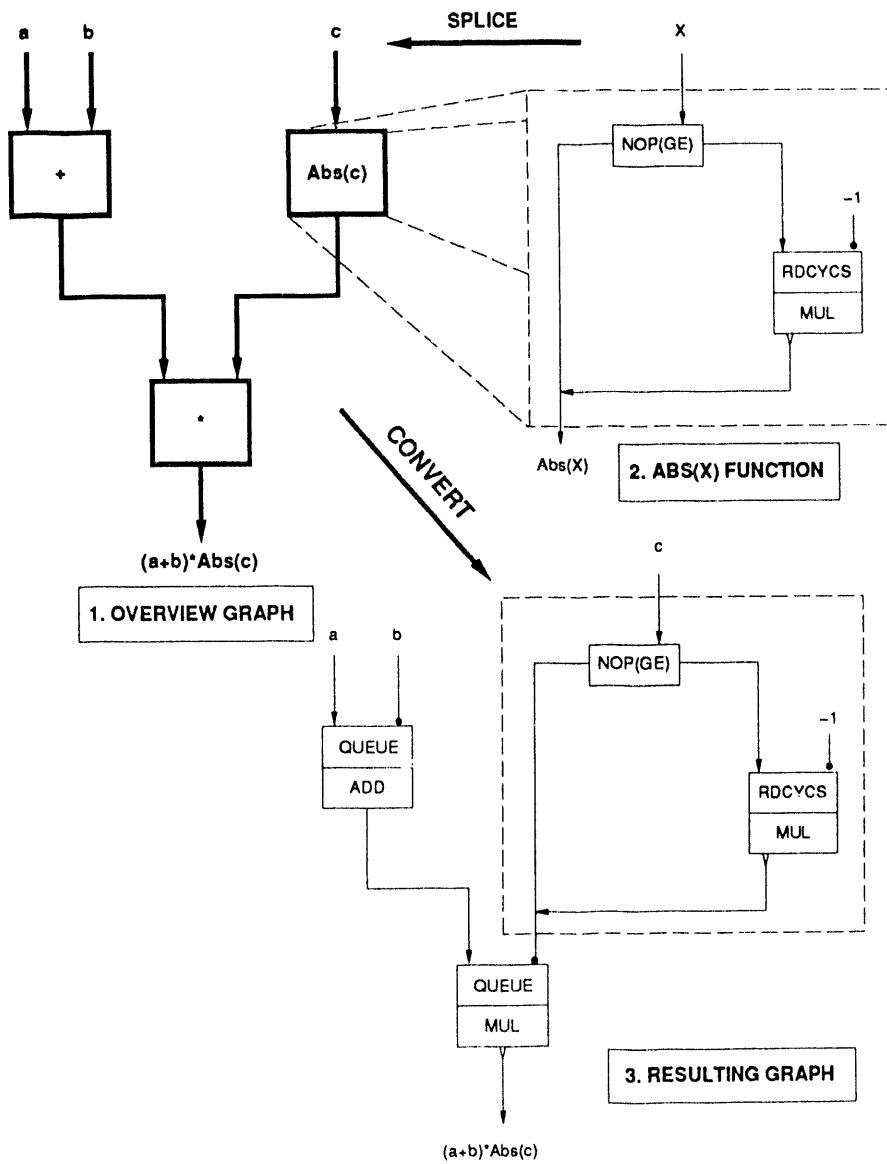

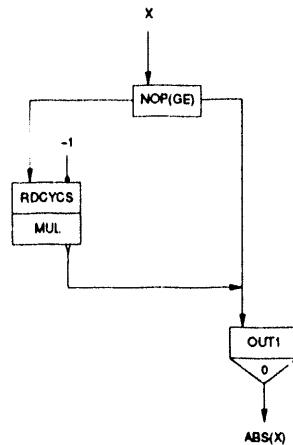

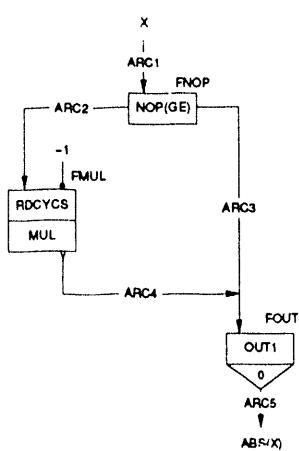

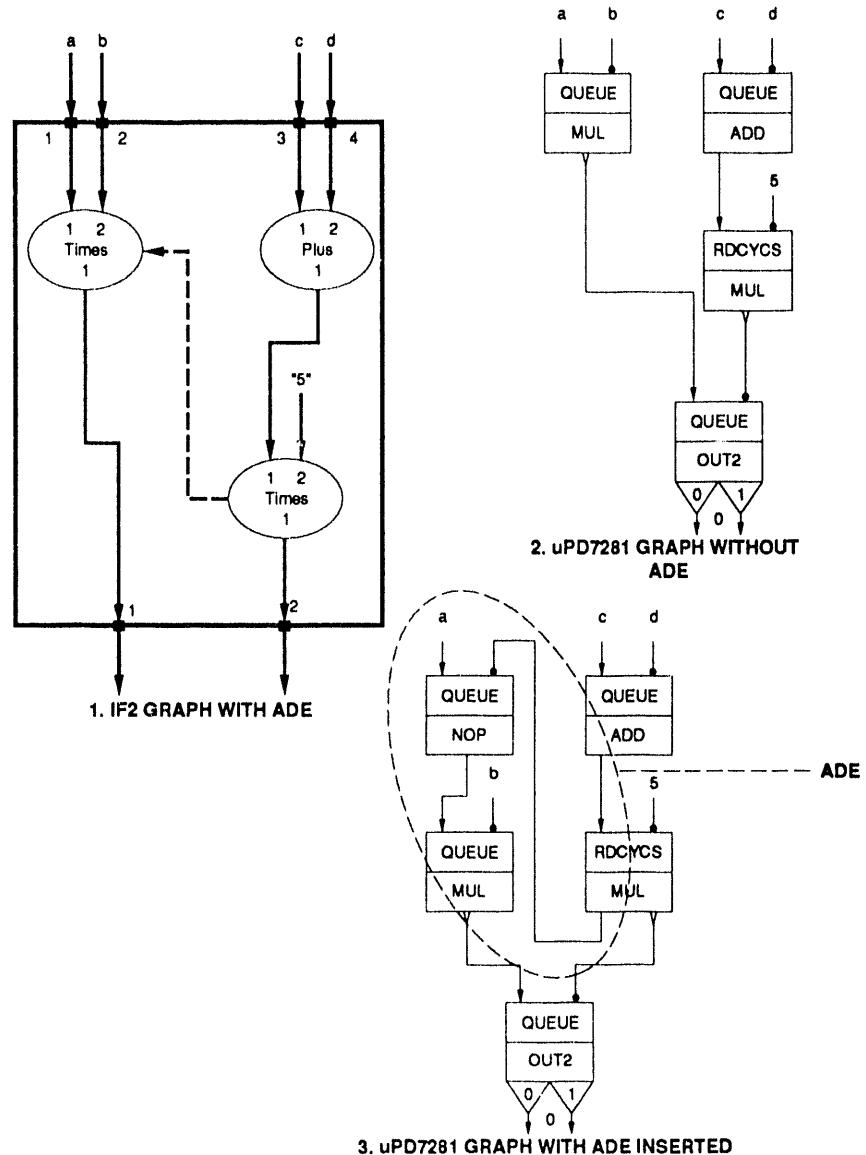

| <b>Compilation of Sisal for a high-performance data driven vector processor</b><br><i>William Miller, Walid Najjar and Wim Böhm</i> | 120 |

| <b>Sisal on distributed memory machines</b><br><i>Sande Pande, Dharma Agrawal and Jon Mauney</i>                                    | 134 |

| <b>A virtual shared addressing system for distributed memory Sisal</b><br><i>Matthew Haines and Wim Böhm</i>                        | 151 |

| <b>Developing a high-performance FFT algorithm in Sisal for a vector supercomputer</b><br><i>John Feo and David Cann</i>            | 164 |

| <b>Implementation issues for IF2 on a static data-flow architecture</b><br><i>Linda Wilkins and Aaron Enright</i>                   | 175 |

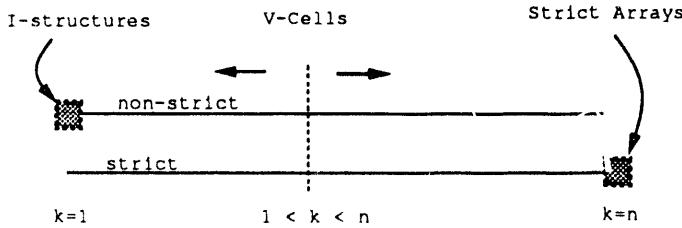

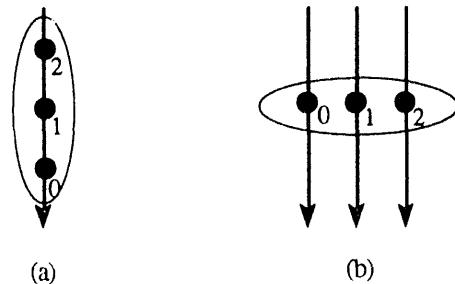

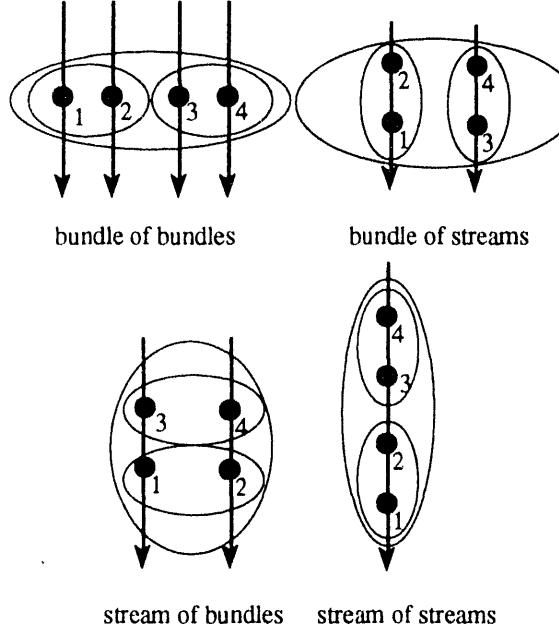

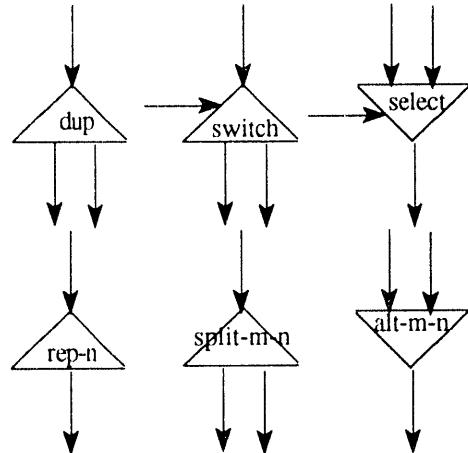

| <b>Systematic control of parallelism in array-based data-flow computation</b><br><i>Kanad Roy and Carl McCrosky</i>                 | 189 |

# Programmability and Performance Issues: the Case of an Iterative Partial Differential Equation Solver\*

Chinhyun Kim Jean-Luc Gaudiot

Electrical Engineering-Systems Dept.

University of Southern California

Los Angeles, CA 90089-2563

Wlodek Proskurowski

Mathematics Dept.

University of Southern California

Los Angeles, CA 90089-1113

## Abstract

*In this paper, we use a specific example to discuss the viability of functional programming in the context of parallel computing. The traditional argument for functional languages has been programmability. Indeed, due to high-level abstractions and the implicit parallelism provided by functional languages, programmers are free to concentrate on the implementation of the algorithm at hand without being burdened with low-level machine execution details. We further report that it is possible to deliver both programmability and performance through functional programming. Some quantitative results from an experiment which consists of developing a multigrid elliptic Partial Differential Equation (PDE) solver are presented.*

## 1 Introduction

In current parallel programming style using imperative languages such as FORTRAN or C, an applications programmer needs to be aware of the architectural details of the target machine in order to generate an efficient program [7, 10]. This is due to the execution model (von Neumann) of most existing programming languages. Such practice makes writing parallel programs difficult. Furthermore, once written, porting a program to a machine with a different architecture virtually means rewriting the whole program. At present, however, no other programming languages can compete with imperative languages in performance.

Functional languages such as SISAL [5, 8] provide higher-level abstractions so that underlying machine architecture is transparent to a programmer. In addition, representation of parallel operations is implicit

in the language semantics. These features allow a programmer to concentrate on the implementation details of the algorithm at hand without worrying about parallelization and other low-level machine mechanisms. The drawback of functional languages, however, have been performance. Programming in functional languages can be a double-edged sword. That is, while high-level abstractions free programmers from low-level details, it could be difficult to achieve good performance.

Much work has been done in compilation techniques to improve the performance of functional languages [2]. It has been shown that the latest SISAL compiler called the Optimizing SISAL Compiler (OSC) [3] can compete with the FORTRAN compiler on CRAY machines [4]. The CRAY FORTRAN compiler can be considered one of the best commercially available optimizing compilers. Thanks to OSC, using the performance issue in the argument against functional programming has been substantially weakened. On the other hand, the alleged functional language feature of programmability issue has not been well substantiated.

A desirable (parallel) programming environment is one that shields a programmer from the low-level machine details without sacrificing performance. The objective of this paper, therefore, is to address the issues of programmability and performance of functional programming together by presenting some empirical results from an experiment. The experiment is based on a one semester graduate level course on numerical methods of elliptic Partial Differential Equations (PDE). In the course, four different algorithms for numerically solving elliptic PDEs are presented and each student is required to implement the PDE solvers within some specified time. In the course, students are free to use a programming language of his/her choice. The four iterative PDE solvers covered in the course are based on :

\*This work was supported in part by the National Science Foundation under grant No. CCR-9013965.

1. Basic iterative methods : Jacobi, Gauss-Seidel, and Successive Over Relaxation (SOR),

2. Multigrid method,

3. Preconditioned Conjugate Gradient (PCG) method (and Fast Poisson solvers),

4. Domain Decomposition method.

The experiment consists of participating in the course and implementing the PDE solvers in SISAL within the assigned date. Once the PDE solvers are written, their performance on various types of parallel machines are measured in addition to uniprocessor machines. There is to be no modifications made to the programs that run on various machines. Note that implementing the PDE solvers for parallel machines is not part of the course. In the course, students were to write programs only for sequential machines.

The programmer participating in the experiment had the following background at the start of the experiment:

- Understood programming language issues in general, but has not written any substantial SISAL programs prior to the experiment.

- Had no knowledge of the numerical PDE solver algorithms covered in the class prior to the experiment.

Due to space limitation, this paper concentrates the discussion on the implementation of a multigrid method. In section 2, the model problem used in the experiment is discussed. In addition, characteristics of the multigrid algorithm is described in some detail. Section 3 describes the implementation of a multigrid algorithm. In section 4, performance measurements of the implemented multigrid solver on sequential and parallel machines are described. In addition, the development time of each solver is described. Section 5 ends with some concluding remarks.

## 2 Description of the Problem

In this section, the model problem used in the experiment is discussed. In addition, two multigrid algorithms are described in some detail.

### 2.1 The Model Problem

The model problem used in the experiment is the following two-dimensional self-adjoint elliptic equation in the unit square with proper Dirichlet (static)

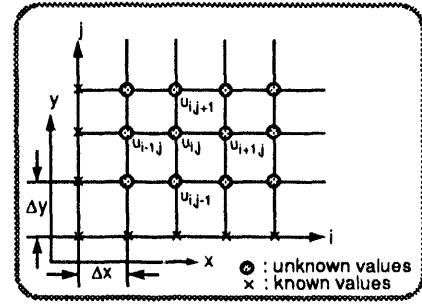

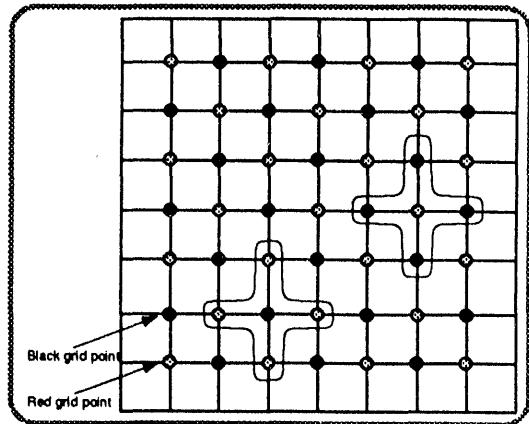

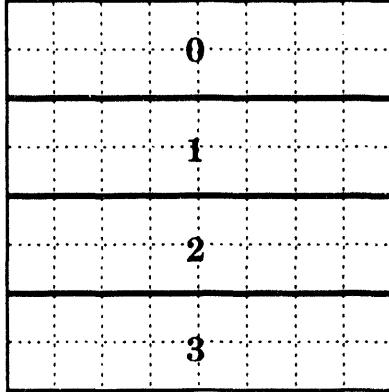

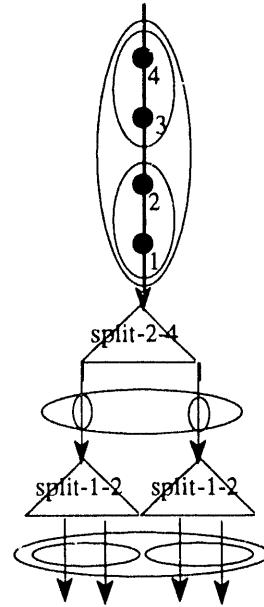

Figure 1: The finite difference method discretizes a continuous region into a finite number of grid points by dividing the region of interest into equal grid sizes.

boundary conditions :

$$-\operatorname{div}(k \operatorname{grad} u) = f$$

Two different values for the diffusion function  $k(x, y)$  are used. The first case is when  $k(x, y) = 1$ . This results in the well-known Poisson's equation :

$$-\left[\frac{\partial^2 u(x, y)}{\partial x^2} + \frac{\partial^2 u(x, y)}{\partial y^2}\right] = f(x, y)$$

In general, the resulting equation is of the following form :

$$-\frac{\partial}{\partial x}[k(x, y) \frac{\partial u(x, y)}{\partial x}] - \frac{\partial}{\partial y}[k(x, y) \frac{\partial u(x, y)}{\partial y}] = f(x, y)$$

In order to solve the problem numerically, the continuous partial differential equation needs to be discretized. In other words, solution of the dependent variables are determined only at discrete points within the problem domain although the variables vary continuously throughout the domain. In the experiment, the partial differential equation is discretized using the finite difference method. The finite difference method is based on Taylor series expansion in which the order of the *truncation error* depends on the number of terms selected from the Taylor series. In the experiment, second order approximation is used, *i.e.*, truncation error is of order  $O((\Delta x)^2, (\Delta y)^2)$ ;  $\Delta x$  and  $\Delta y$  are the grid spaces in the  $x$  and  $y$  axis, respectively (Figure 1). If  $\Delta x = \Delta y = h$ , an unknown variable  $u$  at discrete point  $x_i$  and  $y_j$  (when  $k(x, y) = 1$ ) can be approximated as in the following equation :

$$u_{i,j} = \frac{u_{i-1,j} + u_{i+1,j} + u_{i,j-1} + u_{i,j+1} + h^2 f_{i,j}}{4}$$

where  $0 \leq i \leq N$ , and  $0 \leq j \leq M$

Figure 2: When the diffusion function is not constant, using a staggered grid scheme results in a symmetric coefficient matrix.

The variables  $N$  and  $M$  are the number of grid points in the  $x$  and  $y$  directions, respectively. The  $u_{i,j}$  and  $f_{i,j}$  represent the variables  $u(x, y)$  and  $f(x, y)$  at discrete grid points  $x_i$  and  $y_j$ .

When  $k(x, y)$  is a function of  $x$  and  $y$ , *staggered grid* method is used so that the resulting coefficient matrix is symmetric and the  $O(h^2)$  accuracy is retained. The resulting difference equation looks like the following :

$$\begin{aligned}

u_{i,j} &= \frac{K_1 u_{i-1,j} + K_2 u_{i+1,j} + K_3 u_{i,j-1} + K_4 u_{i,j+1}}{K_0} \\

&\quad + \frac{h^2 f_{i,j}}{K_0} \\

K_0 &= k_{i-1/2,j} + k_{i+1/2,j} + k_{i,j-1/2} + k_{i,j+1/2} \\

K_1 &= k_{i-1/2,j} \\

K_2 &= k_{i+1/2,j} \\

K_3 &= k_{i,j-1/2} \\

K_4 &= k_{i,j+1/2}

\end{aligned}$$

Once the partial differential equation is discretized, a system of linear equations results which can be written in a vector form as shown below :

$$\mathbf{A}_{(n \times n)} \mathbf{u}_{(n \times 1)} = \mathbf{f}_{(n \times 1)}$$

- $\mathbf{A}$  is the coefficient matrix. Its size is  $n \times n$  and has the characteristics of being sparse and symmetric.

- $\mathbf{u}$  is a vector of unknown variables.

- $\mathbf{f}$  is a vector of the values of  $f(x, y)$  at discrete points.

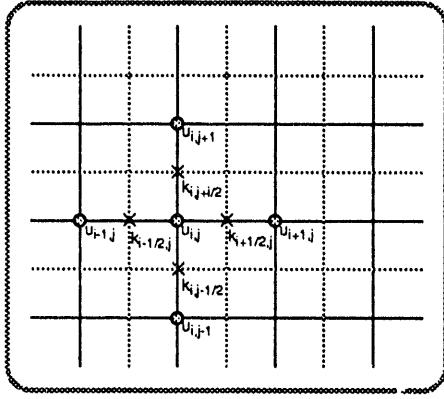

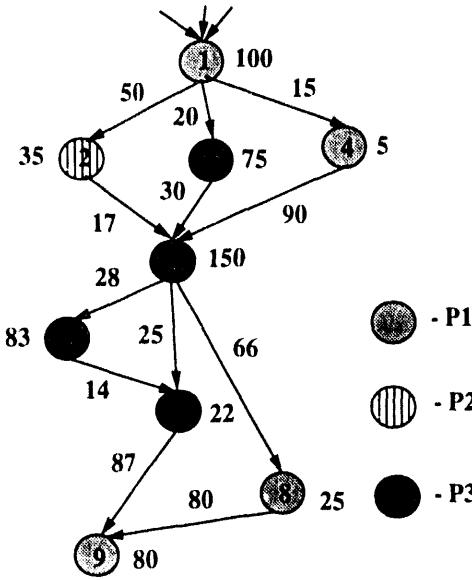

Figure 3: The top figure shows the V-cycle and the bottom figure shows the FMV-cycle.

## 2.2 Multigrid Method

The disadvantage of basic iterative methods is their slow rate of convergence. Of the three methods listed, SOR has the best performance. This, however, is based on the assumption that the optimum value of the weighting parameter  $\omega_{opt}$  is known [6]. Unfortunately, the value of  $\omega_{opt}$  is usually unknown. Conceptually, the slowness of the basic iterative methods is attributed to the fact that they act as a low-pass filter with a fixed cutoff frequency. Initially, the convergence rate is fast because the high frequency error components are quickly filtered out. However, once the high-frequency error components are filtered out and only the low-frequency (or smooth) error components are left, the convergence rate becomes very slow.

The basic idea behind the Multigrid method is to take advantage of the fact that low-frequency error components of a fine grid becomes high-frequency error components in a coarser grid [1]. Thus, the strategy is to move down to a coarser grid once the convergence rate at the current grid saturates. We can think of this as a low-pass filter whose cutoff frequency can vary. That is, once the high-frequency components are filtered out, the cutoff frequency can be further moved down so that the error components which could not be filtered out in the previous setting can be filtered. Thus, fast convergence rate can be sustained by moving through different grid levels.

The basic Multigrid scheme forms a V-cycle in which the downward path computes the residual error while the upward path is the correction path which

updates the old estimation with a new approximation. The algorithm of the V-cycle in a recursive form is as follows [1] :

- $\mathbf{A}^h$  is a coefficient matrix at grid level  $h$ .

- $\mathbf{f}^h$  is a vector of the values of  $f(x, y)$  at grid level  $h$ .

- $\mathbf{v}^h$  is a vector of the unknown variable approximations at grid level  $h$ .

- $I_h^{2h}$  is an interpolation function mapping from a fine grid to a coarse grid. Also called, *restriction*.

- $I_{2h}^h$  is an interpolation function mapping from a coarse grid to a fine grid.

Algorithm  $MV : \mathbf{v}^h \leftarrow MV^h(\mathbf{v}^h, \mathbf{f}^h)$

1. Relax  $\nu_1$  times on  $\mathbf{A}^h \mathbf{v}^h = \mathbf{f}^h$  with initial guess  $\mathbf{v}^h$ .

2. If  $\Omega^h$  is  $\Omega^H$  (coarsest grid) then go to 4.

Else  $\mathbf{f}^{2h} \leftarrow I_h^{2h}(\mathbf{f}^h - \mathbf{A}^h \mathbf{v}^h)$

$\mathbf{v}^{2h} \leftarrow 0$  (zero as initial guess, for error)

$\mathbf{v}^{2h} \leftarrow MV^{2h}(\mathbf{v}^{2h}, \mathbf{f}^{2h})$

End if

3. Correct  $\mathbf{v}^h \leftarrow \mathbf{v}^h + I_{2h}^h \mathbf{v}^{2h}$ .

4. Relax  $\nu_2$  times on  $\mathbf{A}^h \mathbf{v}^h = \mathbf{f}^h$  with  $\mathbf{v}^h$  as initial guess.

A more efficient multigrid scheme called the *full multigrid* (FMV) computes the initial guess on the finest level by performing the V-cycle at every grid level using the corrected value of  $v$  at the coarser level as the new initial guess. Its algorithm in a recursive form is as follows [1] :

Algorithm  $FMV : \mathbf{v}^h \leftarrow FMV^h(\mathbf{v}^h, \mathbf{f}^h)$

1. If  $\Omega^h$  is  $\Omega^H$  then go to 3.

Else  $\mathbf{f}^{2h} \leftarrow I_h^{2h}(\mathbf{f}^h - \mathbf{A}^h \mathbf{v}^h)$

$\mathbf{v}^{2h} \leftarrow 0$

$\mathbf{v}^{2h} \leftarrow FMV^{2h}(\mathbf{v}^{2h}, \mathbf{f}^{2h})$

End if

2. Correct  $\mathbf{v}^h \leftarrow \mathbf{v}^h + I_{2h}^h \mathbf{v}^{2h}$ .

3.  $\mathbf{v}^h \leftarrow MV^h(\mathbf{v}^h, \mathbf{f}^h)$   $\nu_0$  times.

### 3 Implementation

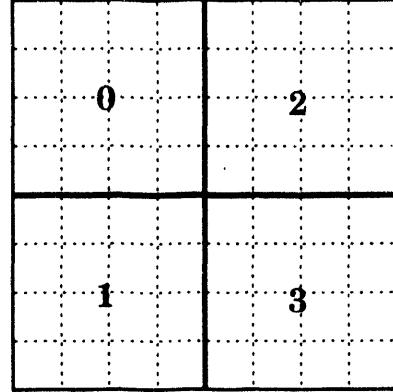

In the experiment, a full multigrid algorithm is implemented. As shown in Figure 3 (b), this method

```

function MultiV (N,n1,n2:integer; V,F : TwoDim returns TwoDim)

let

NewGrid := Relax(N,n1,V,F);

UpdateGrid := if N = 2 then

Relax(N,1,NewGrid,F)

else

let

Residue := ComputeRes(N,F,NewGrid);

CoarseF := Restrict(N/2,Residue);

CoarseErrorG := MultiV(N/2,n1,n2,InitVal(N/2),CoarseF);

ErrorGrid := Interp(N,CoarseErrorG);

CorrectedV := Correction(N,NewGrid,ErrorGrid)

in

Relax(N,n2,CorrectedV,F)

end let

end if

in

UpdatedGrid

end let

end function

```

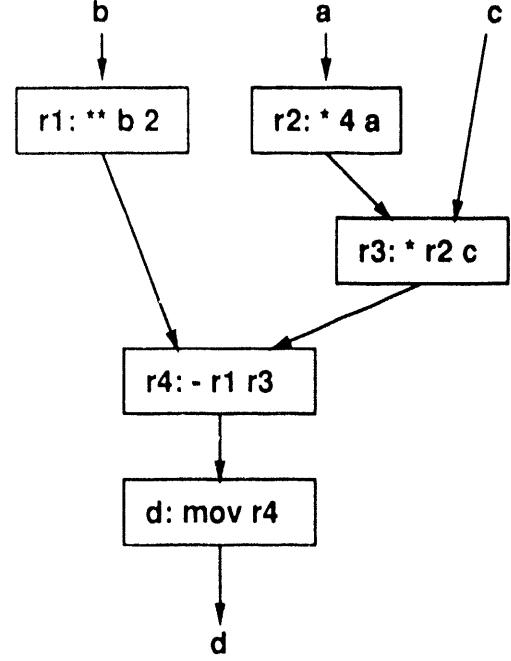

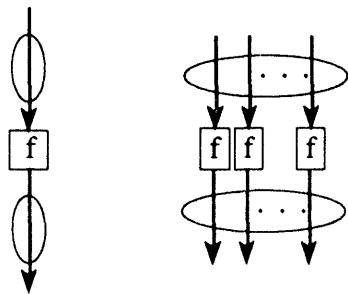

Figure 4: The function **MultiV** is a SISAL implementation of a recursive algorithm which performs a V-cycle.

starts out at the coarsest grid in which each grid points are computed to exact values. These grid points are then interpolated to the next finer grid. Then a V-cycle is performed on these interpolated grid points. This is repeated at every grid level until the finest grid level is reached. On the finest level the  $MV$  algorithm is performed  $\nu_0$  times. This section describes the SISAL implementation of the algorithm and various functions performed as part of the multigrid operations.

The function **MultiV** shown in Figure 4 is a SISAL implementation that performs a V-cycle. The function is written in a recursive style and closely resembles the Algorithm  $MV$  description. It has five input parameters and one output parameter which is a two dimensional array. The data type **TwoDim** is a user defined data type which is really a two dimensional array of double precision floating point numbers. The first three input parameters **N**, **n1**, **n2** of type **integer** are the grid size, the number of relaxations in the downward V-cycle, and the number of relaxations in the upward V-cycle, respectively. Among the two input parameters of type **TwoDim**, **V** is the current approximation of  $\mathbf{u}$  and **F** is  $\mathbf{f}$  in the equation  $\mathbf{A}\mathbf{u} = \mathbf{f}$ . In the current implementation of the multigrid method, the coarsest grid is when the grid is 2 by 2, i.e., when the number of unknowns become one. At this time, the value of the unknown can be computed to the exact value.

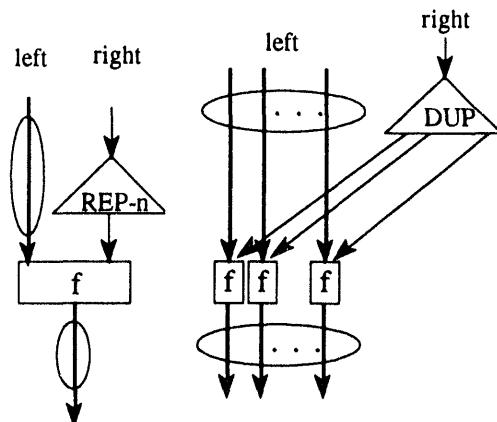

The function **MultiV** is called by the function **FMV** which performs the FMV-cycle. In FMV-cycle, computation starts from the coarsest grid level and moves up one level at a time. At each higher (finer) grid level, a V-cycle is performed (Figure 3 (b)). Figure 5 is a SISAL implementation of the function **FMV**. This

```

function FMV (N,n1,n2:integer; V,F:TwoDim returns TwoDim)

let

Grid := if N = 2 then

ExactSolve(F)

else

let

Residue := ComputeRes(N,F,V);

CoarseF := Restrict(N/2,Residue);

CoarseUpdatedV := FMV(N/2,n1,n2,BndVal(N/2),CoarseF);

UpdateV := InterP(N,CoarseUpdatedV);

CorrectedV := Correction(N,V,UpdateV)

in

MultiV(N,n1,n2,CorrectedV,F)

end let

end if

in

Grid

end let

end function

```

Figure 5: The function **FMV** is a SISAL implementation of a recursive algorithm which performs a FMV-cycle.

function is also written in a recursive style and closely resembles the Algorithm *FMV* description in the previous section.

The functions **MultiV** and **FMV** call the following five functions. These are the core functions of the multigrid algorithm. A short description of each function is as follows :

**Relax** : One of the iterative methods such as Jacobi, Gauss-Seidel, etc. This function is discussed in more detail in subsequent paragraphs.

**ComputeRes** : This function computes *residual r*, i.e.  $r = f - Av$ . This function contains (two-level) nested forall loops only.

**Restrict** : This function performs an interpolation from a grid of size  $N$  to  $N/2$ . It is used in the downward path of the V-cycle and contains nested forall loops.

**InterP** : This function performs an interpolation from a coarse grid of size  $N/2$  to a fine grid of size  $N$ . This function also contains only forall loops.

**Correction** : This function modifies the previously approximated unknown variables by adding the correction values. This function contains forall loops.

Two points were considered in deciding the kind of iterative method to be used for relaxation. The first consideration is the convergence rate. As discussed previously, SOR performs the best if  $\omega_{opt}$  can be determined. Since this value cannot be determined in general, the next best choice is the Gauss-Seidel iteration. The second consideration is the amount of

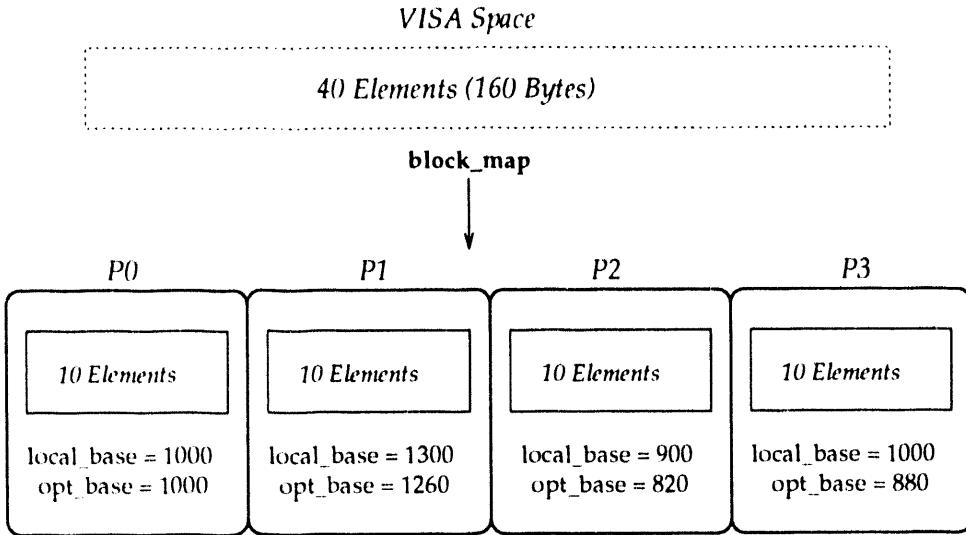

Figure 6: The Red-Black Gauss-Seidel is a parallel version of the otherwise sequential Gauss-Seidel iterative method. Notice the way the red and the black grid points are divided. The cross-like regions represent the 5-point stencil used in the approximation.

parallelism available in the algorithm. In this respect, Jacobi method has the most parallelism. In Jacobi iteration, a new approximation of a grid point is only a function of grid points from previous approximations. Therefore, all grid points can be updated in parallel. In Gauss-Seidel method, on the other hand, a new approximation of a grid point depends partly on the most recently approximated grid points. Due to this data dependency in the algorithm, Gauss-Seidel method is inherently sequential.

Fortunately, a parallel version of the Gauss-Seidel method exists. It is called the *Red-Black* (R-B) Gauss-Seidel method [9] and is shown in Figure 6. This method is not fully parallel as the Jacobi method. Instead, grid points are updated in two sequential steps. That is, one half of the grid points are updated first and then the other half are updated next. At each step, however, grid points can be updated in parallel. Although the amount of parallelism available in the Red-Black Gauss-Seidel method is only half that of the Jacobi method, its superior convergence rate (twice faster than Jacobi) makes it a better iterative scheme.

## 4 Experimental Results

In this section, we first discuss the programmability issue. We then describe the performance of the implemented program. First, the amount of parallelism existing in the SISAL implementation of a multigrid

| Solvers                 | Develop. Time (days) |

|-------------------------|----------------------|

| Basic iterative methods | 29                   |

| Multigrid               | 23                   |

| Precond. Conj. Gradient | 21                   |

| Domain Decomposition    | 30                   |

Table 1: Time spent to learn and implement each PDE solvers presented in the course.

algorithm is analyzed. Then we present the actual performance of the program on a number of different parallel machines.

#### 4.1 Programmability

Table 1 shows the development time of every PDE solver implemented during the course. The development time shown in the second column of the table includes the class lectures explaining the algorithms as well as the days spent in actual program development. On the average, half of the time was devoted to the discussion of the algorithm and the other half to the actual implementation. Although the first assignment consists of simple programs, additional time was needed to become familiar with writing SISAL programs.

In the case of the multigrid PDE solver, the SISAL implementation consists of approximately 350 source lines consisting of 17 functions. Two functions (**MultiV** and **FMV**) are written in a recursive style. There are 25 loops in the program in which three loops are written in a sequential loop construct and 22 loops are written in a parallel loop construct. Approximately two weeks (six lectures) were spent in discussing the algorithm and one week was spent in actual program development.

Once a working program is written, that same program was used for performance measurements on various parallel machines without any modifications. Therefore, on the average, a parallel PDE solver is written in two weeks which runs on various parallel machines in addition to average single processor workstations.

#### 4.2 Performance

This section first discusses the amount of parallelism available in the SISAL implementation of the multigrid algorithm. Then actual performance measured by executing the program on different parallel machines is presented.

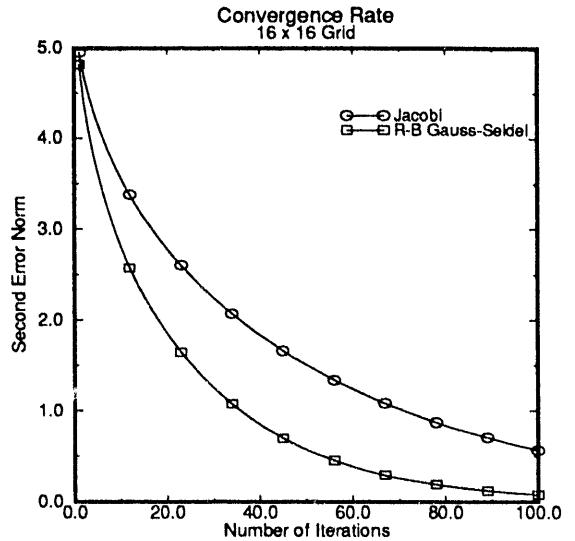

Figure 7: Red-Black Gauss-Seidel iteration has a superior convergence rate over that of the Jacobi iteration.

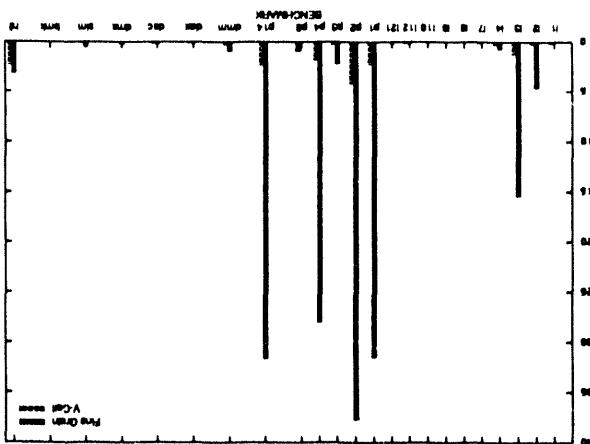

##### 4.2.1 Parallelism Profile of the Multigrid Implementation

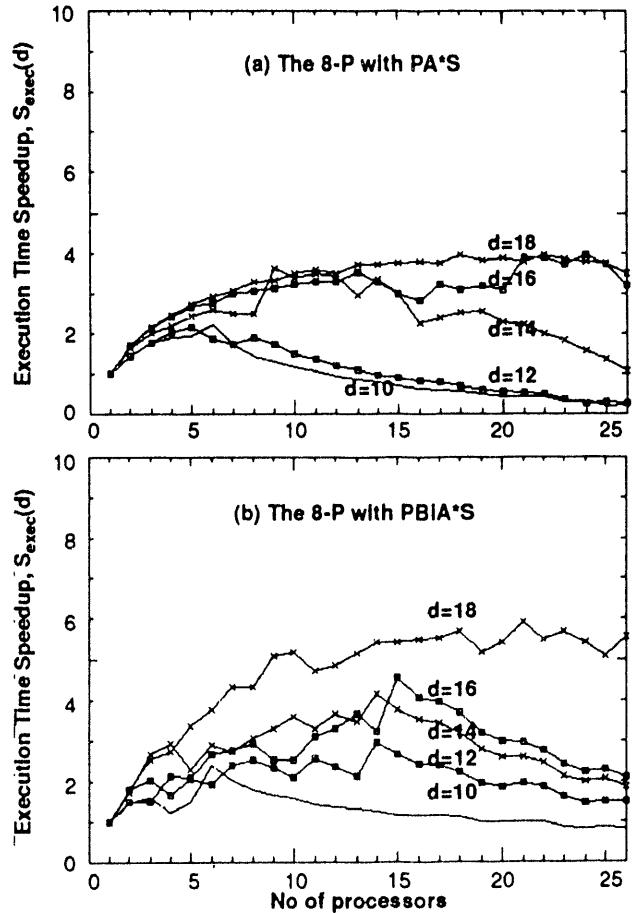

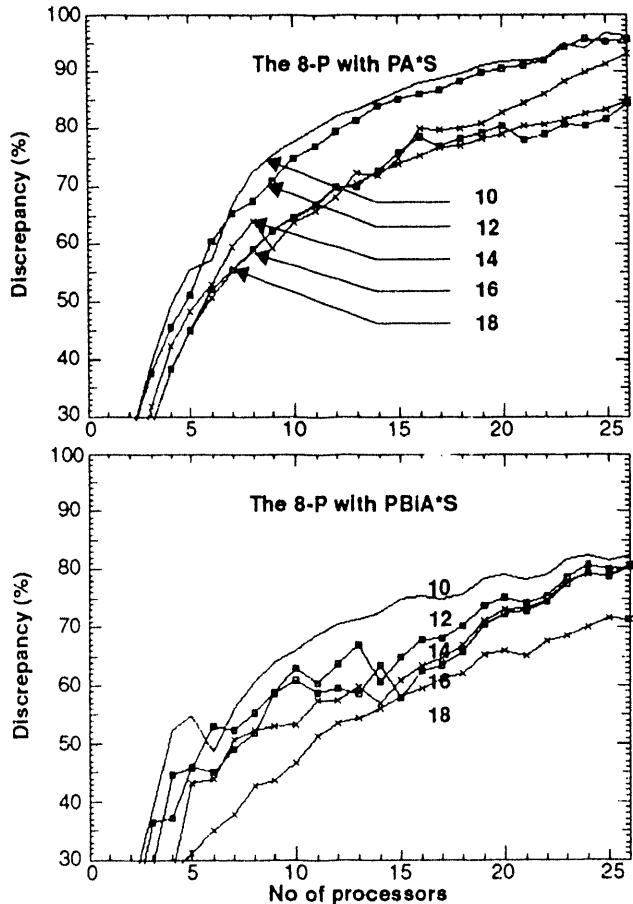

For performance measurements, an implementation of a full multigrid algorithm is used. In the program, the diffusion function of  $k(x, y) = e^{(x+y)}$  is used. Throughout the measurements, the number of relaxations  $\nu_1$  in the downward path of the V-cycle is set to two and the number of relaxations  $\nu_2$  in the upward path of the V-cycle is set to one.

The most expensive operation in each grid level is the relaxation operation. As mentioned in the previous section, the Red-Black Gauss-Seidel relaxation scheme is used. This scheme has a superior convergence rate over that of the Jacobi relaxation while still providing parallelism. Figure 7 shows the convergence rate of the two schemes for a two dimensional grid of 16 by 16. The initial guess for the unknowns were set to zero for both schemes. Table 2 shows the execution time of the two iterations on a Silicon Graphics four processor machine. It shows that both schemes have a close to linear speedups indicating that both schemes contain enough parallelism. Note that the execution time per iteration of the Jacobi iteration is slightly faster. This is due to the fact that the Red-Black Gauss-Seidel iteration updates grid points in a two-step sequence while the Jacobi iteration does it in a single step.

The relaxation operation along with other operations such as interpolation, restriction, residue calculation and error correction is performed at every grid

| 512 x 512, 10 iterations |                 |         |                  |                 |         |

|--------------------------|-----------------|---------|------------------|-----------------|---------|

| Jacobi                   |                 |         | R-B Gauss-Seidel |                 |         |

| PE                       | Exec. Time(sec) | Speedup | PE               | Exec. time(sec) | Speedup |

| 1                        | 202.80          | 1       | 1                | 223.13          | 1       |

| 2                        | 103.19          | 1.97    | 2                | 113.54          | 1.97    |

| 3                        | 69.24           | 2.93    | 3                | 76.33           | 2.92    |

| 4                        | 52.01           | 3.90    | 4                | 57.54           | 3.88    |

Table 2: Both the Jacobi and the Red-Black Gauss-Seidel iterations contain enough parallelism to provide close to linear speedups.

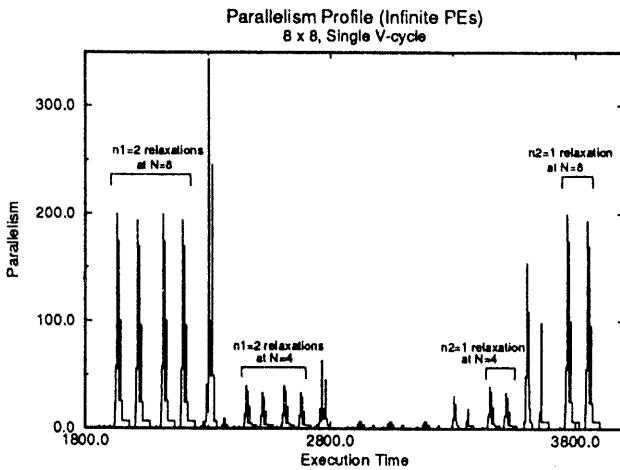

Figure 8: The ideal parallelism profile of a single V-cycle where the grid size is 8 by 8.  $\nu_1 = 2$  and  $\nu_2 = 1$ . (See Algorithm *MV*)

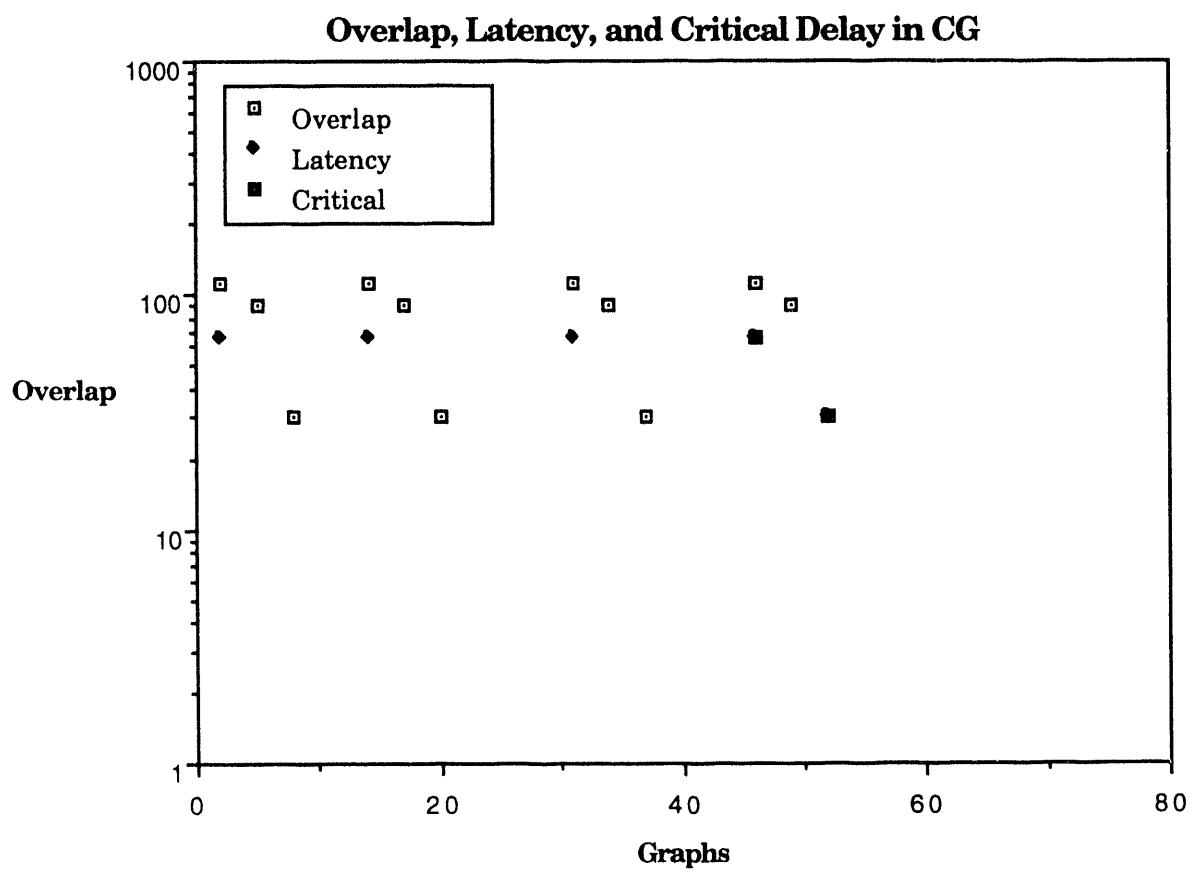

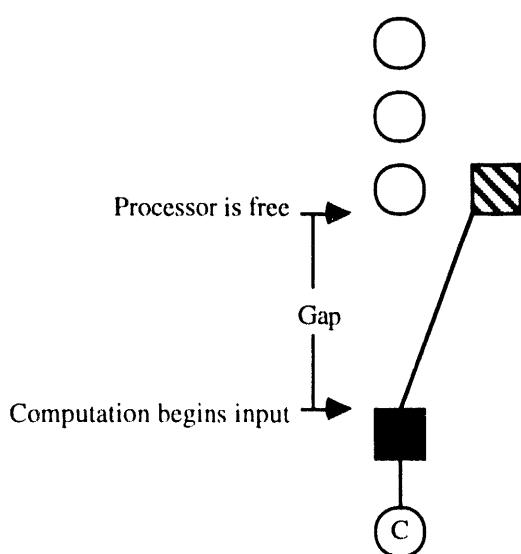

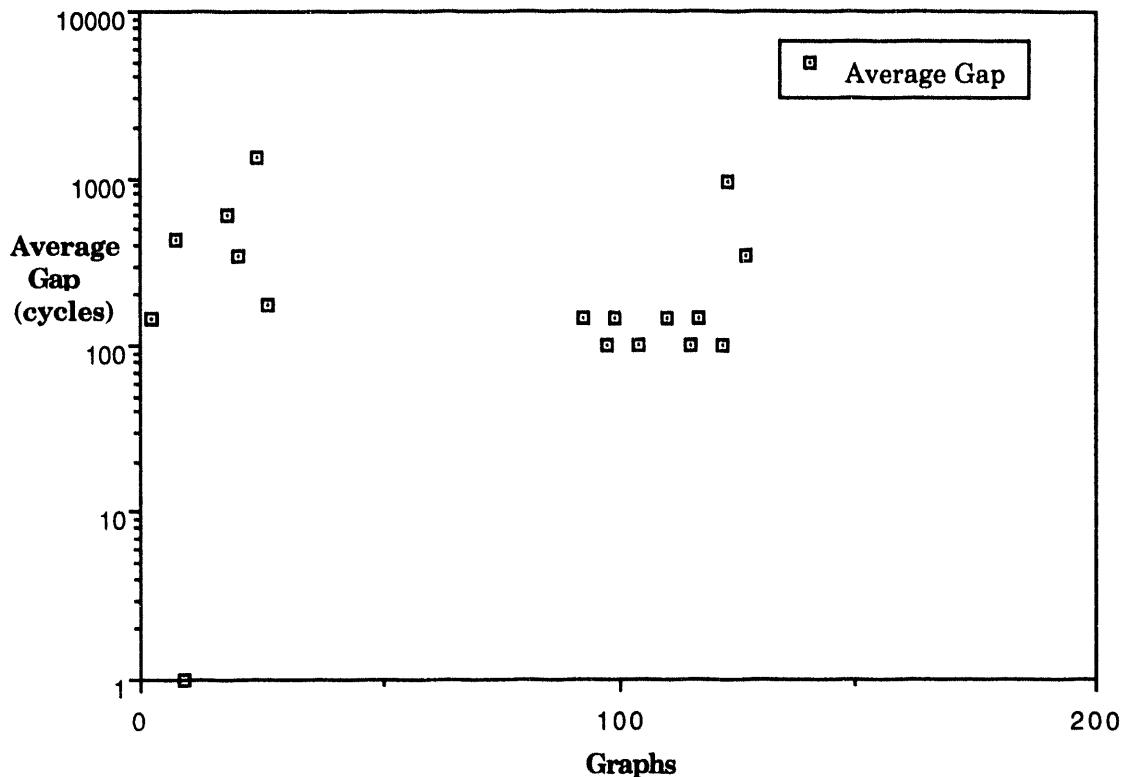

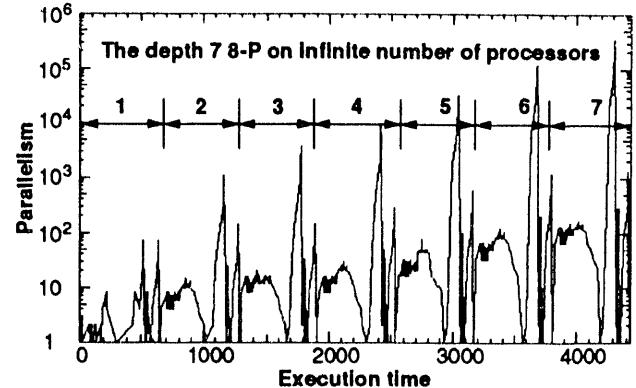

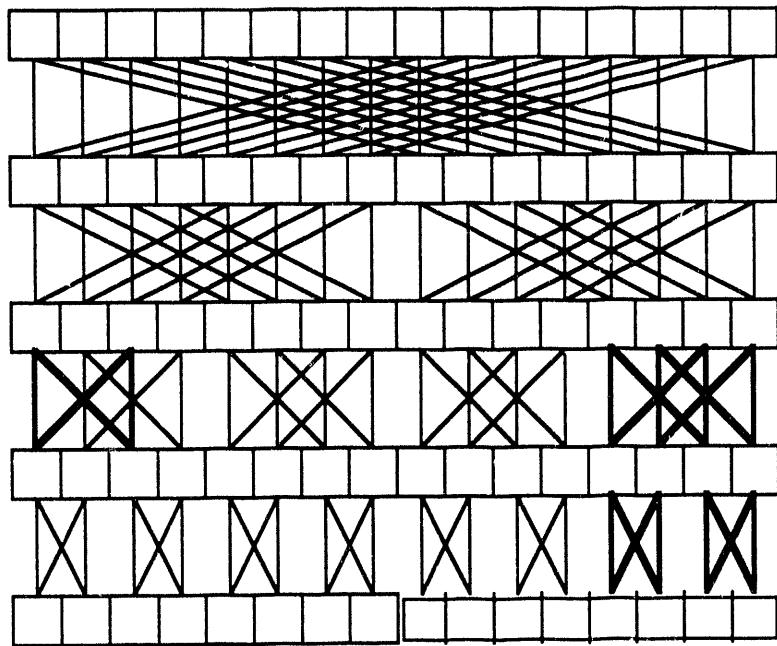

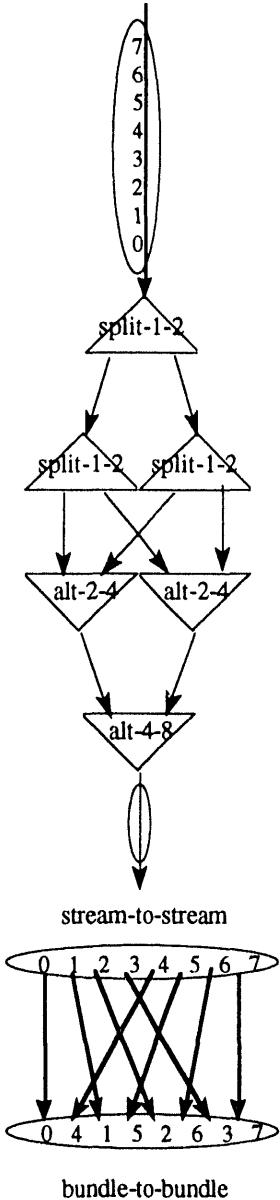

level. Althouth there can be many variations of moving around different grid levels, they are all based on the V-cycle. Figure 8 shows the parallelism profile of the V-cycle for an 8 by 8 grid using the Red-Black Gauss-Seidel iteration as the relaxation scheme. The 2 by 2 grid is the coarsest grid in the V-cycle. The parallelism profile shown is for an ideal case which assumes infinite number of processors and no communication overhead.

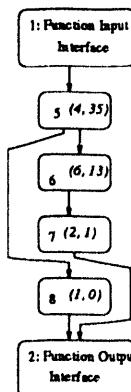

The amount of parallelism is computed by counting the number of executable nodes at each time interval. The nodes are part of the intermediate-level representation of the program which is a directed acyclic graph called Intermediate Form 1 (IF1) [11]. The nodes represent instructions and the edges connecting the nodes represent data dependency relationships among the nodes. The reason that the parallelism profile looks

like a cluster of impulses is because it is assumed that infinite number of processors is available. That is, all instructions that become executable are assumed to be executed together at the same time. The parallelism profile shows that parallelism decreases by one fourth until the grid size of 2 by 2 is reached and increases back to the original level. The reason the profile is not exactly symmetric is because the relaxation is performed twice going down the grid level ( $\nu_1 = 2$ ), but only once coming up the grid level ( $\nu_2 = 1$ ). Note that a single relaxation produces two spikes because in Red-Black Gauss-Seidel iteration, grid points are updated in two sequential steps.

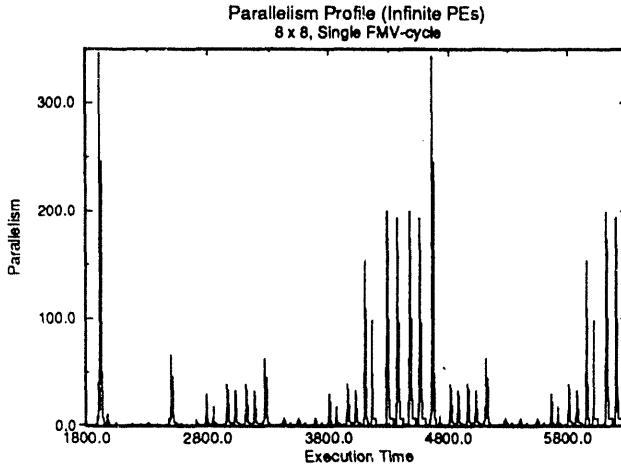

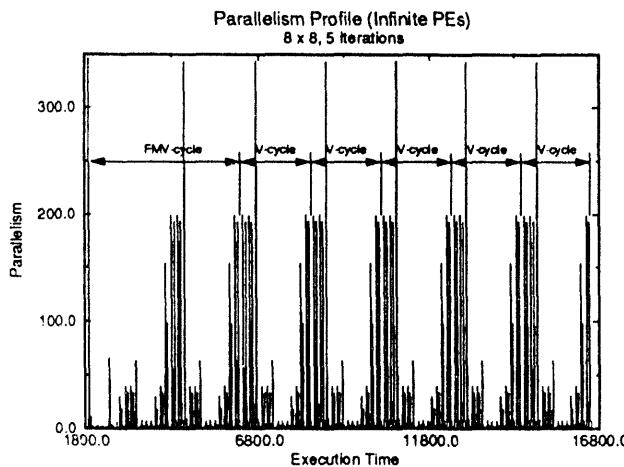

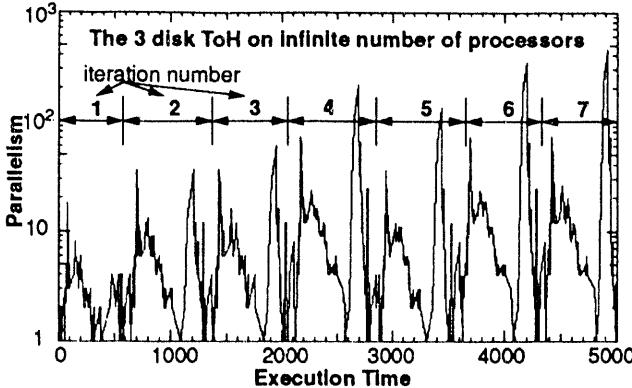

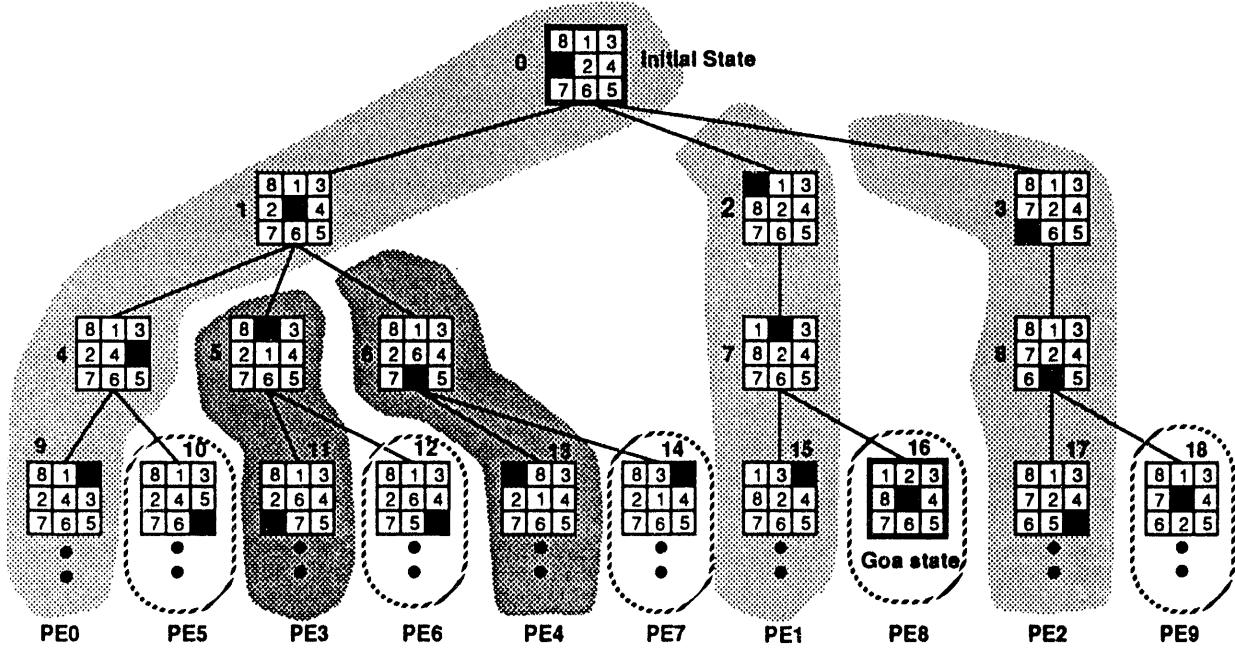

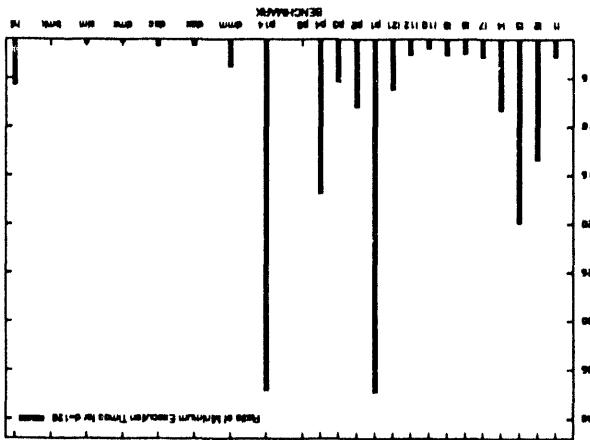

In the current multigrid implementation, a full multigrid V-cycle (FMV-cycle) is used once in the initialization stage followed by regular V-cycles in which the number of repetitions is specified by an input parameter. An FMV-cycle starts from the coarsest grid and moves up to the finest grid. At each grid level, a V-cycle is performed. The parallelism profiles for an FMV-cycle is shown in Figure 9 for infinite processors. As expected, we see repeated V-cycle profiles of different sizes. The rightmost pattern is the V-cycle parallelism profile for an 8 by 8 grid. At far left, parallelism profile for a 2 by 2 grid can barely be seen.

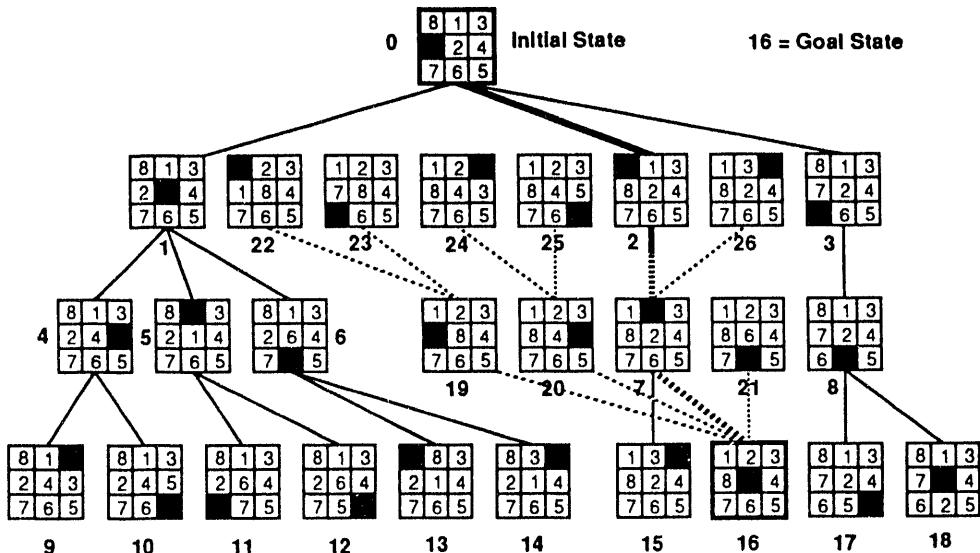

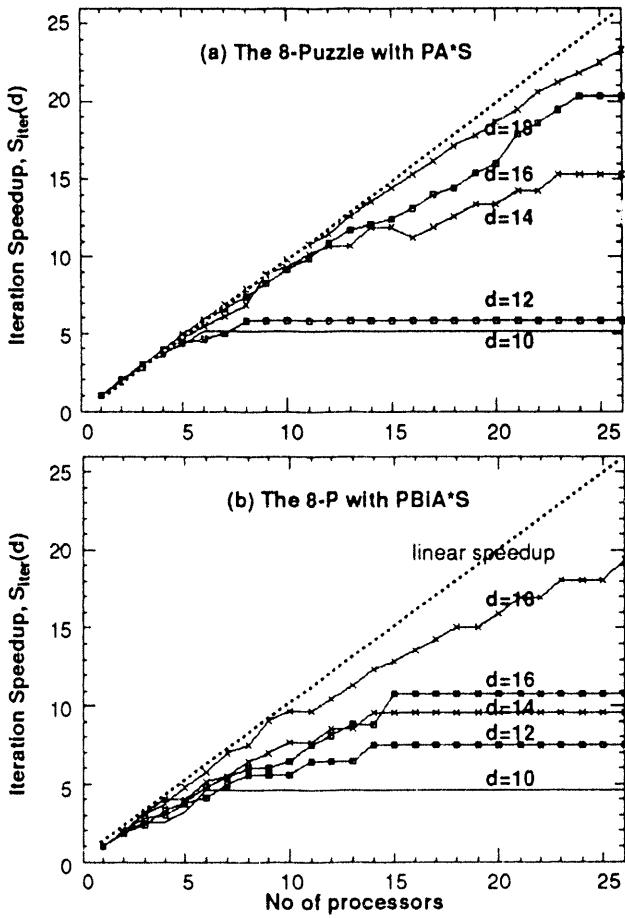

Figure 13 shows the parallelism profile of the full multigrid scheme doing 5 iterations. As mentioned already, the first iteration is the FMV-cycle, and the next 5 iterations are the V-cycles.

#### 4.2.2 Actual Performance on Parallel Machines

Performance of the multigrid implementation is measured on three MIMD type parallel computers. They are,

- CRAY Y-MP (4 PEs)

- Silicon Graphics (4 PEs)

- Sequent Balance (16 PEs)

Figure 9: The ideal parallelism profile of a single FMV-cycle where the grid size is 8 by 8.  $\nu_1 = 2$  and  $\nu_2 = 1$ . (See Algorithm *FMV*)

Figure 10: The ideal parallelism profile of a full multigrid scheme doing 5 iterations. The grid size is 8 by 8.  $\nu_1 = 2$  and  $\nu_2 = 1$ .

| 512 x 512, 5 iterations |             |            |

|-------------------------|-------------|------------|

| PE                      | CRAY (sec.) | SGI (sec.) |

| 1                       | 15.89       | 457.78     |

| 2                       | 8.76        | 287.14     |

| 3                       | 6.39        | 192.69     |

| 4                       | 5.34        | 146.00     |

Table 3: Execution time of a multigrid program on a CRAY Y-MP and a Silicon Graphics machines.

| 256 x 256, 5 iterations |                |

|-------------------------|----------------|

| PE                      | Balance (sec.) |

| 1                       | 3989.20        |

| 2                       | 1993.17        |

| 4                       | 1014.61        |

| 8                       | 516.11         |

| 12                      | 362.29         |

| 16                      | 274.89         |

Table 4: Execution time of a multigrid program on a Sequent Balance Machine.

CRAY Y-MP runs UNICOS which is a Unix-like operating system and has vector execution units in each processor. The Silicon Graphics machine is also a Unix-based and is built on MIPS R3000 processor chips. Sequent Balance utilizes National Semiconductor's NS32032 processor chip and is a slow machine by today's standard.

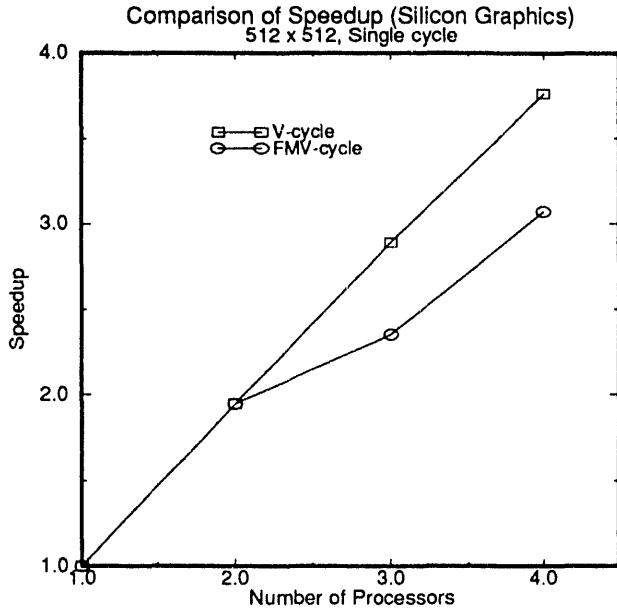

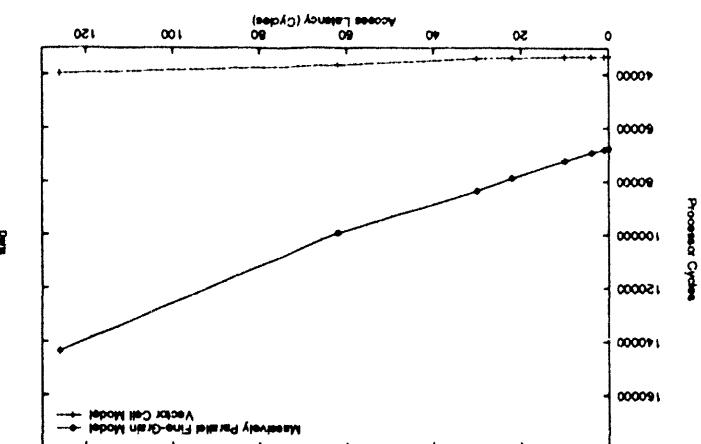

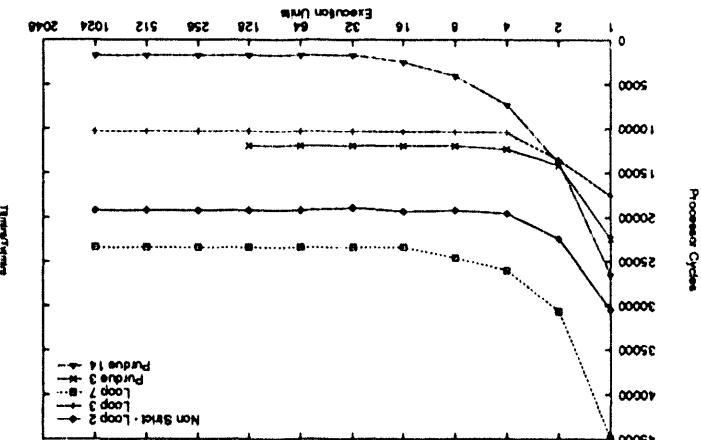

In the performance measurement, a grid size of 512 by 512 is used and each run consists of 5 iterations. Note that by 5 iterations we actually mean one FMV-cycle followed by five V-cycles. Since the full multigrid scheme utilizes a FMV-cycle with V-cycles, it is helpful to measure the speedup of these two cycles separately before measuring the speedup of the whole program. Figure 11 shows a graph which compares the speedup of one FMV-cycle and one V-cycle. It shows that V-cycle results in a better speedup. This is expected since FMV-cycle spends some time performing V-cycles at coarser grids. This results in less processor utilization and thus produces lower speedup. The graph shows that V-cycle results in a close to linear speedup.

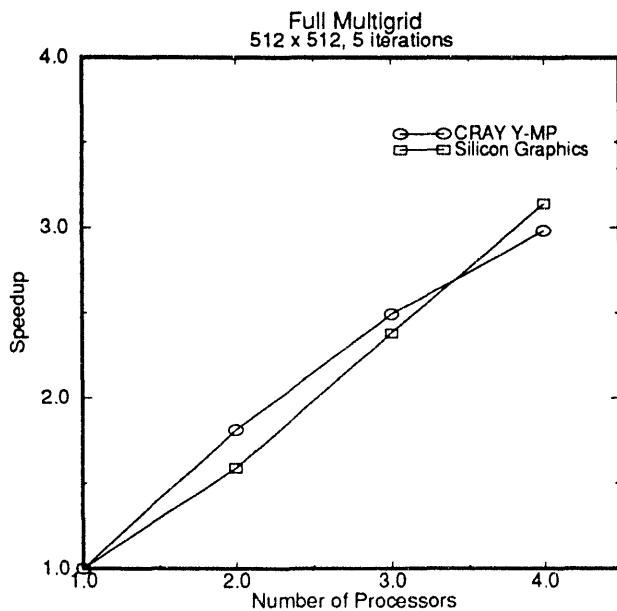

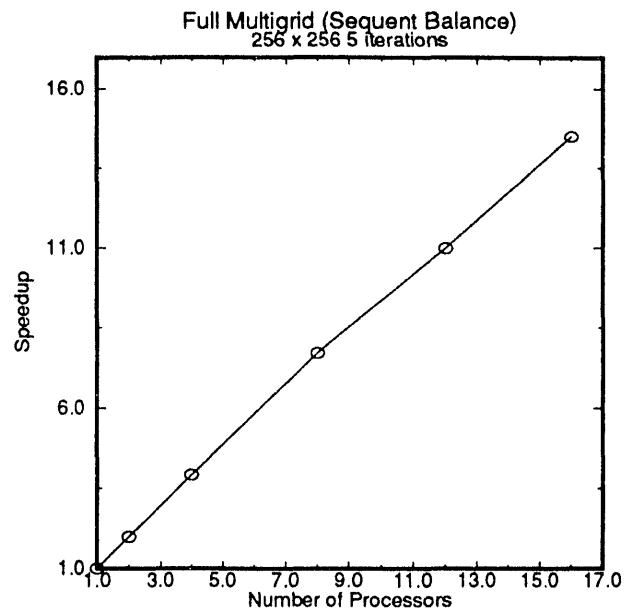

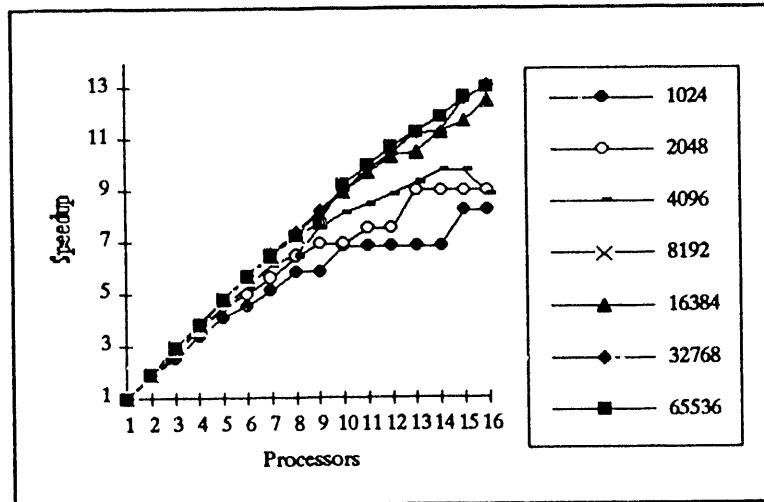

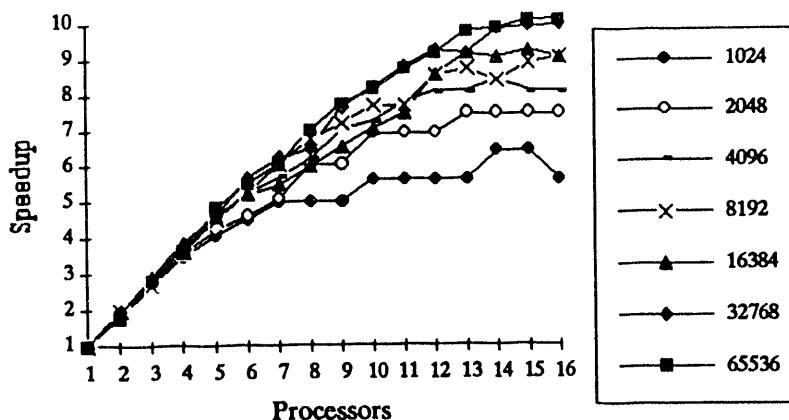

From Figure 11, we expect the speedup of the multigrid implementation to be somewhere between the speedup reached by the FMV-cycle and the V-cycle. Figure 12 shows the speedup of the multigrid implementation on CRAY Y-MP and Silicon Graphics machines. Figure 13 shows the speedup on a Sequent Balance. Tables 3 and 4 show the execution times.

Figure 11: Speedup comparison of a single FMV-cycle and a single V-cycle: 512 by 512 grid.

Figure 12: Speedup of a full multigrid implementation on a 512 by 512 grid.

Figure 13: Speedup of a full multigrid implementation on a 256 by 256 grid.

We see that the OSC compiler does a good job of concurrentization by observing the speedup curve of each machine. In addition to concurrentization, CRAY also utilizes hardware vector facilities. The OSC recommends innermost parallel loops for vectorization. In the multigrid implementation used in the performance measurements, the OSC recommended vectorization of 12 loops in which all were vectorized by the native C compiler. A parallel loop in function `Norm` which has reduction operations (`sum` and `greatest`) in the return clause were neither recommended by the OSC nor vectorized by the CRAY C compiler.

## 5 Conclusion

We have shown that functional programming is indeed a viable approach to parallel computing providing both programmability and performance. Our program which has originally been written for a sequential machine efficiently executed on a number of parallel machines without requiring the programmer to manually parallelize the code. The implicit parallelism of SISAL, therefore, has allowed the programmer to concentrate on the implementation of the algorithm without having to worry about low-level execution details. Once a program is verified to work correctly on a sequential machine, it can be run on various parallel machines without program modification.

However, the current version of OSC is tailored for execution on a *shared global address space* machines which currently employ a relatively small number of processors (< 30). On the other hand, there is a growing number of parallel machines already introduced or being introduced which employ a large number of processors (in the hundreds). Logically, some machines have shared global address space and some do not. Physically, however, all large machines have distributed memory spread across the processors making memory accesses nonuniform and latency a serious issue to consider. To achieve good performance on such machines, a new execution model needs to be developed for the next generation of the SISAL compiler.

## Acknowledgements

We would like to thank our colleagues, especially Dr. John Feo at the Computing Research Group of the Lawrence Livermore National Laboratory for letting us use the CRAY and the Silicon Graphics parallel machines. We also thank Professor Walid Najjar of Colorado State University for letting us use the Sequent Balance machine.

## References

- [1] W. Briggs. *A Multigrid Tutorial*. SIAM, 1987.

- [2] D. Cann. *Compilation Techniques for High Performance Applicative Computation*. PhD thesis, Colorado State University, 1989.

- [3] D. Cann. *The Optimizing SISAL Compiler: Version 12.0*. Lawrence Livermore National Laboratory, P.O. Box 808, Livermore, CA 94550, 1992.

- [4] D. Cann. Retire Fortran: A debate rekindled. *Communications of the ACM*, 35(8):81-89, August 1992.

- [5] J. Feo, D. Cann, and R. Oldehoeft. A report on the Sisal language project. *Journal of Parallel and Distributed Computing*, 10:349-366, December 1990.

- [6] G. Golub and C. van Loan. *Matrix Computations*. Johns Hopkins University Press, 1989.

- [7] M. Kallstrom and S. Thakkar. Programming three parallel computers. *IEEE Software*, pages 11-22, January 1988.

- [8] J. McGraw, S. Skedzielewski, S. Allan, R. Oldehoeft, J. Glauert, C. Kirkham, B. Noyce, and R. Thomas. *SISAL Language Reference Manual Version 1.2*, March 1985.

- [9] J. Ortega. *Introduction to Parallel and Vector Solution of Linear Systems*. Frontiers of Computer Science. Plenum Press, 1988.

- [10] A. Osterhaug. *Guide to Parallel Programming on Sequent Computer Systems*. Sequent Computer Systems, Inc., second edition, 1987.

- [11] S. Skedzielewski and J. Glauert. *IF1 An Intermediate Form for Applicative Languages*. Computing Research Group, Lawrence Livermore National Laboratory, P.O. Box 808, L-306, Livermore, CA 94550, 1985.

# Implementing the Kernel of the Australian Region Weather Prediction Model in SISAL

G.K. Egan

Laboratory for Concurrent Computing Systems

Swinburne University of Technology

John Street, Hawthorn 3122, Australia

## Abstract

*The SISAL implicit parallel programming language has been implemented on a number of platforms ranging from scientific workstations through medium cost multiprocessors to high end parallel super computers and recently massively parallel processors. No changes to source code are required to obtain good performance across these platforms and it has been claimed that SISAL exhibits similar uniprocessor performance to FORTRAN while providing significant speedup compared to FORTRAN on multiprocessors.*

*The Australian Region Weather Prediction Model is an experimental FORTRAN code which uses a variable resolution nesting scheme to provide higher resolution predictions over important areas of the Australian continent such as cities and coastal fisheries. In this preliminary study we explore the performance of the SISAL implicit parallel programming language on a significant scientific application by recoding the kernel subroutine of the Model in SISAL. Results are presented for a low end SPARC workstation, an entry level Cray Y-MP EL and a high end Cray C90.*

## 1 Introduction

The Australian Region Weather Prediction Model (ARPE) was developed by the Australian Bureau of Meteorology Research Centre [1] for short-term weather forecasting up to 36 hours. ARPE draws upon the work of Arakawa, Lamb and Miyakoda [2][3] for its formulation and is intended to be a production code for the prediction of weather over the Australian region. This paper will concentrate on the implementation of the core subroutine of the ARPE in the SISAL language and readers are directed to reference [1] for a detailed description of the model. The work is part of a continuing long term international study of SISAL

being conducted in collaboration with the Lawrence Livermore National Laboratory.

## 2 The SISAL language

SISAL is a functional language for numerical computation [4]. The developers of SISAL have been able to demonstrate performance comparable with FORTRAN on a number of computing platforms including the Cray Research multiprocessors [5].

SISAL prohibits by design the ability to express constructions which lead to the side effects that make compilation for parallel computer systems extremely difficult. Examples of side effects include those which occur through the COMMON and EQUIVALENCE statements in FORTRAN and SISAL has neither of these constructs. SISAL is block structured and superficially resembles a number of modern languages. The single assignment nature of SISAL means variables have values assigned to them once. This requires some departure from a common style of programming where variables are re-used in programs sometimes for unrelated computations. Translation of FORTRAN programs into SISAL is not necessarily a simple process and can be complicated significantly if the program being re-expressed has been the subject of undisciplined maintenance or construction. This may be compounded if there is no original formulation of the mathematical model available. Direct transliteration of well written FORTRAN code can yield satisfactory results.

Most comparative studies to date have involved the complete recoding of an application in SISAL. In this study the mixed language facility of the current (V12.9.1) Optimising SISAL Compiler is used with an initial core subroutine being recoded.

### 3 The weather prediction model

The Weather Prediction Model code (ARPE) consists of some 10,000 lines of FORTRAN source code. Its pre-processors and ancillary code constitute perhaps another 5,000 lines of code. The code is generally well written with disciplined use of COMMON and EQUIVALENCE statements. The kernel routines make almost no use of subroutines although the structure of the code suggests they should be used. ARPE then is a reasonable example of a code where inlining has occurred from the outset in an attempt to obtain improved performance. It predates modern FORTRAN pre-processors which automatically inline selected subroutines.

### 4 FORTRAN

The Cray Research FORTRAN tool suite used [6] runs under X Windows and is a marked advance on those generally available only a few years ago. The tool set comprises: a profiler (flowview) which identifies key subroutines and subroutines which are candidates for inlining; a pre-processor which performs inlining and attempts to identify and annotate parallel regions; an assistant for explicit parallel annotation (atscope); and a parallelism estimator (atexpert).

| Routine Name | Tot Time | Calls | Avg Time | Percentage | Accum% |

|--------------|----------|-------|----------|------------|--------|

| INNER2       | 2.52E+01 | 9     | 2.80E+00 | 42.24      | 42.24  |

| LIE          | 1.09E+01 | 24    | 4.53E-01 | 18.23      | 60.47  |

| PHYS         | 6.15E+00 | 5     | 1.23E+00 | 10.31      | 70.79  |

| LIEBIG       | 5.61E+00 | 12    | 4.66E-01 | 9.42       | 80.21  |

| LIEH         | 5.50E+00 | 12    | 4.58E-01 | 9.23       | 89.44  |

| LIEBH        | 1.69E+00 | 9     | 1.88E-01 | 2.84       | 92.28  |

| SEMMIMP      | 1.48E+00 | 9     | 1.64E-01 | 2.16       | 94.76  |

| VMODES       | 1.08E+00 | 4     | 2.71E-01 | 1.82       | 96.57  |

| INNER        | 9.56E-01 | 9     | 1.06E-01 | 1.60       | 98.18  |

| DADADJ       | 4.40E-01 | 11470 | 3.64E-03 | 0.74       | 98.91  |

| LAMLL        | 1.43E-01 | 2600  | 5.50E-05 | 0.24       | 99.15  |

Table 1: Execution Profile (5 iterations Y-MP EL)

The original program was profiled using flowtrace to identify the core subroutines. For reasons already stated flowtrace did not identify any subroutines eligible for inlining.

The INNER2 subroutine was chosen as the starting point for this study but as it represents only 42% of the run time contribution no significant speedup is to be expected. The LIE and PHYS subroutines will be translated in due course. Our interest here is to confirm that the run time is not adversely affected and that underlying concurrency is uncovered by the OSC compiler.

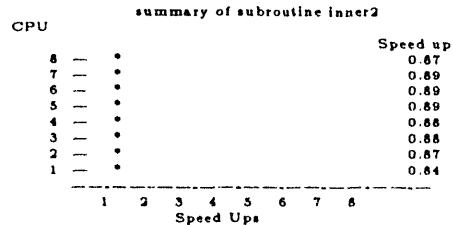

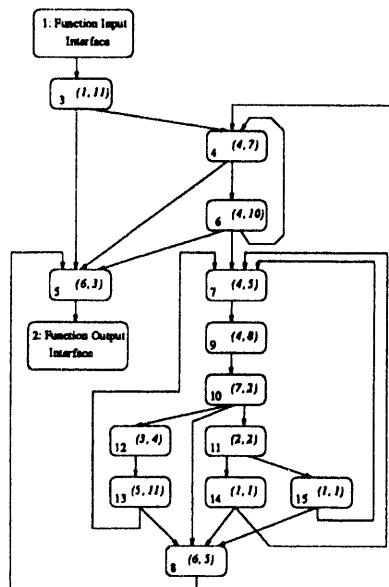

Figure 1: speedup of INNER2 predicted by atexpert

### 4.1 Results for FORTRAN

The automatic parallel annotator was used to annotate the INNER2 subroutine. No attempt was made to resolve data dependencies in the original FORTRAN in this part of the study although this is intended later. The atexpert measurement tool was used to examine individual DO loops for predicted speedup. Atexpert is claimed to accurately predict performance for dedicated systems. The tool provides parallelism profiles and allows routines associated with parallel or sequential regions to be examined and analysed interactively.

It can be seen in Figure 1 that fpp failed to discover significant parallel regions in INNER2.

## 5 SISAL

### 5.1 Mixed language compilation

The osc compiler compiles and links modules written in FORTRAN and SISAL. In this FORTRAN is invoking a SISAL function. To do this the original INNER2 subroutine was replaced by a FORTRAN shell. The shell initialises the array descriptors required by SISAL and calls the replacement INNER2 written in SISAL [7].

Fortunately the array descriptors may be re-used for other arrays which have an identical shape. The ability to specify an offset for returned data structures could be used to avoid the often clumsy process of dealing with boundary values. The current descriptor mechanism unfortunately sets to zero the elements not written to.

### 5.2 The transliteration process

Although the mathematical formulation was available it did not provide significant assistance in the transliteration process. The INNER2 subroutine was

directly transliterated into SISAL with no restructuring being attempted. A number of unintentional out of bound accesses were discovered in the FORTRAN program during this transliteration.

The transliteration process was significantly complicated by the size of the INNER2 subroutine. While the SISAL debugger (sdbx) gave some assistance there were many cases where sdbx was not able to determine the original source line causing the error. Other minor difficulties which would cause irritation for programmers used to imperative styles also arose. In this case even though the author has a reasonable understanding of SISAL the passage of time since writing his previous SISAL program still led him to be caught by the following:

```

for initial

...

k:=0;

while k < kz repeat

k:= old k +1;

returns .....u[k].....

```

Most programmers will expect k to be 1 when the variable u is accessed on the first loop iteration rather than zero as stated by the for initial clause.

Transliteration and debugging took approximately 35 hours.

### 5.3 Results for SISAL

The results for one call of INNER2 in FORTRAN and SISAL are shown in Table 2. In their current form both versions are several hundred lines long and the interleaving of initialisation, the calculation of primary meteorological variables and common working variables makes their inner workings difficult to comprehend (Appendices).

| Language | SPARC   | EL (1-cpu) | C90 (1-cpu) | C90 (4-cpu) |

|----------|---------|------------|-------------|-------------|

| fortran  | 6.6+0.7 |            |             |             |

| c90 -Zp  |         | 3.01+0.48  | 0.39+0.01   |             |

| sisal -O | 7.2+1.0 | 6.57+0.25  | 1.04+0.01   | 0.29+0.01   |

Table 2: Run Times for FORTRAN and SISAL

It may be noted that although the run times on the SPARC workstation for FORTRAN and SISAL are comparable performance on the Cray systems is not as good. It is believed that the transliteration resulted in a SISAL style which caused difficulty for the SISAL optimisers; this is currently being resolved.

## 6 Conclusions

A modest amount of difficulty was encountered in the transliteration of the kernel INNER2 subroutine into SISAL. The run time for this first SISAL implementation relative to FORTRAN is acceptable. Good speedup has been achieved with the SISAL version's runtime falling below that for FORTRAN at four processors. Given this promising start the study will now refine the version of INNER2 and move to the other dominant kernel subroutines LIE and PHYS. The PHYS subroutine is dominated by conditionally executed code as are many other weather codes. It is anticipated that this will produce a more demanding test for SISAL.

## Acknowledgements

The author thanks the Australian Bureau of Meteorology Research Centre for access to the ARPE code. The author also thanks the members of the Laboratory for Concurrent Computing Systems for their contributions to the work presented in this paper.

## Appendices

### INNER2.F

The original code of INNER2 has been stripped out and replaced with descriptor initialisation and call to sinner2.

```

SUBROUTINE INNER2

C INNER2 CALCULATES THE RH SIDES OF THE MAIN SEMI-IMPLICIT EQUATIONS

C

C include 'arpe.inc'

C PARAMETER

C +

C + I2=I1+1, I3=I1+2, I4=I1+3, ILM=IL-1, ILN=IL-2

C + J2=J1+1, J3=J1+2, J4=J1+3, JLM=JL-1, JLN=JL-2

C + ,KZMI=KZ-1, KZP=KZ+1

C + ,CP=1.00464E7, G=980.6, HL=2.501E10, PBAR=1.E6, R=2.87E6

C + ,RV=4.61E+6

C

C COMMON

C + /DTDS/ DT,DS,DTI,DSI,DSI2,DSSQ,TDSI,HDTDS,BET65,DTMAX

C + ,/INTGR/ PRECP, PRECTA, CKS, EKE, PE, PS-BAR, TRIAT, VRONG

C + ,/KTAU/ KTAU

C

C COMMON

C + /CDIFF/ CDIFF(IL, JL)

C + ,/CORP/ CORP(IL, JL)

C + ,/DNORM/ DNORM(KZ)

C + ,/DQ/ DQ(KZ)

C + ,/DTODQ/ DTODQ(KZ)

C + ,/EM/ EM(IL, JL)

C + ,/EMSQ/ EMSQ(IL, JL)

C + ,/EMSQI/ EMSQI(IL, JL)

C + ,/GAMA/ GAMA(KZ)

C + ,/OMEGA/ OMEGA(KZ, IL, JL)

C + ,/PHI/ PHI(KZ, IL, JL)

C + ,/PS/ PSM(IL, JL), PS(IL, JL), PSP(IL, JL)

C + ,/Q/ Q(KZ)

C + ,/QPH/ QPH(KZ)

C COMMON

```

```

+   /RMM/   RMM(KZ,IL,JL), RM(KZ,IL,JL), RMP(KZ,IL,JL)

+   ./RTBAR/ RTBAR(KZ)

+   ./SIGDOT/ SIGDOT(KZ,IL,JL)

+   ./T/   TM(KZ,IL,JL), T(KZ,IL,JL), TP(KZ,IL,JL)

+   ./TBAR/ TBAR(KZ)

+   ./U/   UM(KZ,IL,JL), U(KZ,IL,JL), UP(KZ,IL,JL)

+   ./V/   VM(KZ,IL,JL), V(KZ,IL,JL), VP(KZ,IL,JL)

+   ./ZS/   ZS(IL,JL)

+

C

REAL Q

integer ik(100),ij(100),ikij(100)

DIMENSION RMPR(KZ,IL,JL)

DIMENSION TFLLEV(KZ),DTFDQ(KZ),WVEL(KZ)

DIMENSION VADVU(KZP1),VADVV(KZP1),VADVRM(KZP1)

DATA VADVU/KZP1*0./,VADVV/KZP1*0./,VADVRM/KZP1*0./

DATA OMG / 0.0 /

C

c SISAL array descriptors

c one dimension

ik(1)=0

ik(2)=0

ik(3)=0

c

ik(4)=1

ik(5)=ks

ik(6)=1

ik(7)=ks

ik(8)=1

c

c two dimensions

ij(1)=0

ij(2)=0

ij(3)=0

c

ij(4)=i1

ij(5)=il

ij(6)=il

ij(7)=il

ij(8)=1

c

ij(9)=j1

ij(10)=jl

ij(11)=jl

ij(12)=jl

ij(13)=1

c

c three dimensions

ikij(1)=0

ikij(2)=0

ikij(3)=0

c

ikij(4)=1

ikij(5)=ks

ikij(6)=1

ikij(7)=ks

ikij(8)=1

c

ikij(9)=i1

ikij(10)=il

ikij(11)=il

ikij(12)=il

ikij(13)=1

c

ikij(14)=j1

ikij(15)=jl

ikij(16)=jl

ikij(17)=jl

ikij(18)=1

c

call sinner2(

+dt,ds,dsi,dsi2,tdsi,dtmax,cks, eke, pe, psbar, trhat, vromg,

+ktau,

+cdiff,ijj,

+corp,ijj,

+dnorm,ik,

+dq,ik,

+dtdq,ik,

+em,ijj,

+emsq,ijj,

+emsq,ijj,

+gamma,ik,

+omega,ik,

+phi,ikij,

+psm,ijj,ps,ijj,

+q,ik,

+qph,ik,

+rmm,ikij,rm,ikij,rm,ikij,

+rtbar,ik,

+sigdot,ikij,

+tm,ikij,tk,ikij,tp,ikij,

+trbar,ik,

+um,ikij,u,ikij,up,ikij,

+vm,ikij,v,ikij,vp,ikij,

+zs,ijj,

returns

+rm,ikij,

+sigdot,ikij,

+up,ikij,

+new_tp,ikij,

+new_tm,ikij,

+vp,ikij,

+eke,

+cks,

+trhat,

```

```

+pe,

+psbar,

+vromg)

c

RETURN

END

```

## inner2.sis

```

define sinner2

% G.K. Egan 1993

type OneDReal = array[real];

type TwoDReal = array[OneDReal];

type ThreeDReal = array[TwoDReal];

global log(a:real returns real)

global sqrt(a:real returns real)

function boundary'cell(i,i1,il,j,j1,jl:integer returns boolean)

((i = i1) -- (i = il) -- (j = j1) -- (j = jl))

end function

function divergence'sums(

i,j,ks,il,j1,jl:integer; ds1:real;

dq:OneDReal; u,v,t:ThreeDReal; emsq:TwoDReal

returns

real, real, real, OneDReal, OneDReal,

OneDReal, OneDReal, OneDReal)

for initial

sumu:=0.0;

sumv:=0.0;

sumx:=0.0;

k:=1;

while (k < ks) repeat

k:=old k +1;

sumu, sumv, sumx := (

if boundary'cell(i,i1,il,j,j1,jl) then

old sumu, old sumv, old sumx

else

old sumu+dq[k]*(u[k,i+1,j]-u[k,i-1,j]

+v[k,i,j]+v[k,i+1,j]-v[k,i-1,j-1]),

old sumv+dq[k]*(u[k,i,j]+u[k,i,j+1]

-u[k,i-1,j]-u[k,i-1,j+1]+v[k,i,j+1]-v[k,i,j-1]),

old sumx+dq[k]*(u[k,i,j]-u[k,i-1,j]+v[k,i,j]-v[k,i,j-1])

end if)

returns

value of sumu

value of sumv

value of sumx

array of sumu

array of sumv

array of sumx

array of emsq[i,j]*sumx*ds1

array of t[k,i,j]

end for

end function

function sinner2(

dt,ds,dsi,dsi2,tdsi,dtmax,cks, eke, pe, psbar, trhat, vromg:real;

ktau:integer;

cdifft:TwoDReal;

corp:TwoDReal;

dnorm:OneDReal;

dq:OneDReal;

dtodq:OneDReal;

em:TwoDReal;

emsq:TwoDReal;

emsqi:TwoDReal;

gamma:OneDReal;

omega:OneDReal;

phi:ThreeDReal;

psm, ps:TwoDReal;

q:OneDReal;

qph:OneDReal;

rmm, rm, rmp:ThreeDReal;

rtbar:OneDReal;

tm, t, tp:ThreeDReal;

tbar:OneDReal;

um, u, up:ThreeDReal;

vm, v, vp:ThreeDReal;

xs:TwoDReal

returns

ThreeDReal,%new_im

ThreeDReal,%new'aidot

ThreeDReal,%new'up

ThreeDReal,%new'ip

ThreeDReal,%new'imp

ThreeDReal,%new'vp

real,%new'eke

real,%new'cks

real,%new'that

real,%new'pe

real,%new'psbar

real,%new'vromg

)

let

```

```

kx:=15;

li:=65;

jl:=40;

il:=1;

j1:=1;

j2:=il+1;

j3:=il+2;

j4:=il+3;

ilm:=il-1;

ksml:=kx-1;

kp1:=ksml+1;

cp:=1.00464e7;

g:=980.6;

bl:=2.301e10;

pbar:=1.e6;

r:=2.87e6;

rv:=4.61e+6;

dt:=

if (ktau = 1) then

dt

else

2.0 *dt

end if;

new'rm, rmp:=

for k in 1,kx cross i in il,li cross j in j1,jl

t'rm,

t'rmp:=

if (rm[k,i,j] > 0.0) then

rm[k,i,j],

rm[k,i,j] / (ps[i,j]+pbar)

else

0.0,

0.0

end if;

returns

array of t'rm

array of t'rmp

end for;

dmosp:=0.0;

emosp:=0.0;

new'ip, new'up, new'rp, new'rmp, new'sigdot,

new'cke, new'cks, new'that,

new'pe, new'pbar, new'romg:=

for i in il,li cross j in j1,jl

psijc:=ps[i,j]+pbar;

psijci:=1.0/psijc;

corf1,corf2:=_

if boundary'cell(i,il,li,j,j1,jl) then

0.0,0.0

else

0.125*(corp[i,j]+corp[i+1,j]),

0.125*(corp[i,j]+corp[i,j+1])

end if;

emthad := emsq[i,j]*psijci*tdsi;

em2ip := emthad*psijci*r / cp;

emhad1,emhad2:=_

if boundary'cell(i,il,li,j+1,jl) then

0.0,0.0

else

0.25*tdsi*(em[i,j]+em[i+1,j])

0.25*tdsi*(em[i,j]+em[i,j+1])

end if;

emosp:=emosp; % 0.0 then cycle'emosp

bmonp:=bmonp; % 0.0 then cycle'dmonp

cycle'dmonp, fmosp:=

if boundary'cell(i,il,li,j,j1,jl) then

0.0,0.0

else

em[i+1,j]/(ps[i+1,j]+pbar),

em[i,j+1]/(ps[i,j+1]+pbar)

end if;

new'bmonp:=

if (i = il) & ((j = j1) -- (j = jl))) then

em[i,j]*psijci

else

cycle'dmonp

end if;

new'amosp:=

if (i = il) & ((j = j1) -- (j = jl))) then

0.25*(new'bmonp+fmosp+em[i-1,j] / (ps[i-1,j]+pbar)

+em[i-1,j+1] / (ps[i-1,j+1]+pbar))

else

emosp

end if;

cmonp:=new'bmonp+cycle'dmonp;

cycle'emosp, new'cmonp:=

if boundary'cell(i,il,li,j,j1,jl) then

0.0, cmonp

else

0.25*(cmonp+em[i+1,j+1] / (ps[i+1,j+1]+pbar)+fmosp),

0.25*(cmonp+em[i+1,j-1] / (ps[i+1,j-1]+pbar)

+em[i,j-1] / (ps[i,j-1]+pbar))

end if;

pse, psn:=

if boundary'cell(i,il,li,j,j1,jl) then

0.0, 0.0

else

0.5*(ps[i,j]+ps[i+1,j])+pbar,

0.5*(ps[i,j]+ps[i,j+1])+pbar

end if;

%

% extra variables for evaluating p-grad terms logarithmically

%

pmi, pml, psdi, psdj, spdpj, emuds1, emvds1, emrds1:=

if boundary'cell(i,il,li,j,j1,jl) then

0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0

else

ps[i+1,j]-ps[i,j]-psm[i+1,j]+psm[i,j],

ps[i,j+1]-ps[i,j]-psm[i,j+1]+psm[i,j],

log(ps[i+1,j]+pbar)-log(psijc),

log(ps[i,j+1]+pbar)-log(psijc),

pbar*(ss[i+1,j]-ss[i,j]),

pbar*(ss[i,j+1]-ss[i,j]),

emsq[i,j]/(4.0*ds*pse),

emsq[i,j]/(4.0*ds*psn),

emsq[i,j]/(4.0*ds*psijc)

end if;

%

% compute total divergence

%

sumu, sumv, sumx, vadvu, vadvv, vadvrm, wvel, tlev:=

divergence sumu(i,j,ks,il,li,j1,jl,dsi,dq,u,v,t,emsq);

sigdot'k:=

for k in 1,kx

returns array of (

if (k = 1) then

0.0

else

wvel[k-1]-qph[k-1]*wvel[k]

end if)

end for;

vadvrm'k, vadvu'k, vadvv'k:=

for i in 1,kx

li:=i+1;

t'vadvrm, t'vadvu, t'vadvv :=_

if (i = ks) then

0.0, 0.0, 0.0

else

emuds1*(qph[i]*sumx-vadvrm[i])

*(new'rm[i,j]+new'rm[i,j])

+2.0*sqrt ((new'rmp[i,j]*new'rm[i,j]))),

emuds1*(qph[i]*sumu-vadvu[i])

*(u[i,j]+u[i,j]),

emuds1*(qph[i]*sumv-vadvv[i])

*(v[i,j]+v[i,j])

end if;

returns

array of t'vadvrm

array of t'vadvu

array of t'vadvv

end for;

%

% set up temperature difference terms

%

dtfdq:=

for k in 1, ks

returns array of (

if ((k = 1) == boundary'cell(i,il,li,j1,jl)) then

0.0

else

if (k = ks) then

dtmax*(tlev[ks]-tlev[ksml])+dtodq[ks]

else

0.5*(tlev[k+1]-tlev[k-1]) / dq[k]+dtodq[k]

end if

end if)

end for;

psmue, psmuw, psmuu, psmuu, psmuu, psmvn, psmvw, psmvw, psmvw:=

if ((j = jl) == boundary'cell(i,il,li,j1,jl)) then

0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0

else

if (i = ilm) then

1.5*psm[i,j]-0.5*psm[ilm,j]+pbar,

0.5*(psm[i+1,j]+psm[i,j])+pbar,

0.5*(psm[i,j-1]+psm[i+1,j-1])+pbar,

0.5*(psm[i,j]+psm[i+1,j])+pbar,

if (j = jlm) then

1.5*psm[i,j]-0.5*psm[i,jlm]+pbar

else

0.5*(psm[i,j+1]+psm[i,j+2])+pbar

end if;

end if;

```

```

% moisture

% rmw:=rmp[k,i,j]+rmp[k,i+1,j];

% rmn:=rmp[k,i,j]+rmp[k,i-1,j];

% rms:=rmp[k,i,j]+rmp[k,i,j+1];

% rmvd:=

% if (k = kz) then

%   0.0 %gke

% else

%   -(vadvrm[k+1]-vadvrm[k]) / dq[k]

% end if;

% rmhad:=-emsg[i,j]*tdsi*( u[k,i,j]*rmw-u[k,i-1,j]*rmw

% +v[k,i,j]*rmn-v[k,i-1,j]*rms);

% rmme := rmw*(pam[i+1,j]+pbar);

% rmww := rmn*(pam[i-1,j]+pbar);

% rmmu := rms*(pam[i,j+1]+pbar);

% rmmij := rmw*(pam[i,j-1]+pbar);

% rmbdf:=

% if (dnorm[k] = 0.0) then

%   0.0

% else

%   cdif[i,j]*dnorm[k]*dsi2

%   *(rmme+rmww+rmmu+rmmij-4.0*rmwij)

%   *(pam[i,j]+pbar)

% end if;

% t'rmwk := rmm[k,i,j]+dt*(rmhad+rmvd+rmhdf);

% suppress negative mixing ratios

% rmwk:=

% if (t'rmwk < 1.0E-20) then

%   0.0

% else

%   t'rmwk

% end if;

% in

%   rmwk,

%   t'pk,

%   omg

% end let

% end if;

% vp'k,

% new'cke'k,

% new'ppk',

% new'pvromg'k:=

% if ((l = 12)—boundary'cell(i,i1,i1,j1,j1)) then

%   vp[k,i,j],

%   0.0, %cke

%   0.0, %ppk

%   0.0 %pvromg

% else

%   let

%     ua:=u[k,i-1,j]+u[k,i-1,j+1];

%     ue:=u[k,i,j]+u[k,i,j+1];

%     va:=v[k,i-1,j]+v[k,i-1,j];

%     vb:=v[k,i,j]+v[k,i,j-1];

%     ve:=v[k,i,j-1]+v[k,i+1,j-1];

%     vr:=v[k,i,j]+v[k,i+1,j];

%     hadv1:=emhad*( ud*ud*cycle'dmonp-ub*ub*new'bmonp

%     +ue*ve*cycle'emonp-uc*vc*new'cmonp);

% compute pressure gradient terms on rhs of mtm. = ns.

% logarithmically

pg1:=((pse-pbar)*(phi[k,i+1,j]-phi[k,i,j])

+xpdi*rtbar[k]*perm1

+pse*pldi*( r0.5* (t[k,i+1,j]+t[k,i,j])

+rtbar[k]))*dsi;

ct1:= corf1*(vc+ve);

ubdiff:=

if (dnorm[k] = 0.0) then

0.0

else

cdif[i,j]*dnorm[k]*dsi2

*( um[k,i+1,j]/psmuc+um[k,i-1,j]/psmuw

+um[k,i,j+1]/psmuv+um[k,i,j-1]/psmu

-4.0*um[k,i,j]/psmu )*psmu

and if

in

(ct1+vat1-hadv1-pg1+ubdiff)*dt+um[k,i,j]

end let

end if;

% t'rmwk, t'pk, omega'k:=

if ((l = 12)—boundary'cell(i,i1,i1,j1,j1)) then

rmp[k,i,j],

t'pk[i,j],

omega[k]

else

% calculate horizontal advection term in the temp. = ation

let

wvel&v:=

if (l > 1) then

0.5*(wvel[k-1]+wvel[k])

else

0.5*wvel[1]

end if;

thadv1:= u[k,i,j]*(t[k,i+1,j]-t[k,i,j])

+u[k,i-1,j]*(t[k,i,j]-t[k,i-1,j]);

thadv2:= v[k,i,j]*(t[k,i,j+1]-t[k,i,j])

+v[k,i,j-1]*(t[k,i,j]-t[k,i,j-1]);

thadv := emhad*(thadv1+thadv2);

t'full:= t'levk[k]+thadv;

phadv1:= u[k,i,j]*(ps[i+1,j]-ps[i,j])

+u[k,i-1,j]*(ps[i,j]-ps[i-1,j]);

phadv2:= v[k,i,j]*(ps[i,j+1]-ps[i,j])

+v[k,i,j-1]*(ps[i,j]-ps[i,j-1]);

t'vong:= em2tp*(phadv1+phadv2);

t'psar:= t'vong*t'full;

omg:= wvel&v*q[k]*psijc*t'omg*cp / r;

gamapri:= (r / cp)*t'full / q[k]-dt(dq[k]);

t'difff:=

if (dnorm[k] = 0.0) then

0.0

else

cdif[i,j]*dnorm[k]*dsi2

*( tm[k,i+1,j]+tm[k,i-1,j]

+tm[k,i,j+1]+tm[k,i,j-1]-4.0*tm[k,i,j])

end if;

% t'pk:= (t'psar-thadv+thdiff

% +(wvel&v*gamapri+q[k]*dtdq[k]*wvel[kz])*psijci

% -(wvel&v*gamak+q[k]*dtdq[k]*wvel[kz]) / pbar

% )*dt+tm[k,i,j];

%

```

```

value of sum (dq[k]*psijc*(up'k*up'k+vp'k*vp'k)) %new'cke'k

value of sum (tlevk[k]*dq[k]) %new'ppe'k

value of sum (omega'k*omega'k*dq[k]) %new'pvromg'k

value of sum (t'rmk'k*dq[k])%ptrhat

end for; % k

t'new'ptrhat := new'ptrhat+emsq[i,j];

t'new'ppe := new'ppe*psijc*emsq[i,j];

t'new'vromg := new'vromg*emsq[i,j];

returns

array of tp'k

array of up'k

array of vp'k

array of rmp'k

array of sigdot'k

value of sum new'cke

value of sum (emsq[i,j]) %new'cks

value of sum (t'new'ptrhat*emsq[i,j])

value of sum t'new'ppe

value of sum ((psijc-0.988e6)*emsq[i,j]) % psbar

value of sum t'new'vromg

end for % i,j

in

new'rm,

new'sigdot,

new'up,

new'tp,

new'rmp,

new'up,

new'cke,

new'cks,

new'trhat,

new'pe,

new'psbar,

new'vromg

end let

end function

```

## References

- [1] Leslie, L.M. et al., "A High Resolution Primitive Equations NWP Model for Operations and Research", pp 11-35, Australian Meteorological Magazine, No. 33, Mar 1985.

- [2] Arakawa, A. and Lamb, V.R., "Computatioal Design of the Basic Dynamical Processes of the UCLA General Circulation Model," pp 174-256, 337, Methods of Computational Physics, Vol. 17, Academic Press, 1977.

- [3] Miyakoda, K., "Cumulative Results of Testing a Meteorological-Mathematical Model," pp 99-130, Royal Irish Academy Proceedings, July 1973.

- [4] McGraw et al., "SISAL: Streams and Iteration in a Single Assignment Language," Language Reference Manual Version 1.2, Lawrence Livermore National Laboratory, March 1, 1985.

- [5] Feo, J.T., and Cann, D.C., "A Report on the SISAL Language Project," *Journal of Parallel and Distributed Computing*, Vol. 10, pp 349-366, 1990.

- [6] Cray Research, "CF77 Compiling System Volume 4: Parallel Processing Guide," Cray Research, Incorporated, SG-3074 5.0, 1991.

- [7] Cann, D.C., "The Optimising SISAL Compiler: Version 12.0," Computing Research Group, L-306, Lawrence Livermore National Laboratory, Livermore, 1992.

# Even and Quarter-even Prime Length Symmetric FFTs and their SISAL Implementations \*

Jaiñe Seguel

Department of Mathematics

University of Puerto Rico

Mayaguez, Puerto Rico PR 00681

Dorothy Bollman

Department of Mathematics

University of Puerto Rico

Mayaguez, Puerto Rico PR 00681

## Abstract

*Even and quarter-even symmetric DFTs are variants of the discrete Fourier transform (DFT) in which all redundant operations induced on the DFT equations by the presence of either an even or quarter-even symmetry in the input data have been eliminated. These kinds of transforms appear frequently in image processing and in the core procedures of some direct methods for the numerical solution of the Poisson equation. Fast methods for computing even and the quarter-even DFTs when the number of data samples is a power of two have been proposed by Swarztrauber [8] and Briggs [1]. Their methods are generalizable to any factorizable number of data samples. In this article, following the basic mathematical techniques used by Rader [7] to derive a fast prime length FFT, we introduce fast methods for computing the even and the quarter-even symmetric DFT for a prime number of data samples. The expression of these methods in terms of matrix algebra facilitates their implementations in SISAL.*

## 1 Introduction.

Since its rediscovery in 1965 by Cooley and Tukey [2], the fast Fourier transform (FFT) has become one of the most widely used computational tools in science and engineering. The term FFT, initially associated with the Cooley-Tukey FFT for sequences of period  $N = 2^k$ , has become, after the efforts of many researchers over the years, the generic name of a whole family of efficient discrete Fourier transform (DFT) numerical methods. Each member in the FFT family is specialized to computing the DFT of a particular class of periodic sequences. This period is also referred to as the transform length and the DFT (FFT)

of length  $N$  is usually called an  $N$ -point DFT (FFT). An important member of this family is actually an extension of Cooley and Tukey's idea to  $N$ -point DFT's where  $N$  is factorizable. These  $N$ -point FFTs compute the  $N$ -point DFT through nested sequences of DFT's whose lengths are the factors of  $N$ . The Good-Thomas algorithm [5] improves the extended Cooley-Tukey FFT for transform lengths that are highly composite. Rader's algorithm [7], in turn, is designed for computing prime length DFT's. These algorithms, all members of the family of traditional FFTs, reduce the  $N$ -point DFT arithmetic complexity from  $O(N^2)$  to  $O(N \log N)$ .

A second family of fast DFT algorithms, called symmetric FFTs, was started with an article by Cooley, Lewis and Welch [3] in 1970. A symmetric FFT uses the symmetries of the input sequence to improve over its traditional FFT counterpart in terms of computational complexity and memory storage requirements. Especially important for their use in image processing and in fast Poisson solvers design are the even-symmetric FFT (E) and the quarter-even symmetric FFT (QE). The Cooley-Lewis-Welch algorithm computes the  $N$ -point DFT of a real (E) sequence using a  $N/2$ -FFT as a core procedure. This algorithm involves, however, a numerically unstable pre-process. Dollimore [4] redesigned the Cooley-Lewis-Welch algorithm improving on its numerical stability properties. Swarztrauber [8], who coined the term symmetric FFT, found a family of algorithms for computing real (E) and (QE) symmetric FFTs of any factorizable length. The main strategy in Swarztrauber's approach is to eliminate data redundancies induced by the symmetry of the input sequence in the intermediate steps of the traditional extended Cooley-Tukey FFT. Swarztrauber's algorithm does not consist of a core procedure separated from pre- or post-processes but its data flow is not as regular as its traditional counterpart.

\*This work was supported by NSF grant RII-8905080 and the Computational Mathematics Group of Puerto Rico EPSCoR II grant.

Briggs's algorithm [1] is in the same spirit of Swarztrauber's but with a more regular data flow.

The purpose of this article is to propose new algorithms for computing the DFT of (E) and (QE) symmetric FFTs of prime length and test their Sisal implementations. These algorithms fill a gap in the symmetric FFT family since none of the above mentioned methods can be used for computing symmetric DFT's of prime length.

## 2 Background

The discrete Fourier transform of an  $N$ -periodic complex sequence  $\mathbf{x} = (x_n)$  is the  $N$ -periodic complex sequence  $\tilde{\mathbf{X}} = (\tilde{X}_k)$  determined by the equations

$$\tilde{X}_k = \sum_{n=0}^{N-1} x_n \omega_N^{kn}, \quad k = 0, \dots, N-1, \quad (1)$$

where  $\omega_N = \exp(-2\pi i/N)$  and  $i = \sqrt{-1}$ . Since these sequences are periodic of period  $N$ , the indices  $n$  and  $k$  range over  $Z/N$ , the set of integers modulo  $N$ . Also, the sequences  $\mathbf{x}$  and  $\tilde{\mathbf{X}}$  can be represented by the vectors  $\mathbf{x} = (x_0, \dots, x_{N-1})$  and  $\tilde{\mathbf{X}} = (\tilde{X}_0, \dots, \tilde{X}_{N-1})$ . This gives the following matrix formulation of equation (1)

$$\tilde{\mathbf{X}} = F_N \mathbf{x}$$

where  $F_N = [\omega_N^{kn}]$ ,  $0 \leq k, n \leq N-1$  is an  $N \times N$  complex matrix.

An  $N$ -periodic sequence  $\mathbf{x} = (x_n)$  is said to be:

even – symmetric (E) if  $x_n = x_{-n}$  and

quarter – even symmetric (QE) if  $x_n = x_{-(n+1)}$ .

For an odd number  $N$ , a fundamental set of indices for the (E) symmetry is any subset  $S$  of  $Z/N$  satisfying:

$$(E1) \quad S \cup (-S) = Z/N \quad \text{and} \\ (E2) \quad S \cap (-S) = \{0\}$$

where  $-S = \{-n : n \in S\}$ . A fundamental set of indices  $S$  for the (QE) symmetry, in turn, is any subset of  $Z/N$  satisfying:

$$(QE1) \quad S \cup -(S+1) = Z/N \quad \text{and} \\ (QE2) \quad S \cap -(S+1) = \frac{N-1}{2},$$

where  $S+1 = \{n+1 : n \in S\}$ . The set  $\{0, 1, \dots, \frac{N-1}{2}\}$  is a fundamental set of indices for both symmetries. The restriction of an (E) ((QE)) symmetric sequence to an (E) ((QE)) fundamental set of indices eliminates

redundant data. If  $\mathbf{x} = (x_n)$  is (E) symmetric, its discrete Fourier transform  $\tilde{\mathbf{X}} = (\tilde{X}_k)$  is also (E) symmetric and so, equation (1) can be reduced to

$$\tilde{X}_k = x_0 + \sum_{n=1}^{\frac{N-1}{2}} x_n (\omega_N^{kn} + \omega_N^{-kn}),$$

$$k = 0, 1, \dots, \frac{N-1}{2} \text{ for } N \text{ odd.}$$

This equation defines the even discrete Fourier transform ((E) DFT). Since  $\omega_N^{kn} + \omega_N^{-kn} = 2 \cos(2\pi kn/N)$ , the (E) DFT is sometimes called the cosine transform. Its matrix representation is the  $\frac{N-1}{2} + 1 \times \frac{N-1}{2} + 1$  real matrix

$$F_N^{(e)} = \begin{bmatrix} 1 & 2 & 2 & \dots & 2 \\ 1 & c_1 & c_2 & \dots & c_{\frac{N-1}{2}} \\ \vdots & \vdots & \vdots & & \vdots \\ 1 & c_k & c_{2k} & \dots & c_{(\frac{N-1}{2})k} \\ \vdots & \vdots & \vdots & & \vdots \\ 1 & c_{\frac{N-1}{2}} & c_{2(\frac{N-1}{2})} & \dots & c_{\frac{(N-1)^2}{2}} \end{bmatrix}$$

where  $c_m = 2 \cos(2\pi \frac{m}{N})$ . On the other hand, if  $(x_n)$  is (QE) symmetric, equation (1) can be reduced to

$$\tilde{X}_k = x_{\frac{N-1}{2}} \omega_N^{\frac{k(N-1)}{2}} + \sum_{n=0}^{\frac{N-1}{2}-1} x_n (\omega_N^{kn} + \omega_N^{-k(n+1)}),$$

The (QE) symmetry does not induce any reduction in the number of DFT outputs. Therefore, the matrix representation of the (QE) DFT is an  $N \times \frac{N-1}{2} + 1$  complex matrix. We denote this matrix  $F_N^{(qe)}$ .

Rader's prime length complex FFT is based on the identification of an  $N-1 \times N-1$  block in  $F_N$  which can be transformed into a Hankel-circulant by means of appropriate row and column permutations. In general, an  $M \times M$  matrix  $A$  is a Hankel-circulant if it can be written as

$$A = \begin{bmatrix} a_0 & a_1 & a_2 & \dots & a_{M-1} \\ a_1 & a_2 & \dots & a_0 & \\ a_2 & & \dots & a_1 & \\ \vdots & \vdots & \vdots & \dots & \vdots \\ a_{M-1} & a_0 & a_1 & \dots & a_{M-2} \end{bmatrix}$$

We use the notation  $A = \text{Circ}(a_0, \dots, a_{M-1})$  and  $G_A = (a_0, a_1, \dots, a_{M-1})^T$ , the "generator" of  $A$ .

Hankel-circulants admit the following interesting matrix factorization: Let  $A$  be an  $M \times M$  Hankel-circulant and let  $\Omega(A)$  be the diagonal matrix whose

main diagonal is the inverse DFT of the first row of  $A$ . Then,

$$A = F_M \Omega(A) F_M$$

Thus, the multiplication of a Hankel-circulant  $A$  of order  $M$  by a vector can be computed in terms of  $M$ -point FFTs, in fact, in terms of  $2^k$ -point FFTs by embedding  $A$  in a circulant  $\tilde{A}$  of order  $2^k$  defined as follows: Let  $A = \text{Circ}(a_0, a_1, \dots, a_{M-1})$  and let  $k$  be the minimum  $m$  for which  $2^m \geq 2M - 1$ . Define

$$\tilde{A} = \text{Circ}(a_0, \dots, a_{M-1}, a_0, a_1, \dots, a_{M-2}, 0, \dots, 0)$$

where the number of zeros inserted is  $2^k - 2M + 1$  and for any vector  $x$  of length  $M$ , let  $\tilde{x}$  be the vector of length  $2^k$  obtained from  $x$  by padding the last  $2^k - 2M + 1$  positions with zeros. Then  $\tilde{A}x$  is the vector consisting of the first  $M$  components of  $\tilde{A}\tilde{x}$ .

In order to identify the Hankel-circulant block in  $F_N$  let us rewrite the  $N$ -point DFT matrix as

$$F_N = \begin{bmatrix} 1 & e^T \\ e & W_N \end{bmatrix}$$

where  $e$  is the column vector of ones of length  $N - 1$  and  $e^T$  is its transpose. The  $N - 1 \times N - 1$  complex block can be transformed into a Hankel-circulant by pre- and post-multiplications by permutation matrices whose definition rely on the field structure of  $Z/N$ . Indeed, if  $N$  is prime, then  $Z/N$  is a field and the multiplicative group  $U(N) = Z/N - \{0\}$  is a cyclic group generated by a primitive root  $g$  modulo  $N$ . For example,  $U(5) = \{1, 2, 3, 4\}$  is generated by  $g = 2$  since

$$\begin{aligned} <2^0>_N &= 1 \\ <2^1>_N &= 2 \\ <2^2>_N &= 4 \\ <2^3>_N &= 3 \end{aligned}$$

where  $<\cdot>_N$  denotes the least positive residue congruent to  $g^k$  modulo  $N$ . Thus, if  $g$  is a primitive root modulo  $N$  we define  $P_{N,g}$  as a matrix representation of the permutation  $y_k \leftarrow x_{<g^{k-1}>_N}$ ,  $1 \leq k \leq N - 1$ . It can be easily shown that

$$\tilde{W}_N = P_{N,g} W_N P_{N,g}^{-1}$$

where  $\tilde{W}_N = \text{Circ}(\omega_N, \omega_N^{<g>_N}, \dots, \omega_N^{<g^{N-2}>_N})$ . Hence,

$$F_N x = \begin{bmatrix} 1 & e^T \\ e & P_{N,g}^{-1} \tilde{W}_N P_{N,g} \end{bmatrix} x$$

where  $e$  is a column vector of 1's and  $e^T$  is its transpose. Thus,

$$\begin{aligned} F_N x &= y + \begin{bmatrix} 0 \\ P_{N,g}^{-1} \tilde{W}_N P_{N,g} x' \end{bmatrix} \\ &= y + \begin{bmatrix} 0 \\ P_{N,g}^{-1} F_M (F_M^{-1} G_{\tilde{W}_N} \circ F_M P_{N,g} x') \end{bmatrix} \end{aligned}$$

where  $M = N - 1$ ,  $\circ$  denotes component-wise multiplication,

$$y = \begin{bmatrix} x_0 + x_1 + \dots + x_{N-1} \\ x_0 \\ \vdots \\ x_0 \end{bmatrix}$$

and  $x'$  is the result of deleting the first component of  $x$ . This matrix expression is essentially Rader's algorithm. The same factorization but using  $\tilde{W}_N$  instead of  $W_N$  gives what we call the extended Rader algorithm.

In the rest of this paper, we show how, as in the extended Rader algorithm, the core procedures for computing even and quarter-even prime length symmetric FFTs can be written as the product of a Hankel-circulant by a vector. The efficiency of these algorithms, as well as the Rader algorithm or its extended version, depends on the availability of efficient algorithms for computing FFTs.

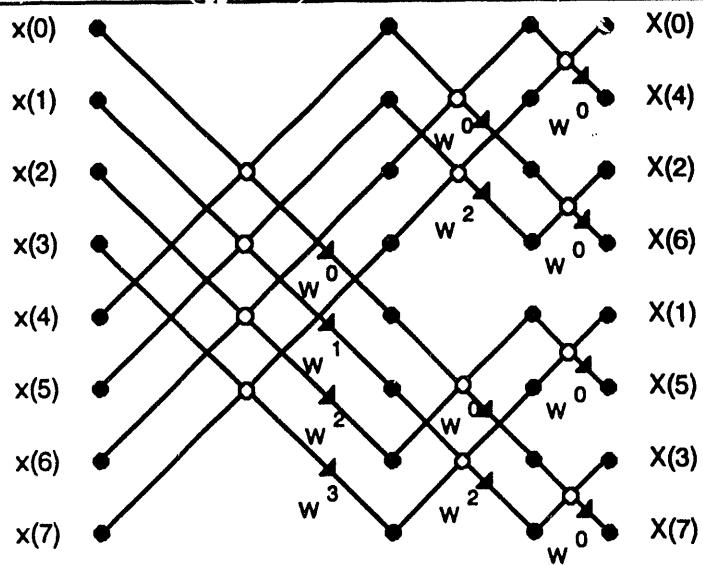

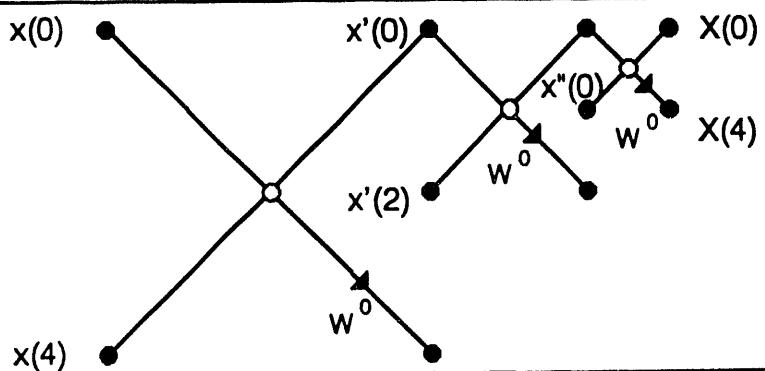

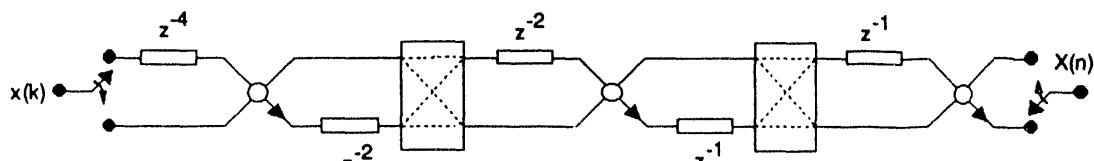

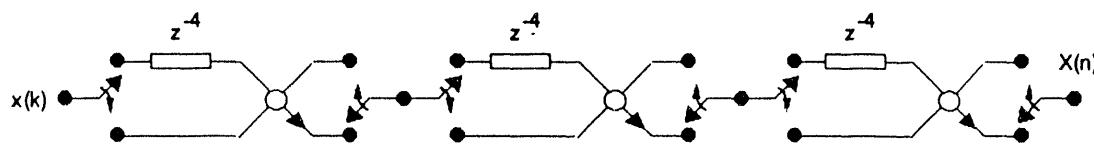

### 3 Prime length (E) symmetric FFTs

Let us rewrite the (E) DFT matrix as

$$F_N^{(e)} = \begin{bmatrix} 1 & 2e^T \\ e & C_N \end{bmatrix}$$

where  $C_N = [c_{kn}]$ ,  $1 \leq k, n \leq \frac{N-1}{2}$ , an  $\frac{N-1}{2} \times \frac{N-1}{2}$  real matrix. Now let  $g$  be a primitive root modulo  $N$  and define  $P_{N,g}^{(e)}$  to be the matrix representation of the permutation on  $1 \leq n \leq \frac{N-1}{2}$ , defined by the map

$$p_{N,g}^{(e)}(n) = \begin{cases} <g^{n-1}>_N, & \text{if } <g^{n-1}>_N \leq \frac{N-1}{2} \\ <N - g^{n-1}>_N, & \text{otherwise} \end{cases}$$

Then we have

$$F_N^{(e)} x = \begin{bmatrix} 1 & 2e^T \\ e & P_{N,g}^{(e)-1} \tilde{C}_N P_{N,g}^{(e)} x \end{bmatrix}$$

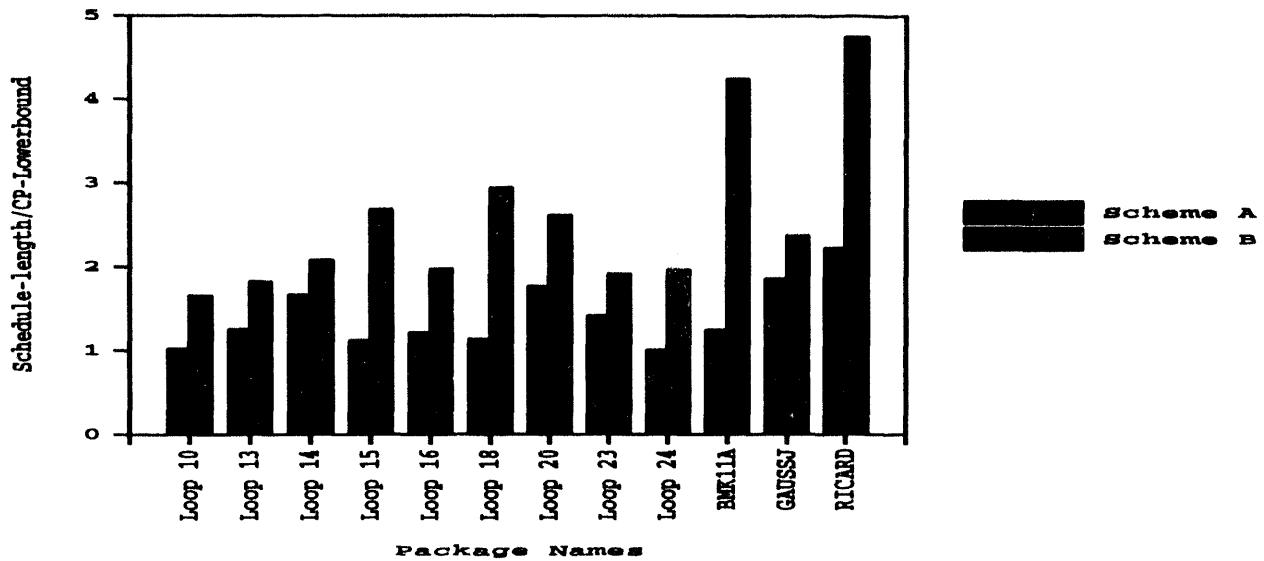

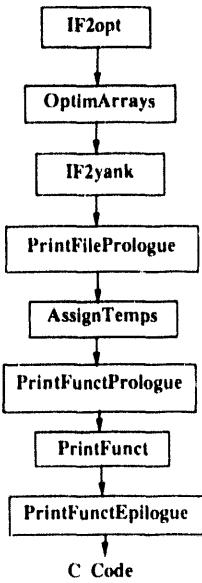

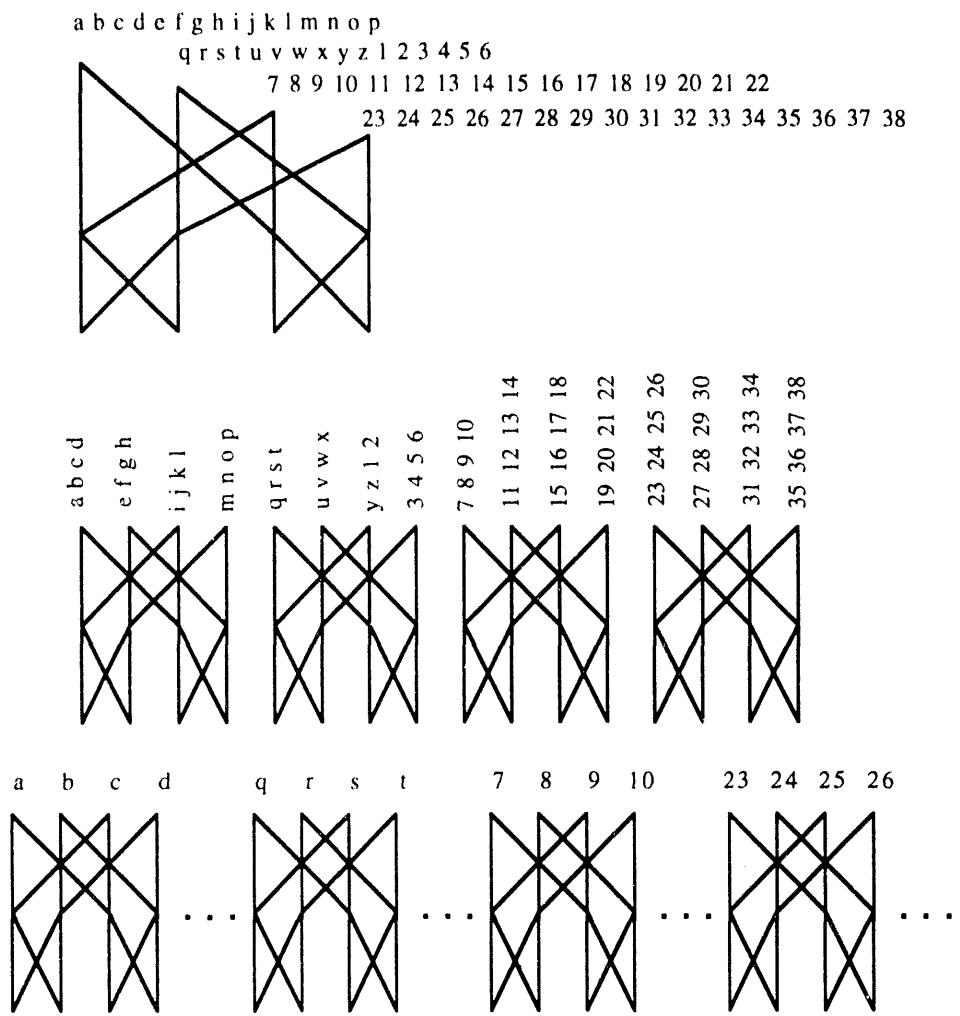

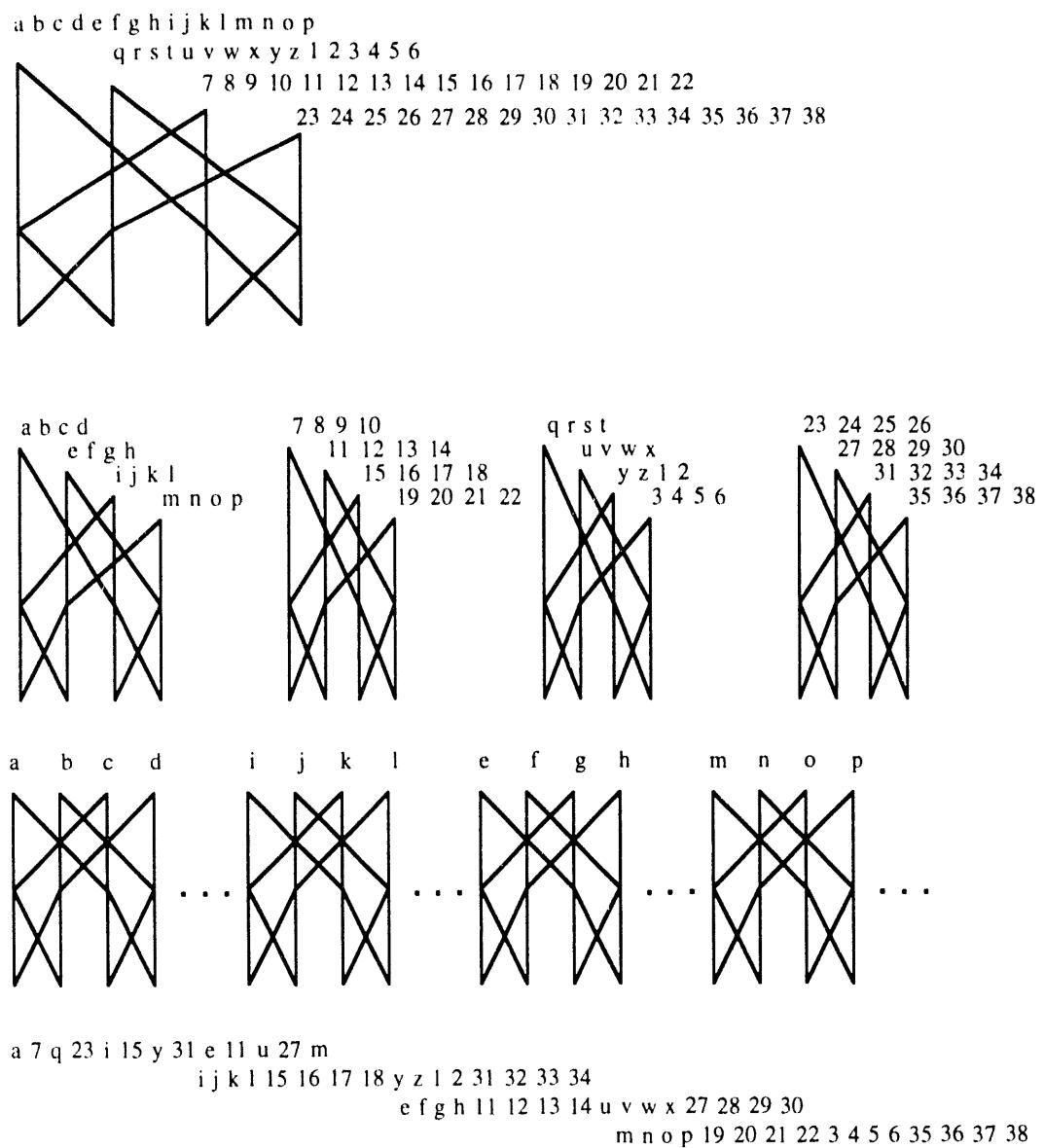

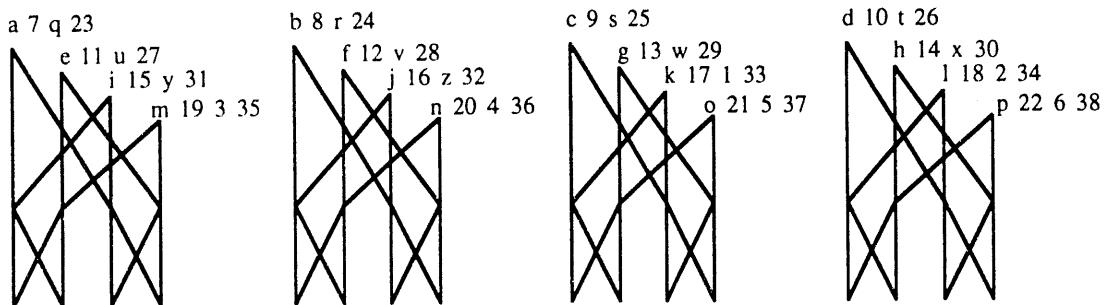

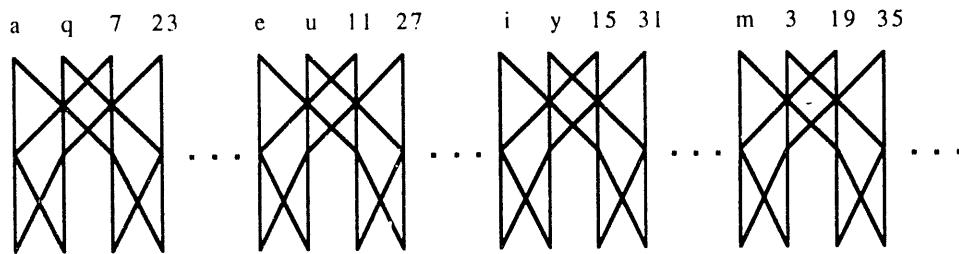

where