#### ОБЪЕДИНЕННЫЙ ИНСТИТУТ ЯДЕРНЫХ ИССЛЕДОВАНИЙ

) NR- D--13-94-491

# XVI International Symposium on Nuclear Electronics and VI International School on Automation and Computing in Nuclear Physics and Astrophysics

Varna, 12-18 September 1994

XVI Международный симпозиум по ядерной электронике и VI Международная школа по автоматизации исследований в ядерной физике и астрофизике

Варна, 12-18 сентября 1994 г.

IJ

We regret that some of the pages in this report may not be up to the proper legibility standards, even though the best possible copy was used for scanning

XVI International Symposium on Nuclear Electronics and 6-th International School on Automation and Computing in Nuclear Physics and Astrophysics were held in Varna on September 12-18, 1994.

#### Organized by:

Joint Institute for Nuclear Research, Dubna, Russia

Institute for Nuclear Research and Nuclear Energy of the Bulgarian Academy of Sciences, Sofia, Bulgaria

Institute for Nuclear Research of the Russian Academy of Sciences, Moscow, Russia

International Academy of Informatization

XVI Международный симпозиум по ядерной электронике и 6-ая Международная школа по автоматизации исследований в ядерной физике и астрофизике проходили в Варне 12-18 сентября 1994 г.

#### Организаторы:

Объединенный институт ядерных исследований, Дубна, Россия

Институт ядерных исследований и ядерной энергетики Болгарской академии наук, София, Болгария

Институт ядерных исследований Российской академии наук, Москва, Россия

Международная академия информатизации

#### General Consulting Committee:

Velikhov E.P., vice-president of R.A.Sc. (chairman); Vinogradov V.I. INR of R.A.Sc.; Gustavson D.B., prof., Stanford, USA.

#### **International Program Committee:**

Churin I.N., Dr., JINR, Dubna (co-chairman); Vankov I.D., Dr., INRNE, Sofia (co-chairman); Vinogradov V.I., Dr., INR, Moscow (co-chairman); Evreinov E.V., vice-president of the International Academy of Informatization; Hunt R., prof., Oxford, Great Britain; Mueller K.D., prof., Julich, Germany; Naumann D., prof., Berlin, Germany; Probert D., Dr., Reding, England; Sunol A., prof., Florida, USA.

# Contents Содержание

#### A. Front-End Electronics and Detectors

| R.Bock Triggering of the detectors at CERN                                            | 9  |

|---------------------------------------------------------------------------------------|----|

| F.Maddaleno, M.Rossi A study of analog-to-digital sliding scale converter utilization | 20 |

| M.A.Baturitsky, V.A.Chekhovsky, I.F.Emel yanchik, N.M.Shumeiko,                       |    |

| I.A.Golutvin, N.I.Zamyatin                                                            |    |

| Fast low noise monolithic charge sensitive preamplifiers IC for hadron calorimeter    | 27 |

| O.V.Strekalovsky, K.Heidel, S.I.Ivanovsky, D.May, HG.Ortlepp,                         |    |

| G.Pausch, G.Renz, V.E.Shuchko, W.Wagner, V.V.Trofimov, I.P.Tsurin                     |    |

| The front-end electronics and the data acquisition system of the FOBOS $4\pi$ -array  | 31 |

| В.В.Сидоркин                                                                          |    |

| Система съема информации с дрейфовых камер                                            |    |

| на основе времяцифровых преобразователей                                              |    |

| с 2 нс разрешением в стандарте КАМАК                                                  | 38 |

| А.И.Климов, Е.А.Мелешко, А.Г.Морозов, Г.Н.Дудкин,                                     |    |

| Л.А.Кузьмичев, А.А.Паньков                                                            |    |

| Электронная аппаратура черенковских детекторов                                        |    |

| Электронная аппаратура черенковских детекторов                                        | 42 |

| Б.А.Борисовец, Л.А.Донских, А.М.Клабуков, А.И.Климов,                                 |    |

| Л.А.Кузьмичев, Е.А.Мелешко, А.Г.Морозов, И.Е.Осташев, Т.Тон                           |    |

| Подводная электроника нейтринного детектора                                           | 45 |

| K.Inakiev, T.Grigorov                                                                 |    |

| Enhanced timing channel for spectroscopy amplifiers                                   | 48 |

| F.A.Ermalitski, S.S.Vetokhin, V.B.Zalesski                                            |    |

| Large area silikon avalanche MRS-photodiodes for nuclear spectrometry                 | 53 |

| K.Inakiev, T.Grigorov                                                                 |    |

| Pole-zero adjustment of spectroscopy amplifiers using MCA                             | << |

| 1 or reto achaement of short osoph ambutters using mon                                |    |

#### B. Data Acquisition and Processing

| B.Hoffmann Building blocks for modular data acquisition systems                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

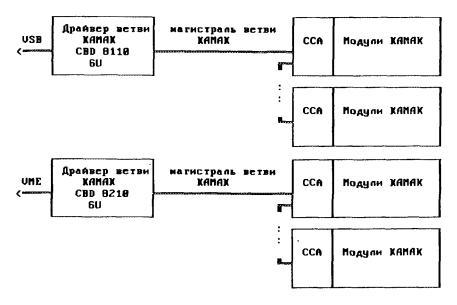

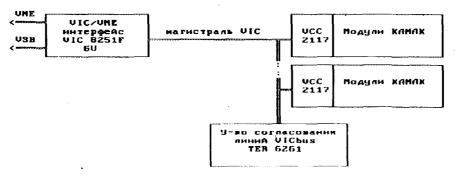

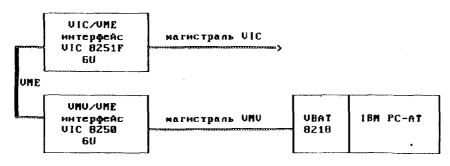

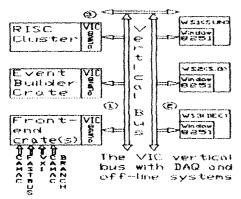

| В.А.Смирнов Организация систем сбора данных на основе аппаратуры, выполненной в разных стандартах 68                                                                                                 |

| В.Г.Тишин Некоторые концепции развития многомерных измерительных систем на физических установках ЛНФ ОИЯИ                                                                                            |

| А.А.Грибов, В.А.Жуков, С.И.Сдобнов, Г.В.Яковлев Решение сложных измерительных проблем при автоматизации научного эксперимента и технологических процессов                                            |

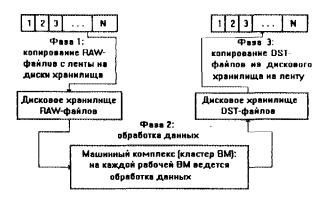

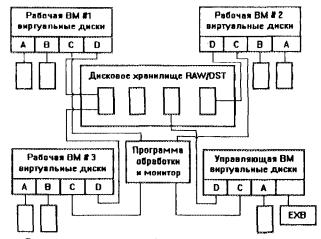

| И.М.Иванченко, З.И.Коженкова, В.В.Кореньков, Ю.А.Кретов, А.Г.Скрипничук<br>Архитектура системы массовой обработки экспериментальных данных<br>с установки EXCHARM на базе кластера виртуальных машин |

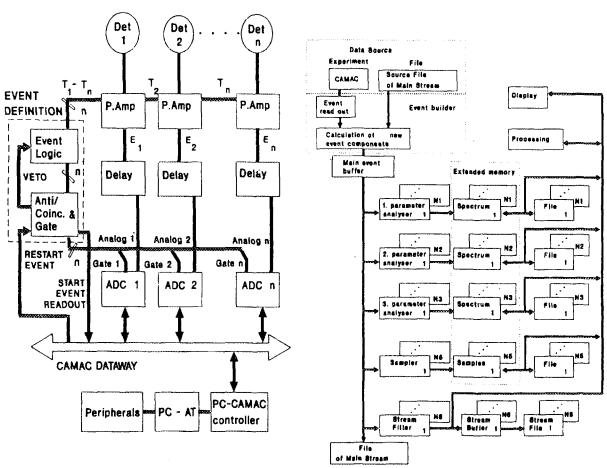

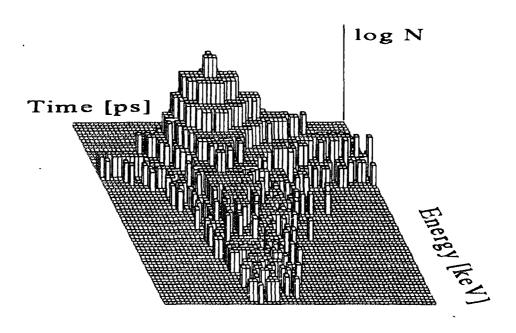

| M. Morhac, I. Turzo, J. Kristiak, V. Matousek  Multiparameter nuclear data acquisition and processing system                                                                                         |

| Н.И.Журавлев, В.Е.Сидоров<br>Система считывания информации с пропорциональных камер                                                                                                                  |

| Ц.Пантелеев, В.Минкова, Н.Камбуров, А.Дражев, И.Кожухаров Электронная система для измерений с многоцелевым нейтронным детектором                                                                     |

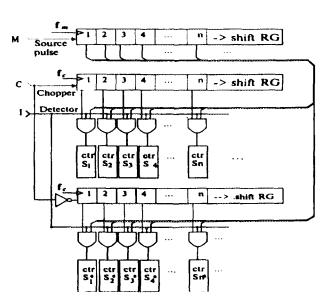

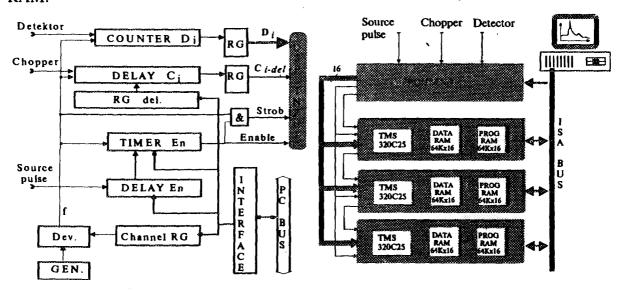

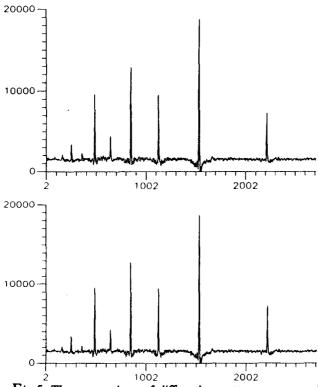

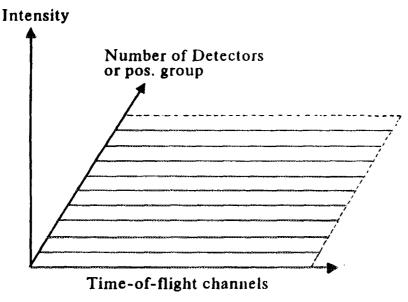

| V.A.Butenko, V.A.Drozdov, A.S.Kirillov, V.E.Novozhilov, A.I.Ostrovnoj, V.I.Prikhodko, V.E.Rezaev, Ja.Sudek, D.Krushinskij The DSP-based RTOF correlator for high resolution Fourier diffractometers  |

| В.Е.Резаев Спектрометрическое запоминающее устройство в стандарте VME107                                                                                                                             |

| M. Morhac, V. Matousek, I. Turzo  Multiparameter amplitude analysis with on-line compression using adaptive orthogonal transform                                                                     |

| D. Yu. Mostovoy, Yu. P. Lyashchenko Russian anti-virus technology versus western tools                                                                                                               |

| C. Networks and Buses                                                                                                                                                                                |

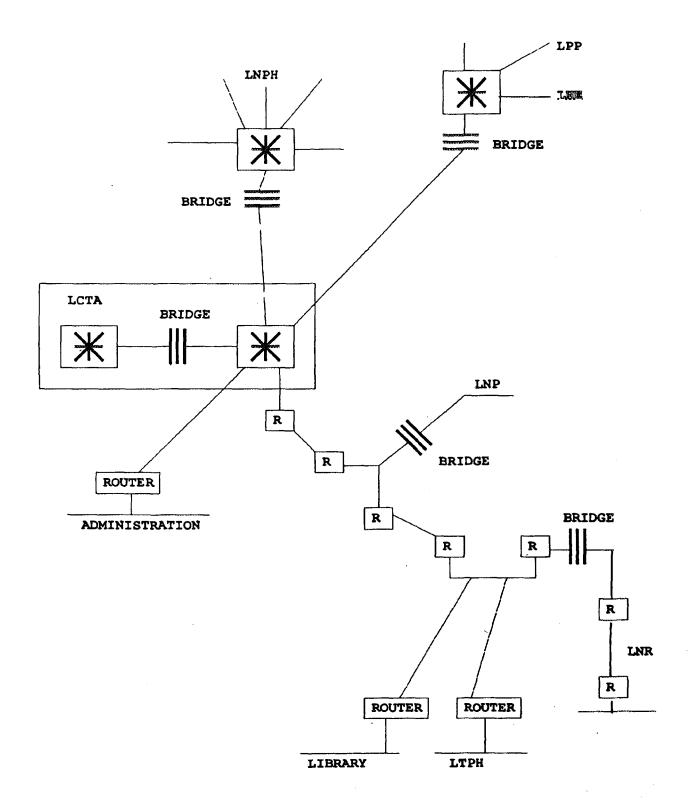

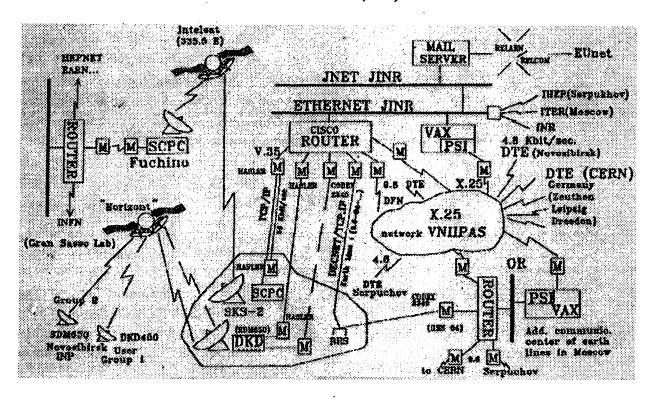

| A.T. Dorokhin, V.P. Shirikov  The status of computing and means of local and external networking at JINR122                                                                                          |

| M. Tomasevic, V. Milutinovic  The cache coherence problem in shared memory multiprocessors: hardware solutions                                                                                       |

| T. Tartalja, V. Milutinovic  The cache coherence problem in shared memory multiprocessors: software solutions                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

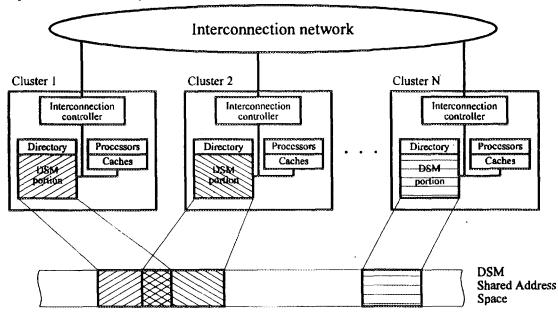

| J.Protic, M.Tomasevic, V.Milutinovic A survey of distributed shared memory approaches132                                                                                                                              |

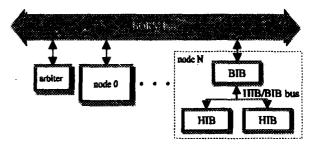

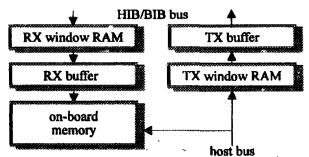

| M.Jovanovic. M.Tomasevic, V.Milutinovic  Design issues for a block-oriented reflactive memory system                                                                                                                  |

| A. Janicijevic, E. Jovanov, D. Raskovic, V. Milutinovic A comparison of two approaches to ATM router chip design                                                                                                      |

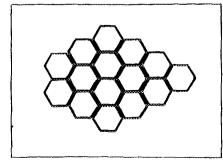

| D. Milutinovic Time analysis of interconnection networks implemented on the HONEYCOMB architecture147                                                                                                                 |

| D. Milutinovic  Area analysis of interconnection networks implemented on the HONEYCOMB architecture                                                                                                                   |

| V.I. Vinogradov  Ring interconnection for distributed memory automation and computing system157                                                                                                                       |

| D. Spectrometers and Radiometers                                                                                                                                                                                      |

| S.K.Andrukhovich, A.V.Berestov, V.M.Grebenjuk, V.I.Gut ko, A.M.Khilmanovich, E.A.Rudak, A.S.Uzunbadjakov, F.E.Zjazjulja High-sensitivity multidimensional gamma-ray spectrometer «PRIPYAT» for low-level measurements |

| Г.Георгиев, И.Ванков, Л.Димитров, И.Пеев<br>Многоканальный анализатор в персональном компьютере,<br>использующий канал прямого доступа к памяти                                                                       |

| S.M.Dmitriev, F.A.Ermalitski, A.A.Kolyada, S.V.Sukhanin, L.N.Vasilevich The multichannel system of synchronous proton counting of range 50 ns — 100 ms168                                                             |

| F.A.Ermalitski, A.A.Kolyada, V.V.Revinski, L.N.Vasilevich About using of the high speed modular computing structures in the systems of radiation express analysis                                                     |

| I. Vankov, Ch. Kambourov, L. Dimitrov, B. Kunov, G. Georgiev  Low-level beta-activity radiometer with compensator of the background                                                                                   |

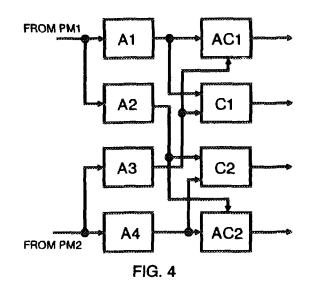

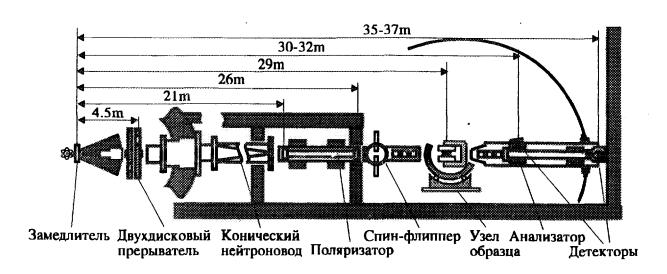

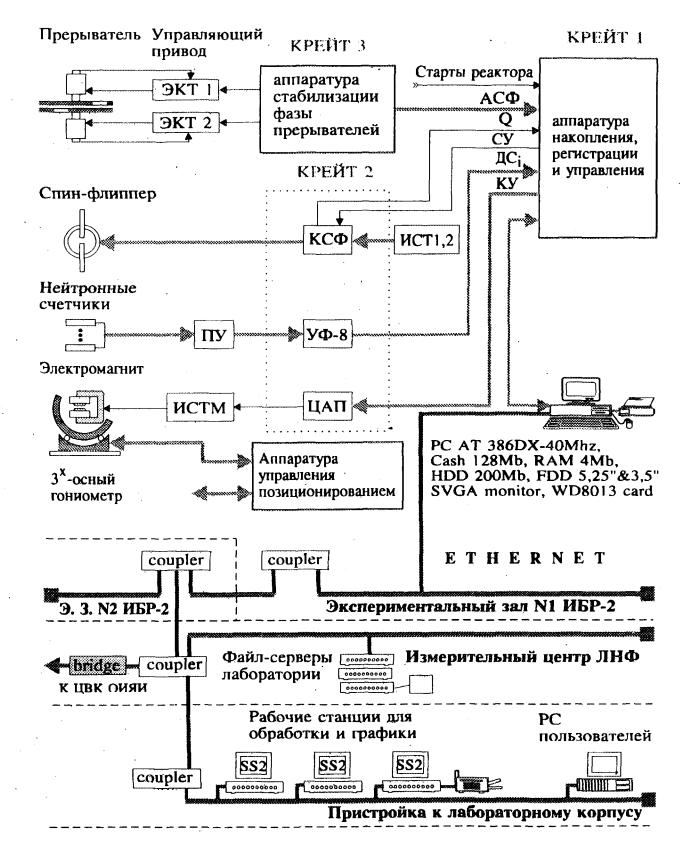

| В.В.Журавлев, Д.А.Корнеев, Е.И.Литвиненко, Д.И.Ляпин<br>Измерительно-накопительный модуль спектрометра<br>на поляризованных нейтронах СПН-1178                                                                        |

| Н.Милева, А.Петров, Н.Павлов<br>Компьютерно-интегрированные среды для проблемного обучения<br>по электронике на основе аналогового симулятора PSPICE                                                                  |

#### E. Control Systems and Equipment

| R. Barillere et al. (The CICERO group)                                                |   |

|---------------------------------------------------------------------------------------|---|

| CICERO: Research in the design of software for control systems                        |   |

| using object-oriented techniques                                                      | 8 |

| V. A. Cuduca. A. C. Hamanaga. A. D. Hilanaga. D. M. Danaga.                           |   |

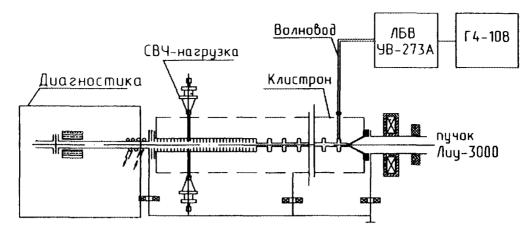

| К.А.Гудков, А.С.Чепурнов, А.В.Шумаков, В.И.Виноградов                                 |   |

| Концепция систем автоматизации контроля и управления                                  | - |

| технологическими объектами ускорителя19                                               | / |

| J.Kliman, V.Matousek, M.Morhac, I.Turzo, Y.Anisimov, A.Artiomov, S.Basilev, V.Slepnev |   |

| PC-based control of the internal target station at the nuclotron                      | 2 |

| птС. Э п 4 п                                                                          |   |

| В.Т.Сидоров, П.А.Петев                                                                |   |

| Автоматизация электростатического и магнитного $\beta$ -спектрометров                 | ð |

| А.Н.Баландиков, В.И.Волков, В.М.Горченко, И.И.Куликов,                                |   |

| С.В.Романов, А.П.Царенков                                                             |   |

| Измерение параметров выведенных пучков заряженных частиц                              |   |

| на ускорительном комплексе ЛВЭ                                                        | 2 |

| Л. Димитров, Г. Георгиев, И. Ванков, В. Волков                                        |   |

| Блок отбора и сохранения видеоизображения21                                           | ۵ |

| олок отоора и сохранения видсоизооражения                                             | • |

| О.Аварзад, В.С.Рихвицкий                                                              |   |

| Система пакетного ввода и вывода изображений                                          |   |

| для нейтронной радиографии на базе ПЭВМ IBM PC XT/AT22                                | 2 |

| W W Warmer                                                                            |   |

| И.Н. Чурин                                                                            |   |

| Контроллер крейта КАМАК КК014 на основе однокристальной микро-ЭВМ 8031                | 4 |

| для работы через последовательную линию связи RS-232C                                 | U |

| A.V.Pilyar                                                                            |   |

| Multifunction input-output board for the IBM PC AT/XT (Lab-Master)                    | 0 |

| В.И. Дацков, А.С. Никифоров, В.П. Николаев, Ю.А. Шишов                                |   |

| Система сбора данных сверхпроводящего соленоида на базе РС                            | 3 |

|                                                                                       |   |

| B.Kunov, G.Georgiev, L. Dimitrov, I. Atanassov, I. Vankov                             | _ |

| Computer controlled high voltage system                                               | 5 |

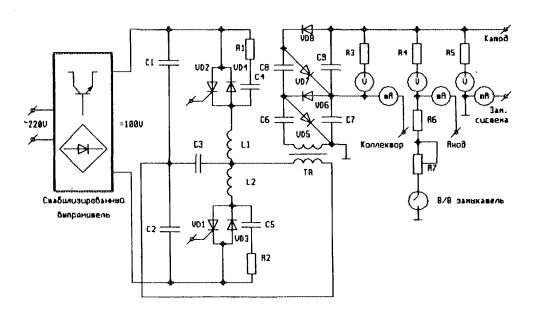

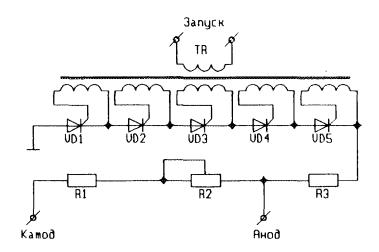

| Н.И.Лебедев, А.А.Фатеев                                                               |   |

| Высоковольтные источники питания для ЛБВ УВ-273А24                                    | 0 |

| A.M.Bufan, A.A.Ivanov, Yu.S.Nechaev                                                   |   |

| The optimized laser photoplotter of IHEP24                                            | 5 |

| ob                                                                                    | _ |

#### Triggering of the detectors at LHC

#### R.Bock, CERN

Switzerland

#### Abstract

The future Large Hadron Collider (LHC), to be built at CERN, presents among other technological challenges a formidable problem of real-time data analysis. From a primary buch crossing rate of 40 MHz, each crossing containing multiple pp collisions, a multi-stage trigger system has to analyze data to decide which is the fraction of events that should be preserved on permanent storage for further analysis. This is done by algorithms at different levels, using very partial and local data to start with, and, at reduced rates, increasingly complete data sets and complex algorithms subsequently.

We report here on the overall structuring of the trigger into three levels, and some further structuring, particularly of the critical second trigger level. We also discuss existing ideas about possible implementations.

#### 1. The Large Hadron Collider: a triggering challenge

The community of High Energy Physics is proposing the next-generation collider to be built at CERN, the 'Large Hadron Collider' or LHC. This new instrument will allow the international community of researchers to explore unknown areas of physics at the smallest scale, as it collides in its preferred mode two counter-rotating beams of protons each at an energy of 7000 GeV, not attainable in any accelerator today. The development of critical components for this collider, to be installed in the existing LEP underground ring, is well advanced: in particular, the critical superconducting magnets with fields of more than 9 Tesla have been industrially produced and successfully tested. Experimentation in that ring is expected to start at the beginning of the next century, in an optimistic scenario around the year 2002.

One characteristic property of the future collider [1] arises from the fact that the collisions giving clues to the physics of interest are rare<sup>1</sup>, and in particular the ratio between this and the overall collision rate is very small, like one in a million or less.

<sup>&</sup>lt;sup>1</sup> LHC physics is mainly focussed on discovery of the Higgs particle, postulated by theory to explain the mass scale of particles in the Standard Model. Further discovery potential exists for particles related to Supersymmetry, for possible unknown heavy gauge bosons, compositeness, and others. Beyond that, a wealth of information can be expected for top and beauty physics, and for high-cross section phenomena, also unknown at these energies.

The accelerator builders, therefore, put much ingenuity into achieving the highest possible 'luminosity', i.e. beam density and collision rate. They do this by fine focussing the largest possible number of protons into packets ('bunches') of less than 10cm length (and only a few µm diameter), which follow each other at very short time intervals (25 nsec - not a very long distance, as it corresponds to about eight meters at the speed of light). The detectors studying the collisions (two pp experiments are planned, the proposals are known under the names ATLAS and CMS, see [2], [3]) will then have to deal with very high rates of events and must attempt to achieve a time separation that takes advantage of the bunch structure - the limit being that some of the physics processes put to use in detectors take longer than the bunch separation.

Let us assume that the problem of separating collisions recorded in the detector into individual signals can be solved. This is only partially true at high luminosity, as multiple collisions will occur in a single bunch crossing, and appear as one 'supercollision'. There remains yet another challenge, though: to use the signals from a single bunch crossing, or at least a subset of them, in order to decide if one of the collisions at hand should be analyzed in more detail and eventually recorded. The detectors are, of course, constructed to provide signals corresponding to the signatures of interesting collisions, in nearly all cases characterized by high transverse momenta and by the occurrence of leptons (electrons, muons, tau-s, and neutrinos) and jets. This selection procedure of entire collisions is called 'triggering', and is familiar to physicists from past experiments, albeit at rates much lower than those imposed by the LHC. Our present contribution discusses briefly the structure of triggers at the LHC, and specific implementation possibilities of critical trigger parts.

#### 2. Technological preparation

In preparation for the challenges of the LHC, an impressive number of R&D projects, more precisely in excess of forty, have been initiated by an internationally composed 'Detector R&D Committee' over the last years. Many of them concern developments of novel detectors with optimal time resolution, or components that can resist the high radiation doses expected in LHC detectors, particularly those at small angles from the beams. Several of them also deal with the new problems of readout, data transmission and triggering. To mention a few of these projects:

- FERMI (RD16) has already demonstrated the design of fast non-linear 10-bit ADC-s (80 MHz) on chips, to be used in the readout modules of calorimeters. The plan is to equip all calorimeter channels in an experiment with microsystems containing analog and digital front-end electronics, allowing optimal signal extraction and data buffering during level 1 and level 2 leteroises.

buffering during level-1 and level-2 latencies.

- RD23 develops radiation-hard lightwave links, based on electro-optic intensity modulators, for economic transmission of analogue signals on fibres.

- RD12 has proposed practical ways of connecting a fast timing and control network to all individual readout units to identify bunch crossing and allow proper synchronisation.

- RD27 has worked on the details of level-1 triggers, and has successfully operated

a custom chip for calorimeter triggering (see chapter 4 below).

- EAST (RD11) explores architectures for implementing second-level triggering, and has demonstrated implementations of data-driven devices based on field-programmable gate arrays (see chapters 5 and 6 below).

There are further projects on transmission and switching technologies (ATM, SCI,

Fibre Channel), which will be mentioned below (see chapter 6 below).

#### 3. Overall trigger structure

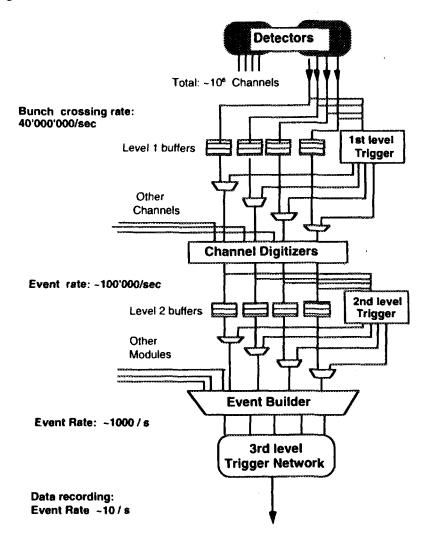

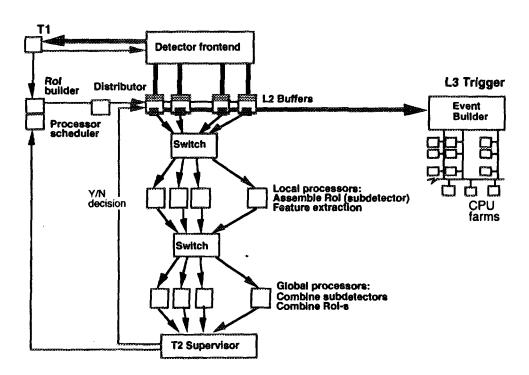

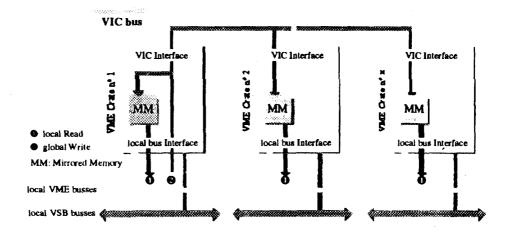

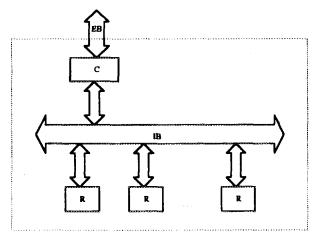

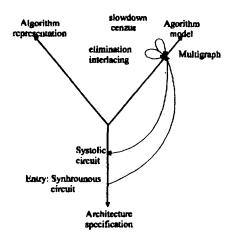

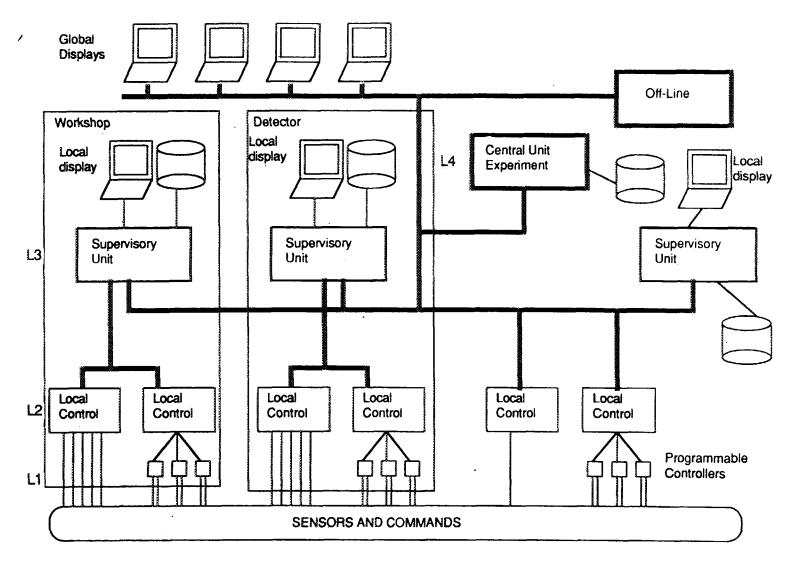

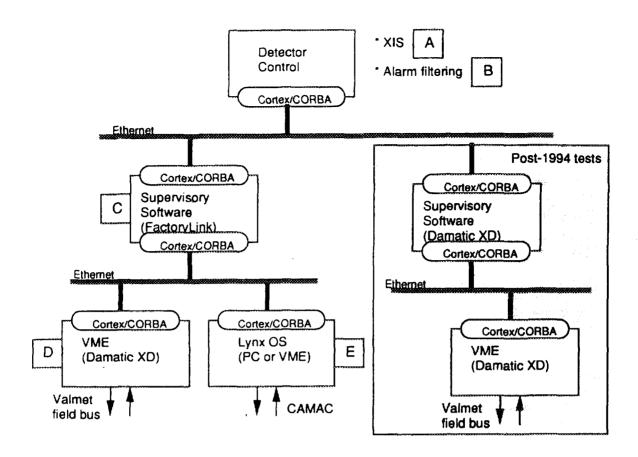

Physics at the LHC will start with a primary event rate of 40 MHz, the bunch crossing frequency. Each event is characterized by several Mbytes of information, once it is fully digitized. In real time at high frequency before rate-reducing triggers, this volume of information is transmitted (in analog or digital form) in parallel into thousands of individual buffers, with characteristics specific to the different subdetectors. The task of the trigger is to find the small number of interesting physics events, not more than a few (to be specific, certainly less than a hundred) per second. A succession of event selection algorithms is applied; close to the detectors they have to run at bunch crossing frequency and must be simple enough to be implemented in custom-made or specifically adapted hardware, with limited or no programmability. As there is a finite latency, viz. delay between the availability of data and a final 'yes/no' decision, transmission and operations have to be pipelined and all data stored in a buffer, avoiding dead time as much as possible. Schematically, this is shown in the following figure 1.

Figure 1.Overall structure of triggering in an LHC experiment

As the successive stages of event selection reduce the rates, algorithms of increasing complexity and implemented in processors of some generality become both necessary and possible. While this is certainly true for the last ('third') level of triggering, 'second-level' algorithms operate at an assumed input event rate of 100 kHz, and may need some parallelization and structuring to keep up with this rate. The algorithms to be implemented at level 2 are expected to achieve another rate reduction of a factor of ~100; examples are discussed below. For the 'third-level' trigger, one assumes that it can be implemented as a group of general-purpose processors, each of which is served a full event (at ~1000 events/second), and hence can execute any high-level code that allows a final data reduction in real time.

#### 4. Implementations of the first-level trigger (pp)

The most important detectors for which level-1 triggers are to be implemented at bunch crossing rate, for pp physics most likely the only detectors, are calorimeters and muon chambers. We have seen before that the triggering task is to identify high-pt leptons, among which electrons and muons are most prominent (tau-s are much more difficult to identify, as they have a very short lifetime and must be pieced together from their decay products). Gamma pairs and very high-pt jets or hadrons are an additional demand.

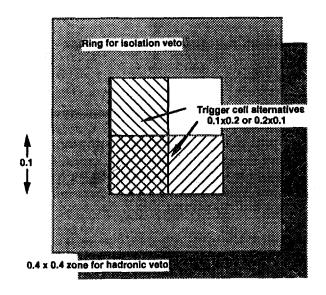

Calorimeters are built to provide the most characteristic signature of electrons and gammas, electromagnetic energy in a very concentrated region, with practically no leakage into the hadronic section behind. In connection with tracking chambers, electrons can be distiguished from gammas, and both can be discriminated against the gamma pairs from  $\pi^0$ -s, an important source of background. Calorimeters can also serve to recognize hadronic high-p<sub>t</sub> phenomena, single hadrons or jets, provided the window over which the trigger extends is broadened, and the hadronic cells, which in the electron case act like a veto, are included. Trigger thresholds, naturally, have to be tuned differently for the hadron or jet case.

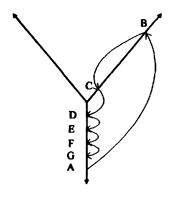

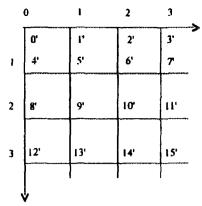

The implementation of the calorimeter trigger foresees typically a sliding trigger window of about 0.4 x 0.4 in  $\Delta\eta$  x  $\Delta\phi$ , inside which 16 cells (of 0.1 x 0.1 in the same coordinates) are accessible each for the electromagnetic and hadronic part. This implies integrating a number of original cells both in depth and  $\Delta\eta$  x  $\Delta\phi$ ,; the raw data in ATLAS are presently assumed to correspond, in the e.m. calorimeter, to three layers in depth and a cell size of 0.025 x 0.025. The summing up of cells into larger non-overlapping trigger cells is done by the frontend electronics. The 'sliding window' has to move by increments of 0.1 both in  $\eta$  and  $\phi$ , to avoid losses; due to the requirement of a 40 MHz rate there is no viable alternative to a parallel implementation. Each possible window has an associated 'trigger processor' realized as an ASIC, which must be provided the necessaray data in synchronization. Presently, a prototype implementation operating according to figure 2 below, has been demonstrated by the project RD27 in a test beam (see [4]).

Figure 2. Principle of first-level calorimeter trigger window

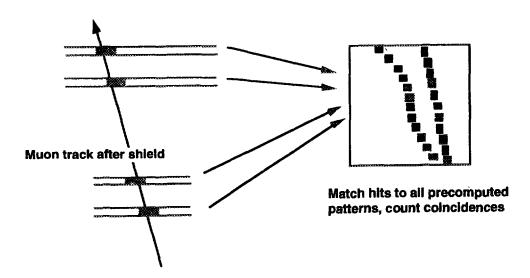

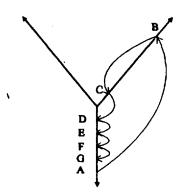

Level-1 muon triggers require the existence of fast tracking devices behind substantial shielding. They must provide, again at 40 MHz, hit patterns from which a pattern matching algorithm (implemented in custom-designed ASICs) can decide that hit combinations corresponding to a track have occurred. Compared to more detailed tracking algorithms in the inner detector, this algorithm must rely on coarser grain information so that the necessary fast parallel lookup tables remain of manageable size.

Figure 3. Principle of first-level pattern matching for muon triggering

#### 5. Structuring the second-level trigger (pp)

If in level 1 of the trigger, the limits of technology and the high repetition rate confine solutions essentially to ASIC implementations of crude algorithms known from past experiments, the second-level opens a much wider range of possible implementations. As shortcuts taken in the implementation usually translate into a less than optimal performance concerning biasses and losses, the implemented algorithms are crucial to the quality of physics. This is why we give level 2 here a somewhat more detailed coverage, although the available space does not allow us to enter detailed descriptions or discussions of algorithms. For more details, see [5-7].

Several guiding principles have emerged for the level-2 trigger, assumed to operate at 100 kHz or less. One of them is the fundamental Region-of-Interest (Rol) concept, very critical at least at high luminosity (viz. at high level-1 rates). The Rol concept relies on the level-1 trigger to identify those parts of the detector containing candidate features (electrons, photons, muons, jets). Only the data fraction in this candidate region (of the order of a few % of the total) is considered relevant and is moved to and used by the level-2 processors; the restricted readout alleviates the very stringent bandwidth requirements on providing data for algorithms from distributed buffers, at high frequency.

Simultaneously, the RoI concept considerably simplifies algorithms: local algorithms convert limited data from a single subdetector into variables containing the relevant physics message ('features'), in order to confirm or disprove a known hypothesis.

Another principle is to allow in level 2 for algorithms using full-granularity, full-precision data on all characteristic detectors. The extent to which data with full precision are effectively needed in level 2, will have to be the subject of future detailed physics-driven studies, and may even be dependent on the target physics. In general, the option for use of full data has to be provided for. Reducing the requirements on precision in the trigger will, of course, result in architectural simplification and cost savings.

A further guiding principle for all implementations is that any proposed or demonstrated hardware solution must be envisaged to hold for the entire detector, or at least for several detector components, apart from the usual constraints of flexibility, robustness, ease of control and maintenance. It also must be readily embedded in the overall data acquisition system. As we also want to rely as much as possible on commercially available components, and are dealing with a market that evolves fast and is not driven by our application, we will have to ensure that future technology improvements can be absorbed as easily as possible in the system, the limit being that some new technologies will, obviously, require architectural adaptation. These criteria translate into a maximum use of standard interfaces, and in particular the introduction of as few different components as possible (viz. detector-independent solutions).

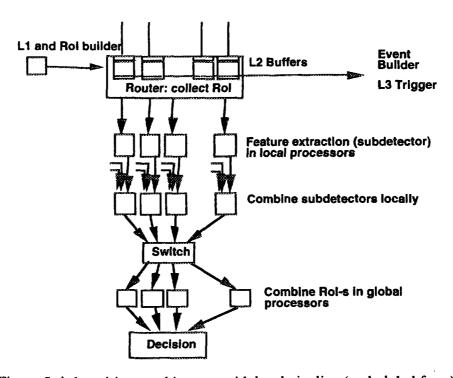

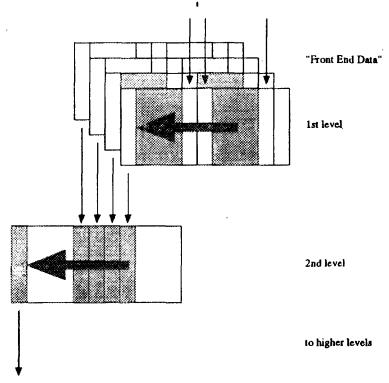

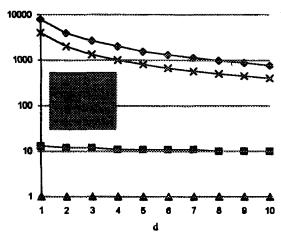

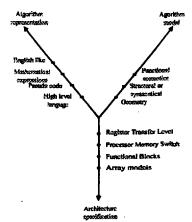

We can decompose the problem of second-level triggering in some detail, using as model the detector design as pursued in the ongoing work on LHC experimental proposals. This structuring of the problem is vital to limit the choices of transmission and processing technology, and to introduce the use of natural parallelism. The following paragraphs outline the overall functional decomposition of the level-2 problem, into three main phases, illustrated by figures 4 and 5.

Phase 1 consists of the buffering of level-1 (L1) selected data, and the collection of regions of interest. Raw detector data, after a L1 trigger has occurred, are naturally transmitted via cables or fibers, and collected in multiple local non-overlapping memory modules (chips, boards, crates), the L2 buffer. These memories need to hold full information over the duration of the L2 operation, the so-called L2 latency. For a data set representing a region of interest to become available, two functions must then be implemented:

- A device realized outside the L2 data stream has to indicate the whereabouts of regions of interest. This L1-guided unit is called a *Ro1-builder* and 'drives' the RoI collection. Note that this is true even for RoI-s that do not themselves actively participate in the L1 decision, like lower-threshold calorimeter clusters.

- The data pertaining to RoI-s have to be selected by some mechanism, which we term *RoI collection*. Detector-dependent differences will exist in the implementation, as substantial variety exists in the modularity and technology of collecting data in L2 buffers. All intended implementations could make use of the RoI parallelism, i.e. deliver data for different RoI-s simultaneously. This parallelism does not, however, match directly the parallelism of readout or L2 buffers: RoI-s do, in general, extend across the boundaries of buffers.

Phase 2 consists of 'feature extraction', i.e. of local processing of the data in a single RoI of a subdetector. On data collected for a single RoI, a relatively simple feature extraction algorithm can perform a local pre-processing function. Features are variables containing the relevant physics message, like cluster or track parameters that can contribute to corroborate or disprove the different physics hypotheses. The local algorithms are independent from other subdetectors and RoI-s, hence can exploit the natural double parallelism of RoI-s and subdetectors. Future simulation will have to show if and to which extent this simple concept has to be diluted (the fate of nearly all simple concepts), in order to avoid physics losses. This could be true in regions of overlap of detector parts (e.g. barrel/end cap), where each subdetector only has a weak signal.

Phase 3 is made of algorithms operating on the previously found features, to achieve a 'global decision making'. The physics features have to be collected from all subdetectors and from all RoI-s, for forming an overall decision on the entire event. The bandwidth requirements are substantially reduced by feature extraction, so that implementations of this phase have less of a problem with data transmission, although the trigger frequency of 100 kHz is, of course, unchanged. If one decomposes further the part of the algorithm dealing with multiple sets of features, the natural and efficient order of processing is to combine first all subdetectors that have 'seen' the same physics 'object', into decision variables which are again local (same RoI), and follow this by combining all RoI-s into an event decision, as shown in figure 5. While this is likely to be the most inviting algorithm strategy, it is by no means necessary (although possible and perhaps cost-effective) to express the strategy also by a corresponding implementation in separate and parallel processors. There is another natural parallelism which could be used, that of testing multiple physics hypotheses against the same set of data. It should be noted that the data set of independent features for detectors/Rol-s. has to be amended by derived quantities (e.g. effective masses for particle pairs).

#### 6. Implementation options for level 2

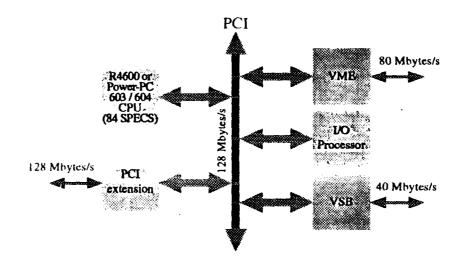

We have, so far, avoided discussing the hardware on which these level-2 algorithms or algorithm parts are to be implemented. In fact, basic choices exist that lead to quite different architectures. We will discuss here two overall options showing the basic choices in a pure way. Both of these are still under study and have specific advantages. We call them the farm-based and the data-driven architecture. Note that practical implementations are unlikely to follow such a pure solution for all detectors; hybrid implementations are quite possible and potentially the most cost-effective overall.

Figure 4. An architecture with local and global farms

The **farm-based** approach uses standard general-purpose processors and commercial network and communication components. The characteristic property of a farm is that at any given time, any processor may be busy with a full or partial event, while other processors deal with different events. This minimizes inter-processor communication and avoids detailed synchronization, but requires powerful mechanisms to purvey free processors in the farm with all the data necessary for its algorithm(s).

In the very simplest architectural scheme, as discussed in the CMS collaboration, processors are all grouped into a single farm, and are all connected to the entire set of potential data sources, the L2 buffers, via a switching network. A farm of this type can, of course, execute level-2 algorithms on partial data or level-3 processing on entire events, in the same architecture. Realistic estimates for the numbers of buffers talk about a thousand or more, and certainly several thousand processors will be needed; this leads then to a very demanding network technology.

The ATLAS decomposition into farms (shown in figure 4) follows more closely the above three phases: there are two layers of processors performing local feature extraction and global feature combination respectively. Local processors receive their data from intelligent devices in the L2 buffer, through a switching network. The global processors are organized as a single general farm; local processors may be run as one farm per subdetector, but groups of processors may also be permanently assigned to regions of the detector.

The data-driven approach uses low-level devices for ROI collection (sometimes called 'Routers'), directly coupled to (or inserted upstream of) the L2 buffers. Typically, these could be implemented as field-programmable gate arrays. Devices based on the same principle of low-level programmability, are also used as feature-extraction processors. Solutions based on field-programmable gate arrays have been shown ([8],[9]) to be able to satisfy the characteristic constraint applied to this solution, which is that processors operate in a pipelined mode capable of coping with the level-1 event rate of 100 kHz. This constraint obviates the necessity of event parallelism in a farm for phase 2. In figure 5, the network/farm approach is, however, kept for the low-bandwidth problem of global decision making.

Figure 5. A data-driven architecture with local pipeline (and global farm)

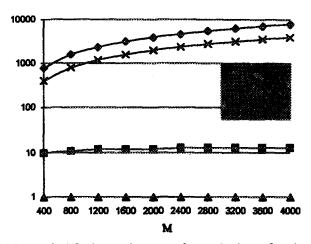

We do not presently understand enough about the elements of commercial farms in the various parts of the L2 trigger. Very first measurements seem to indicate that the market offers today components that seem not to permit an implementation of algorithms at 100 kHz, and extrapolations into the future are necessary. We have taken a benchmark suite of feature extraction and global decision algorithms, onto most of the market-leading processors, and measured execution times. The algorithms are conceptually optimized (e.g. making extensive use of look-up tables), and contain no system kernel overheads or interference with communication, nor the necessary 'service functions' like unpacking information or address manipulation (from 'local in readout module' to 'local in RoI' or 'global'). Feature extraction algorithms execute

typically in around a millisecond, first estimates for the neglected overheads are in the hundreds of microseconds. Global decisions take of the order of 200 microseconds on average (all times are given for the best available RISC processor). At a 100 kHz event rate, and for reasonable assumptions about the number of detectors and RoI-s, we can conclude that (with today's processors) a farm with several thousand processors will be required.

On communication and switching devices, theoretical and measured information on commercial equipment is available for HIPPI, used for transmission and switching between a few ports. Of the theoretically possible 100 Mbytes/s of HIPPI, 70 to 80% have been realized for transmission and over the switch (reported by experiment NA48). This does not include high-level software. HIPPI, however, does not look like a possible candidate in the long term, due to the bulky 32-bit-parallel cables limited to 25m length. On a preliminary installation with a Fibre Channel switch and several processors (up to five Power PC-s and HP 750-s were connected), transmission and setup characteristics were evaluated using a fully commercial path, including interfaces and software. Although the bandwidth for large packets is acceptable, high-frequency applications seem excluded without major software replacements, due to the long setup times of transfers (of the order of 500 µsec).

Early transmission results exist from RD24 for the prototype chips of SCI [10], but commercial availability is not yet given. For ATM, a fully commercial NetComm switch runs at a theoretical maximum of 12.5 Mbytes/s, of which a (strongly packet-size dependent) fraction only is achieved. Interpreting the measured NetComm rates for small packet size, a switching latency again in excess of 500 microseconds and substantial processor overhead may be inferred, but better understanding and more measurements are required. Newer hardware for ATM switches up to about 20 Mbytes/s has been realized and will be available soon. Both SCI and ATM for faster theoretical hardware speed have been simulated in quite some detail ([10],[11]), and could eventually become candidates for future farm implementations.

The above discussion was kept very polarised to general-purpose processors and switches on the one, field-programmable gate arrays on the other side. We have not done enough justice to the combined power inherent in digital signal processors (DSP-s), which have typically compute performances comparable to RISC processors, with added and properly integrated communication capability. DSP-s can be arranged into farms, but also into pipelined architectures, and their links allow constructing intelligent networks from them. They can constitute an ideal intermediate link between the 32-bit general-purpose processor and FPGA-s. Although some preliminary work has been done, no simple and cheap general solution based on DSP-s has been proposed today. Efficient interplay between communication and processing in DSP-s needs thorough understanding of the device's architecture and internal pipelines. In some DSP-s, links are also limited to short physical length.

#### 7. Experiments at the LHC at lower luminosity

The LHC is primarily built for high-luminosity and low cross section physics, but allows also to investigate other phenomena at lower pp luminosity, and in particular will also allow operation with heavy ions accelerated in both rings.

For B-physics in pp collisions, first proposals to build specific detectors have been made; that sector, however, is also covered in the proposals of CMS and ATLAS. One can assume a luminosity tenfold lower than assumed for prime physics, and use of the same detector components. The signatures relevant for the B sector, however, are quite

different, in particular the phenomena manifest themselves by leptons at much lower pt. This may require a partial rethinking of triggers. For instance, modifications may become necessary to the principle of RoI for B-physics; if a level-1 B-trigger detects a medium-pt muon, the need to corroborate the signature by low-pt (below 5 GeV/c) electrons may well result in a need for an unguided scan of a full tracking detector, as guidance from calorimetry can not be relied upon. If rates after the standard tools of level 2 (e.g. refinement of level-1 muons) are too high to go to level 3, a special full-detector search for candidates will become necessary. This is, of course, easier to implement in a farm-type or DSP-based solution than in a data-driven architecture.

For heavy ion physics, the event rate will be lower still, by orders of magnitude. In the proposal that is presently pursued [12], a collision rate of up to 4000 collisions/sec is assumed, which is level-1 triggered down to a few % of this rate by estimating the overall charged-particle multiplicity. At such rates, many stringent constraints of the pp experiments can be relaxed; e.g. data pipelining is not considered necessary, nor is there a complex multi-level trigger foreseen. On the other hand, heavy ion collisions are characterized by an extraordinary track density, like several thousand per unit of rapidity (as opposed to less than ten in pp collisions), leading to a data volume of from 20 to 50 Mbytes per collision, dominated by the fain-grain tracking device (time projection chamber). As of today, it is not foreseen to analyze these data in real time.

#### 8. References

- [1] Y.Baconnier et al., eds., The Large Hadron Collider Accelerator Project. CERN/AC/93-03, 8 November 1993.

- [2] CMS, The Compact Muon Solenoid, Letter of Intent, CERN/LHCC 92-3, 1 Oct 92.

- [3] ATLAS, A General-Purpose pp Experiment at the Large Hadron Collider at CERN, Letter of Intent, CERN/LHCC/92-4, 1 Oct 1992.

- [4] RD27, First-level trigger systems for LHC experiments, CERN/DRDC/93-32 (Status Report).

- [5] RD6: Integrated Transition Radiation and Tracking Detector for the LHC. CERN/DRDC/93-46 (Status Report); also J.Shank et al., Test beam performance of a tracking TRD prototype, Nucl.Inst.Meth. A309 (1991) 377.

- [6] G.Klyuchnikov et al., A second-level trigger based on calorimetry only, CERN/EAST Note 92-23 and ATLAS DAQ Note 007, 8 Oct.92.

- [7] K.Borer et al., A study of a second level track trigger for ATLAS. Nucl.Inst.Meth. A336 (1993) 59.

- [8] R.K.Bock, A.Gheorghe, W.Krischer, L.Levinson, Z.Natkaniec, A commercial image processing system considered for triggering in future LHC experiments, submitted to Nucl.Inst. and Methods.

- [9] D.Belosloudtsev et al., Programmable Active Memories in real-time tasks: implementing data-driven triggers for LHC experiments, submitted to Nucl.Inst. and Methods.

- [10] RD24, Application of the Scalable Coherent Interface to Data Acquisition at LHC, CERN/DRDC/94-23 (Status Report).

- [11] RD31, INEBULAS: A high-performance data-driven event building architecture, CERN/DRDC/93-55 (Status Report).

- [12] ALICE, A Large Ion Collider Experiment, Letter of Intent, CERN/LHCC/93-16. 31 March 1993.

# A STUDY OF ANALOG-TO-DIGITAL SLIDING SCALE CONVERTER UTILIZATION

Franco Maddaleno (\*) and Mario Rossi (#)

\* Politecnico di Torino

Dep. of Electronics C.so Duca degli Abruzzi 24 10129 TORINO - ITALY Tel ++39-11-564.4042 Fax ++39-11-564.4099

Email: MADDALENO@POLITO.IT

# Alenia Spazio

Turin Plant

C.so Marche 41

10146 TORINO - ITALY

Tel ++39-11-718.0256

Fax ++39-11-723.307

Email: MROSSI@ALSTO.ALENIA.IT

#### **Abstract**

The well-known Sliding Scale technique provides a statistical linearization of the Analog to Digital Converter, obtaining a high differential linearity. This technique sums at each conversion a known and uncorrelated variable signal (offset) to the analog input signal, and then subtracts numerically the offset from the conversion result.

Using this technique, a single conversion can have greater non linearity error than the straight conversion with no offset, but if the converted data are used to build histograms with a high number of events, the final accuracy of the center of gravity relevant to the histogram is better than the accuracy obtained by straight conversions. Moreover, the Sliding Scale technique shows the best advantage when the signals to be converted come with associated statistic phenomena, that is the case of X-ray events.

As a case study, a typical 12 bit A/D converter implementation is examined. In this system, the Sliding Scale function is obtained with an 8 bit D/A converter generating a discrete ramp signal (range value 0-255). This A/D converter is used to cyclically convert 8 multiplexed inputs: this arrangement can cause a beating effect, reducing the expected gain in differential linearity.

#### Introduction

This work has been originated by an analysis of an X-ray acquisition system to be used on an artificial satellite. During the analysis, some design misconceptions were discovered, which are pointed out in this paper. Although Sliding Scale Converters are used since a long time, in some cases design misconceptions can still occur.

The A/D converter to be analyzed is the main component devoted to the analog to digital conversion of science data. The energy spectra construction is the main purpose of the A/D converter that shall introduce as few errors as possible. This means that the A/D converter needs as a main characteristic an high differential linearity. The limitations due to the need of using qualified devices narrow the set of possible circuit that can be used for the system.

In order to improve the characteristics of the available and qualified A/D converters, the design solution is the use of the Sliding Scale technique that provides a statistical linearization of the A/D characteristics.

#### **Sliding Scale Principle**

The Sliding Scale Converter technique has been invented in order to overcome the differential non linearities of the A/D converters [1]. This is a statistical correction, i.e. it works only for a large amount of data: the single conversion can have an error greater than the error obtained without the Sliding Scale. However, if the converted data are statistically processed, as in a histogram, then the statistical properties of the histogram, (for example the center of gravity) are better determined by the Sliding Scale technique [2]. An X-ray

analyzer, which typically must measure the energy spectra of X-ray emission, can present dramatic precision improvements, provided that the Sliding Scale technique is correctly used.

The Sliding Scale principle is based on a simple idea, explained by this example: in order to measure a rod length with a scale having non linear errors, one has to perform many measurements, sliding randomly the rod on the scale, and taking each time the difference between the two rod extremes. The corrected value is obtained by averaging the different results. Of course one must not slide the rod moving an extreme over the end of the scale.

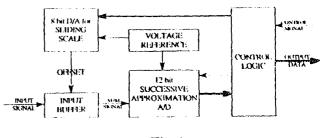

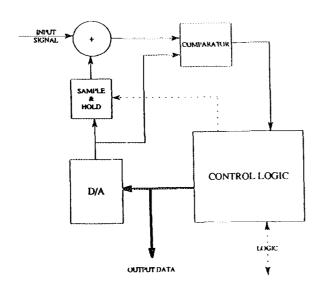

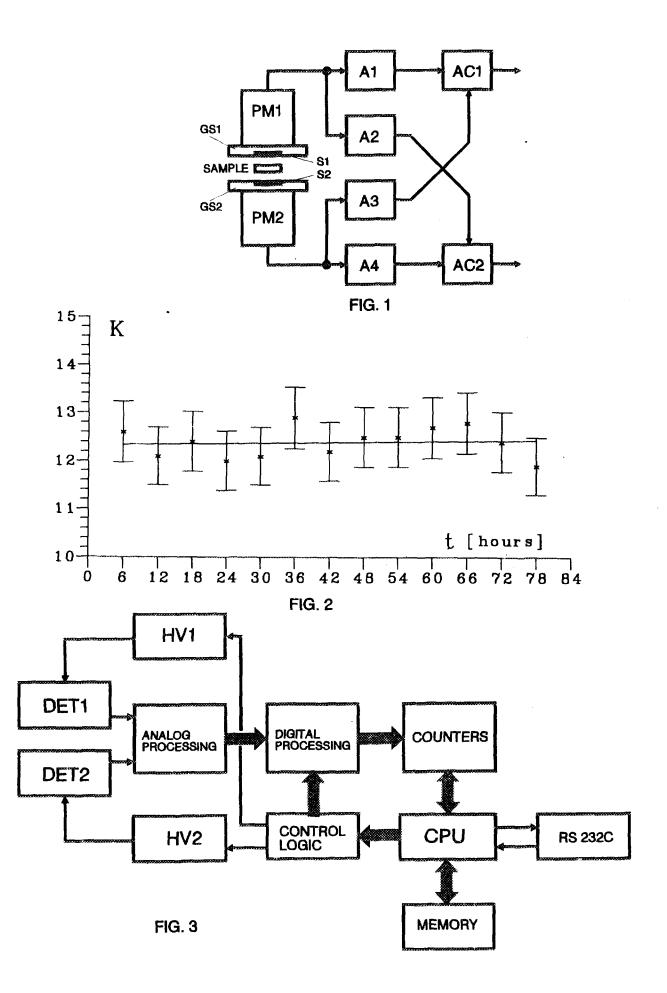

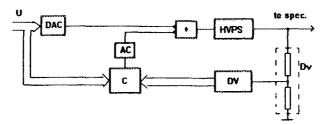

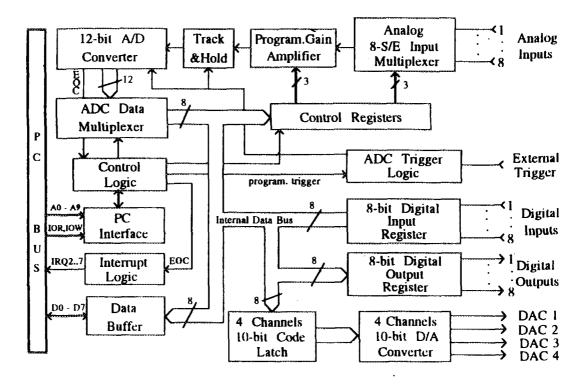

In a data acquisition system, the operation of sliding the voltage to be measured is accomplished by a D/A converter whose input is a "random" number. After the A/D conversion, this slide value is numerically subtracted from the result. A block diagram of a sliding scale converter is shown in Figure 1:

Fig.1

The control block provides for each conversion a new value to the D/A converter, and then subtracts it from the A/D converter output in order to get the conversion result.

This technique works if the following conditions are satisfied:

- 1) The added offset is uncorrelated to the input signal; a real random value could be used, but an uncorrelated deterministic signal is simpler to generate;

- 2) After each acquisition, a sufficient number of samples must be present in each bin;

- 3) The electrical amplitudes of LSB in A/D and D/A converters must be equal.

The maximum non linear error that can arise from a single conversion is given by the sum of A/D and D/A specific non linear errors. If multiple samples are taken, the non linear error decreases due to the averaging effect, depending on the number of different offset values, i.e. on the number of bits used by the Sliding Scale D/A converter.

A histogram obtained with this technique, presents a better shape (no false double peaks), and a more accurate centroid position. On the other hand, the histogram width (that is its variance) is increased, due to the addition of the random variable.

If m bits are used for sliding the input voltage, a maximum decrease of  $2^{-m}$  on the system differential non linearity can be expected. The system non linearity is principally given by the differential non linearity of A/D converter added to that of D/A converter. The sliding scale technique works if at least an order of  $2^m$  measures are carried out for a constant input. In case of a distribution, each bin must contain at least about  $2^{2m}$  / DNL samples, were DNL is the differential non linearity of the used A/D converter.

#### A/D Converter Implementation

Analog to Digital Converter adopted in the science instruments is constituted by a 12 bit Successive Approximation A/D converter with the sliding scale technique.

The previous listed conditions has been met with the following design choices:

- The first condition has been fulfilled, applying, as offset, a ramp signal that is statistically uncorrelated from the input signal. The input signal is the energy signal produced by the detector system, that is completely random.

- The second condition depends on the user: he/she must guarantee a high number of events for each significant bin in the histogram (see above).

- The third condition has been satisfied using the same voltage reference for both A/D and D/A converters, and using only the 8 most significant bits of a 10 bit D/A converter.

The analog gain error of the D/A converter is convolved with the real distribution: as a consequence, a constant input (monochromatic line) is represented by a wider distribution and the centroid of the obtained data doesn't represent the line position, because a systematic error is added to the input data.

The A/D sliding scale converter is constituted by the following blocks:

- Input buffer receives the analog input signal, adds to this signal the offset signal and subtracts the offset adjust signal. This block is constituted by an operational amplifier that provides an high input impedance and a fast settling time allowing a fast time conversion.

- DAC for sliding scale: this DAC is a 10 bit current output, that provides the offset signal. Only the 8 most significant bits are used for the sliding scale function, obtaining an error reduction on its non linearities.

- Successive Approximation A/D, implemented by a 12 bit high speed ADC, performs the sum signal conversion in about 5 μs..

- Control Logic, implemented by a FPGA, performs the sliding scale control, provides the digital data result in a latch register with three state output and provides, under external activation, the automatic offset adjust function. The logic performs the following steps:

- 1. subtracts to the converted 'sum signal' the digital code corresponding to the analog value previously added by the DAC.

- 2. store the result in the output latch register

- 3. update the sliding scale DAC incrementing the code.

The offset is a ramp signal, generated by a 8 bit counter, that is incremented for each conversion. When the ramp signal reaches to the maximum value N<sub>MAX</sub>, the counter is reset and repeat the counting.

- Voltage reference, an high stability voltage reference, provides the -5V reference to the successive approximation ADC, the +5V reference to the DAC. An excellent voltage reference accuracy is necessary to ensure a good offset signal accuracy.

#### **System Architecture Analysis**

The case study here presented deals with a problem of multiple input conversion. Two different ADC applications will be examined. In both cases, the same A/D subsystem, previously described, is used.

In the first application, for each X-ray detection (event) 4 or 8 different analog voltages must be converted, depending on the operating mode chosen by the human observer.

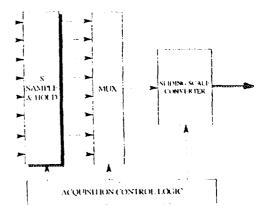

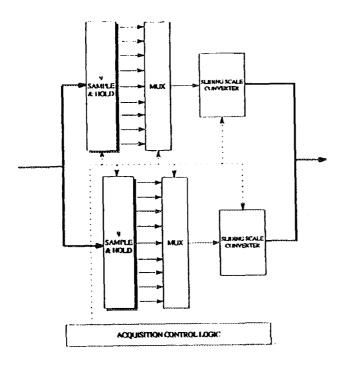

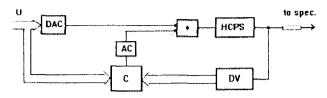

The system designer chose the approach shown in figure 2.

THE 2 TIRST AND STIDING SCALE CONFIGURATION.

The 8 input signals are sampled at the same instant, and then routed to a multiplexer which cyclically connects the various inputs to the A/D subsystem, with Sliding Scale correction. The same A/D converter performs, for each received event, 4 or 8 consecutive conversions with the same order.

The Sliding Scale control generates a discrete ramp (input signal to DAC from 0 to 255), so every input signal i is summed by an offset numeric value equal (8\*k+i) mod 256, where i is the input channel and k is an integer: for example starting with the Sliding Scale register reset, the first of the eight input signals has as offset the value 0, 8, 16, 24, 32 ... while the second line input has 1, 9, 17, 25... A beating effect between number of converted line input and number of offset happens. In this condition, the Sliding Scale improvement is reduced because to each input channel only 32 different "random" values are averaged.

Moreover, the non differential linearity of the

D/A converter usually depends on the internal resistive network (R-2R), so the error could be periodic and the statistical correction could not work properly. In this case, the statistical independence between input signal and offset is not completely verified.

Finally, in the specific implementation, the 8 input signals are not statistically independent because some of them are obtained by an analog processing: in this case the statistical independence between the input signals and the offset could be violated.

In the second application, 9 input channels must be cyclically converted for each event. This instrument however must also recognize and measure the so called double event, constituted by two sets of analog voltages to be converted with very short time differences ( $< 40 \,\mu s$ ). The architecture solution chosen by the system designer is shown in figure 3.

FIELD SECOND AND SLIDING SCALE CONFIGURATION

During single events, only the first conversion chain works. In case of double event, the second one is sampled and converted by a second chain, identical to the first. The drawback of this solution should be obvious. The second chain works only for the second event in case of double event. This occurs only sporadically, and few measurements are carried out by the second chain. This fact decreases the linearization capability of the Sliding Scale technique, because it is based on averaging. Moreover, when the set of second events is processed and compared with the corresponding first events, a difference on offset and gain between the two conversion chains could generate a difference on statistical parameters between the two distribution (mean value and width). To overcome this problem, automatic offset correction and gain calibration have been provided.

#### Measurement results

Measurements have been carried out by the manufacturer after the circuit construction, and few supplemental tests have been done by Alenia Spazio. The differential non linearity has been evaluated using a slow ramp applied after the multiplexer, bypassing thus the indicated problems. The obtained results indicate a perfect agreement with the theory: a total differential non linearity error of A/D and D/A converters of about 1.3 LSB should reduced by a factor 28; the measured residual non linearity is about 0.005 LSB. This value is asymptotically approached after a very high number of conversions per bin (order of 105), as predicted.

A test for observing the multiplexing interaction with the Sliding Scale converter has been carried out on the first instrument by applying to the 8 inputs the same DC voltage, and collecting on a file the conversion results. The data for each input have been divided in three or four bunches, and the average value has been computed: this way the noise effects

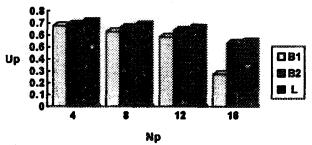

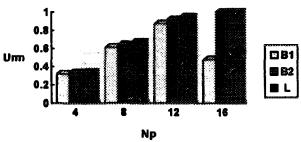

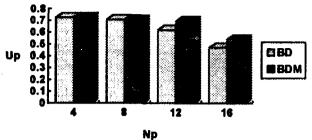

have been reduced. The results are shown in figure 4, where on horizontal axis is indicated the input channel number.

Figure 4. Average values with constant inputs.

A correlation among the different curves is visible: for example the values read by channel 7 are systematically higher than the same voltage read by channel 8. The probable reason of this behavior is that the 32 different offsets added by the Sliding Scale D/A converter to the input 7 have in average a lower value than the offsets added to the following channel. The raw data for this measurement have been obtained with 8 bit only, because the application requires only a low resolution.

More detailed measurements using a ramp or a triangular wave for the direct evaluation of the differential non linearity error, up to now have not been allowed. Some preliminary measurements indicates that the differential non linearity is better than 0.03 LSB but the short time allowed for the tests didn't let us to collect a sufficient number of data for a more precise evaluation.

#### Improvement Proposals

The proposals for improving the presented conversion systems and to correct the architecture are here described.

The loss of linearizing capability due to the multiplexing can be easily fixed by adding a ramp going from 0 to a maximum value  $N_{MAX}$ -1 such that the number of inputs to be cyclically converted is a prime divider with respect to  $N_{MAX}$ . This can be done in a FPGA designing a counter modulus 254 instead of 255 (for the 8 input case). Another solution for the same problem consists in keeping the same sliding value for each set of 8 conversions.

A last solution is the use of a (pseudo)random number generator (based on a shift register dividing in a Galois Field) which has the same cost in terms of flip-flops than a standard counter, and generates pseudo-randomly all values from 1 to 255; in this case however there are possible beating problems with the second instruments, due to the fact that 9 (conversions) and 255 (generator period) are not reciprocally prime.

The second problem discovered, related to the double event measurement, can be fixed by a change on the control logic, which should use alternately the two conversion chains, regardless if the detected event is a single or a double event.

The previous proposals have zero cost, because they require the reprogramming of an FPGA. An improvement of different nature, which works on any Sliding Scale converter, but requiring a more complicated circuitry is described in the following.

From simulation, a better statistical linearization is obtained if the D/A converter contained in the A/D successive approximation converter is used also for the generation of the Sliding Scale offset, as shown in figure 5.

Fig.5 EMPROVED SLIDING SCALE.

This approach has the obvious advantage of having the same LSB amplitude for both the converters, as required by the Sliding Scale technique, and provided that the analog circuitry is precise. Moreover, this solution has also a less obvious advantage in terms of statistical corrections, due to the correlation between the non linearity errors of the A/D and D/A converters. This solution however requires a sample and hold circuit to store the analog value to be added to the analog input signal.

In this approach, the control logic at the beginning of the conversion must generate the "random" offset signal, and then execute the successive approximation algorithm to carry out the conversion.

#### Conclusion

The Sliding Scale linearization technique of a A/D converter has been briefly examined.

Then, as a case study of application, the results of an analysis have been presented. In two applications, designed for X-ray analysis, architectural choices leading to a loss in precision have been pointed out. Measurements confirmed the possible problem. Some simple actions for curing the problems have been proposed.

Finally, a possible alternative architecture for general purpose Sliding Scale converters is indicated.

#### References

[1] C. Cottino, E. Gatti and V. Svelto, A New Method for Analog to Digital Conversion, Nucl. Instr. and Meth. 24 (1963) 241-242.

[2] E. Gatti and S. Cova, The Quantization Cell Profile: a Useful Concept for a Deeper Insight in Analogue to Digital Conversion, Proc. of International Conference on Measure Systems and Distributed Processing, Univ. of Pavia (Italy), Oct 15-16 1979, 121-131.

## Fast Low-Noise Monolithic Charge Sensitive Preamplifiers IC for Hadron Calorimeter

M.A. Baturitsky, V.A. Chekhovsky, I.F. Emel'yanchik, N.M. Shumciko

The National Scientific and Educational Centre of Particle and High Energy Physics at the

Byelorussian State University.

M. Bogdanovicha street, 153. Minsk, Belarus, 220040 I. A. Golutvin, N. I. Zamvatin

Joint Institute for Nuclear Research, Dubna, Russia, 141980

O. V. Dvornikov

Information Technology Center, P.Brovki street, 6, Minsk. Belarus, 220600

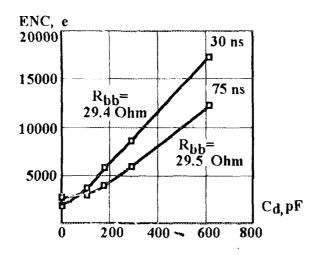

A low-noise fast monolithic charge-sensitive preamplifier in one-channel and four-channel versions is designed. It has 3.5 ns rise time for input detector capacitance  $C_d = 0$  and 8ns for 100pF and approximately 8mW power dissipation for 5V supply voltage. The ENC performance at shaping time  $30 \ ns$  is 1350e + 17e/pF for  $C_d$  up to  $600 \ pF$ . Crosstalks in a four-channel amplifier made in the same chip were measured equal to about -16dB for Cd = 100pF.

#### Introduction

High luminosity of Large Hadron Collider and large number of readout channels set stringent requirements to front-end electronic of CMS. Our main goal is to use advantages of monolithic technology for design and production of the fast charge sensitive preamplifier (CSP). The CSP integrated circuits for a readout channel must be compact enough, cheap and suitable for mass production. It was designed for silicon calorimeter of CMS project, but our IC can be used in some other tasks where high speed and low noise performance are necessary.

Our CSP ICs have been tested at CERN together with avalanche photodiodes in the prototype of copper/scintillator hadron calorimeter in July, 1994.

#### Design goals

Design goals of our CSP were the next:

- High speed. Rise time of output signal has to be about 7ns.

- Low noise. Equivalent Noise Charge (ENC) has to be  $3800c^-$  at shaping time  $T_m = 30ns$  and detector capacitance  $C_d = 100pF$ .

- Power consumption less than 10mW per channel.

- Minimum number of external elements.

- Maximum output voltage swing 2V.

#### The CSP IC description

We can present now two versions of fast low noise CSP ICs: one-channel and four-channel ones.

The main characteristic of the CSP ICs are:

- ENC performance at shaping time 30ns is  $1350 + 17c^{-}/pF$  for detector capacitance up to 600pF. The mean value of ENC for  $C_d = 100pF$  equals  $-3600c^{-}$ .

- The best sample has 3.5ns rise time at  $C_d = 0pF$  and 7ns for  $C_d = 100pF$ . The slew rate is about  $200V/\mu s$  for large signal. The CSP operates at voltage supply  $V_{cc}4.5...10V$  with power dissipation 8mW for 5V.

- Linear output voltage swing is 1V for  $V_{cc} = 5V$ .

- Crosstalks in the four-channel CSP IC were measured to be about -46dB for  $C_d=100pF$  and  $V_{cc}=5V$ .

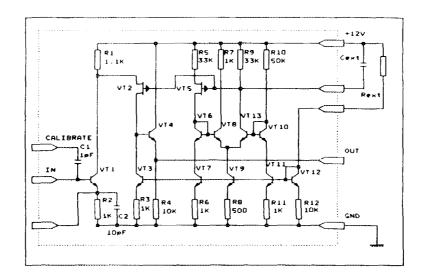

Fig.1. The electric circuit of the CSP

The CSP circuit is shown in Fig.1. It consists of a folded cascode (BJT VT1 + JFET VT2) followed by an emitter follower VT4. A biasing circuit VT5...VT12 stabilizes operation point of VT2 and sets operation current of VT1 with an external resistor  $R_{ext}$ .

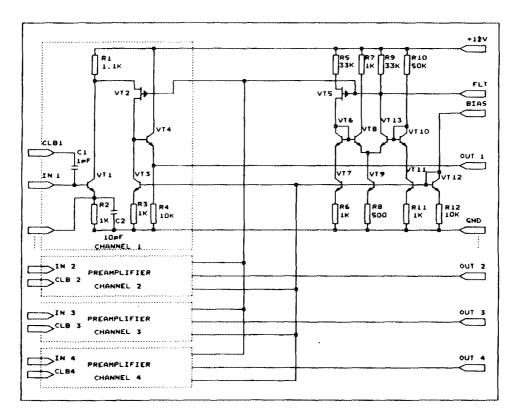

Fig.2. The 4-channel CSP

The four-channel version has the same circuitry and is shown on Fig.2. The biasing circuit is shared by the four channels. There are four integrated capacitances at the inputs to provide the ability of electrical calibration.

#### **ENC** estimation

The total ENC (1) may be considered to consist of the next five components (2)...(6) [1]

$$ENC^{2} = ENC_{1}^{2} + ENC_{2}^{2} + ENC_{3}^{2} + ENC_{4}^{2} + ENC_{5}^{2},$$

(1)

$$ENC_1 = \frac{e}{2q}(C_d + C_f + C_i)\sqrt{\frac{kT}{T_m g_m}}, \qquad (2)$$

$$ENC_2 = \frac{e}{2q}(C_d + C_f)\sqrt{\frac{2kTR_{bb'}}{T_m}},\tag{3}$$

$$ENC_3 = \frac{e}{2q} \sqrt{q T_m I_b}, \tag{4}$$

$$ENC_4 = \frac{e}{2q} \sqrt{q T_m I_d}, (5)$$

$$ENC_5 = \frac{e}{2q} \sqrt{\frac{2kTT_m}{R_p}} \tag{6}$$

where

$ENC_1$  is a series mean squared equivalent noise charge dependent on the transistor transconductance;  $ENC_2$  a series mean squared equivalent noise charge caused by the base spreading resistance;  $ENC_3$  a parallel mean squared equivalent noise charge caused by the input current of the CSP;  $ENC_4$  a parallel mean squared equivalent noise charge generated by the detector leakage current;  $ENC_5$  a parallel mean squared equivalent noise charge due to the detector biasing circuit and the CSP feedback resistor;  $C_f$  is the feedback capacitance;  $C_i$  the input capacitance of the CSP; e = 2.718;  $g_m$  is the input transistor's transconductance;  $I_d$  the detector leakage current;  $I_b$  the CSP input transistor base current;  $R_p$  the resistance of parallel connection of feedback resistor  $R_f$  and detector bias resistor  $R_f \parallel R_p'$ , assumed in what follows  $R_p = R_f$ ; k is the Boltzmann constant; q electron charge;  $R_{bb'}$  base spreading resistance of BJT transistor; T the temperature;  $T_m$  the shaping time.

Because of high counting rate of incoming events in the LHC collider experiment the shaping time of the preamplifier output signal has to be very short. Consequently the series noise of CSP is the main source of noise. So the npn bipolar transistor is suitable for this task. It also permits to use combined microwave BJT-JFET technology to fabricate high speed preamplifiers. The technology permits to produce input npn BJTs with  $f_T > 3.0 GHz$  and  $\beta = 200$ , and MOSFETs with  $f_T = 300 MHz$  placed in any part of a chip.

Preliminary estimations of  $R_{bb'}$  made from ENS measurements gave value 6Ohm. With respect of this fact and the influence of d = 100pF the first term equals  $|ENC_1| = 1200e^-$ .

The collector current was chosen taking into account the condition

$$ENC_1 = ENC_2, (7)$$

approximately satisfied for  $I_c = 2.5mA~(ENC_2 = 1250e^-)$ . The detector leakage current contribution  $ENC_4$  is neglected because it doesn't depend on the preamplifier merit. The contribution caused by parallel noise  $(ENC_3, ENC_5)$  doesn't exceed  $2100e^-$  with respect of the input transistor current gain about  $\beta = 200$  and feedback resistance 100kOhm.

The total level of input noise according to our estimation with  $C_d = 100pF$  and  $T_m = 30ns$  equals ENC = 2900 electrons.

The dependence of ENC versus  $C_d$  for  $T_m = 30ns$  and 75ns is shown in Fig.3. The measurements were carried out for  $I_c = 2.5mA$ ,  $C_f = 3.3p$ , and input charge  $Q_{in} = 10fC$ . The measured value of  $R_{bb'} \approx 30Ohm$  as may be seen from the picture. This fact explains the greater level of series noise compared with the preliminary estimation.

Fig.3. Noise performance of the CSP IC

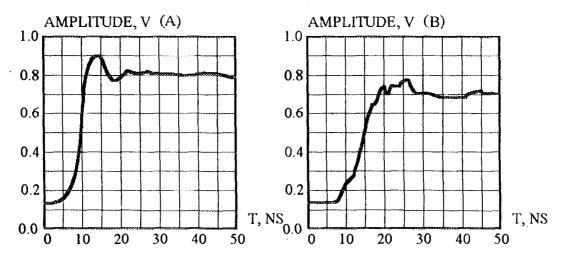

The output voltage rise time equals 3.5ns and 8ns that corresponds to the slew rate approximately  $200V/\mu s$  and  $80V/\mu s$ , respectively.

Fig.4. The CSP output signal: a)  $C_d = 0pF$ ,  $T_r = 3.5ns$ ; b)  $C_d = 100pF$ ,  $T_r = 8.0ns$

#### Conclusion

In conclusion it may be said that a new version of four-channel CSP with more wide functional abilities is under development now. The new chip will require minimum number of external elements, the feedback resistor and capacitor will be integrated into the chip. It will contain a summing network and a shaper CR-RC with  $T_m = 30ns$  and externally controlled voltage gain.

#### Reference

1. M.A.Baturitsky et al., Charge Sensitive Preamplifier IC for Silicon Calorimetry at Colliders, Nucl. Instr. and Meth., to be published.

### The Front-end Electronics and the Data Acquisition System of the FOBOS $4\pi$ - array

O.V. Strekalovsky, K. Heidel, S.I. Ivanovsky, D. May, H.-G. Ortlepp, G. Pausch, G. Renz, V.E. Shuchko, W. Wagner, V.V. Trofimov, I.P. Tsurin

Joint Institute for Nuclear Research, Dubna

#### Introduction

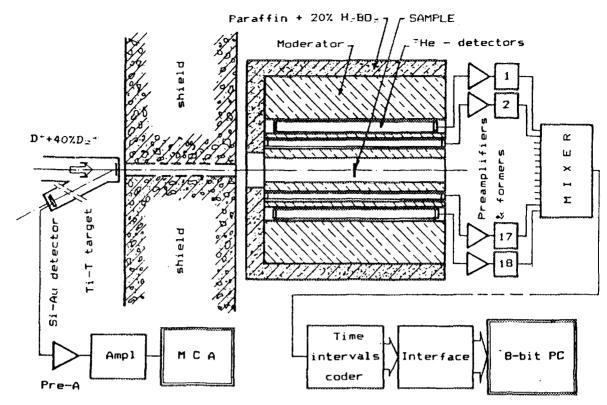

The FOBOS [4] spectrometer at Flerov Laboratory of Nuclear Reactions in Dubna is intended for heavy ion reaction studies in the bombarding energy range of 10...100 AMeV. It consists of a "gas ball" of 30 position-sensitive avalanche counters (PSAC) and 30 Bragg" axial ionization chambers (BIC) behind them. A shell of 210 CsI(Tl) scintillation counters surrounds the gas ball. As forward detector 92 phoswich detectors of the ARGUS array [2] are foreseen.

The counters are arranged in 30 modules placed on the facettes of a polyeder (12 regular pentagons and 20 regular hexagons). Two pentagons are used for the beam input and exit, the last containing also the forward detectors in an extended cone.

The first experiments with the FOBOS multidetector array have been started last year. They are directed to study the fission process of nuclei as in the case of cold fission in <sup>244</sup>Cm(sf) as at the heavy ion beam of the cyclotron U-400M. In these experiments especially developed electronics and a new VME based data acquisition system came into operation. All components are closely appropriated to the special features of the FOBOS detectors.

#### The Position Sensitive Avalanche Counter Channel

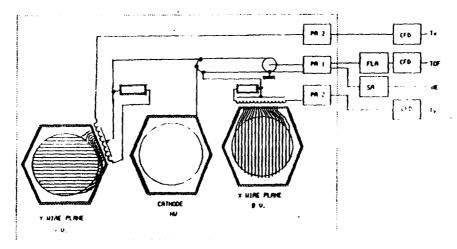

The PSAC's are based on the principles described in [3]. One cathode foil delivers the timing signal and two anode wire planes connected to delay lines serve as coordinate grids.

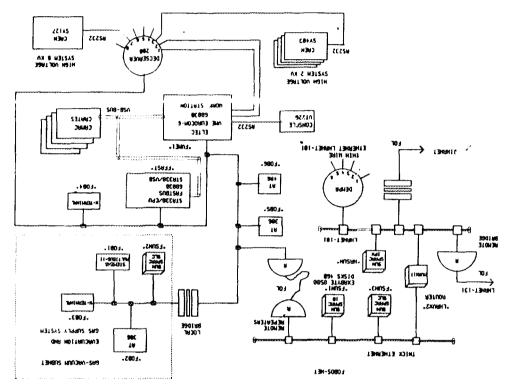

Fig. 1. Read-out principle of the position sensitive avalanche counter

The two lines with 1.4 ns/mm specific delay and  $560\Omega$  impedance are matched with resistors at one end and coupled to readout amplifiers 5027-30 with  $560\Omega$  "cold" dynamical input resistance and 350 fold current amplification at the other end. The negative detector bias is fed to the cathode. The cathode readout circuit delivers an 80 fold amplified (Avalanche-Counter-Amplifier 5027-40) current signal for timing and a charge signal of 150 mV/pC sensitivity for pulse height analysis.

The timing signal is directly fed into a trigger. All channels are protected against damage in the case of spark discharges in the gas. The circuits are placed directly on the counter frame.

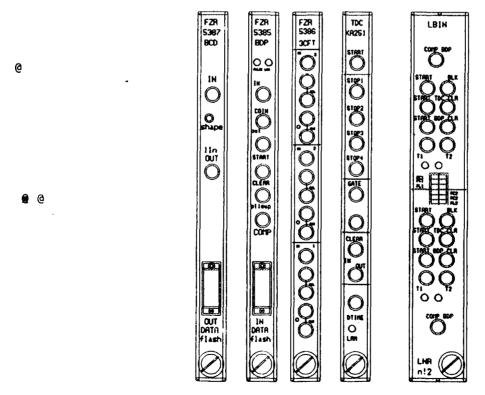

The three constant fraction discriminators (CFD) are housed in one CAMAC module FZR 5386 (fig.4). Their thresholds are CAMAC-controlled. The high dynamic range (1000:1) allows to cover all experimental conditions without changing the amplification factor of the preamplifiers. The delay necessary for the zero crossing formation must be implemented by an external cable. The time walk amounts to  $\pm 50$  ps for step pulses of 2 ns risetime in the range 10 mV to 2V.

#### The Axial Ionization Chamber Channel

The axial ionization chambers cover cones of  $\pm 13.8^{\circ}$  and  $\pm 17.4^{\circ}$  with entrance window diameters of 285 mm and 385 mm, respectively.

The field shaping is performed by copper strips coated every 5 mm on a teflon insulator cone. The voltage divider provides equal potential steps, e.g., a homogenious field. The Frisch grid consists of two perpendicular planes of 1 mm spaced  $50\mu m$  thick CuBe wires. The anode placed 10 mm behind the Frisch grid is made of  $10\mu m$  aluminized mylar which may be penetrated by light charged particles to be registered in the scintillation counters. At a gas pressure of 100 kPa an anode potential of + 8kV is necessary (the entrance window acts as cathode and is grounded). The electron drift time of up to  $4\mu s$  would cause large ballistic deficit in the case of conventional pulse shaping.

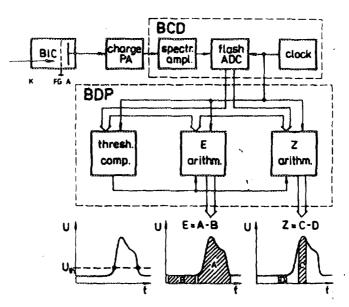

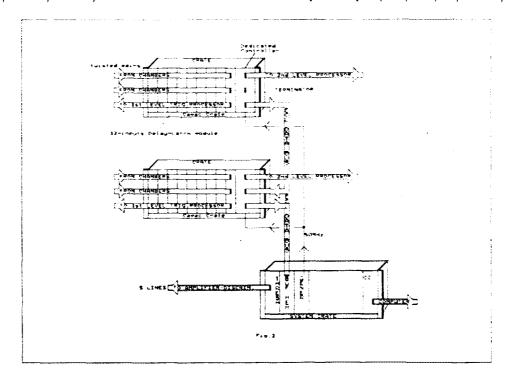

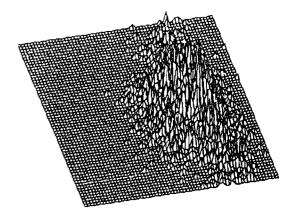

Therefore a digital processing method [4] is utilized which derives the energy and Bragg peak height from digitized signal samples. The principle is illustrated schematically in fig.2. The read-out system for BIC consists of a charge sensitive preamplifier 5027-10 and two CAMAC modules, the Bragg-curve digitizer BCD 5387 and the Bragg digital processor BDP 5385.

The Bragg-curve signal, shaped by a spectroscopy amplifier with short time constant  $0.2/0.4~\mu$  s is digitized by an 8-bit flash ADC with a quartz stabilized sampling frequency of 10 MHz. If a signal is recognized by the threshold comparator, the two arithmetic units, calculating E and Z are activated. The algorithms are schematically shown in the bottom of fig. 2.

Fig. 2. Principle of the new signal processing method for Bragg peak spectroscopy

The shadowed areas indicate sums of digitized values. A digital comparator determines the threshold for pulse recognition and a pile-up inspector rejects erroneous results. The

control of the working conditions and the data transfer is performed via the CAMAC dataway. The control logics, not shown in fig. 2, implements the coincidence conditions with the DGAC, the pile-up inspection and the connection with the first level trigger logics. The digital processing system is faster than the classical one by a factor of 10 and very simple to operate.

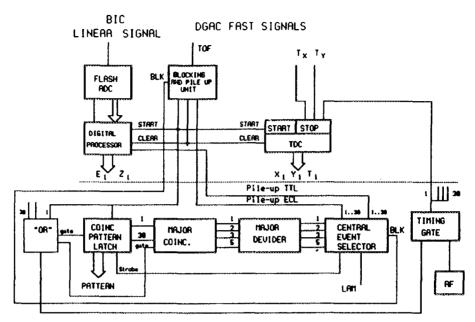

Fig. 3. Front-end gas detector module and part of the first level trigger

#### The First Level Trigger

The DGAC TOF signals pass a blocking and pile-up unit (fig.3) connected with the control logics of the BDP, if the BDP is free and reach the coincidence pattern register KR13K [5].

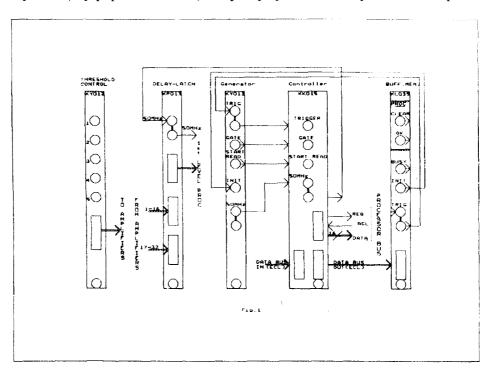

Fig. 4. CAMAC modules developed for FOBOS

The pattern is analyzed by a majority coincidence unit KL360 [6], the outputs of which are connected with the central event selector. If the multiplicity condition is fulfilled and there was no pile-up signal, the central event selector indicates a "good" event and sets LAM.

To provide effective pile-up rejection the following conditions must be fulfilled to allow an event for registration:

- no avalanche counter signal  $12\mu s$  before and  $6\mu s$  after the event,

- no threshold comparator responses in  $10\mu s$  before the event,

- trailing edge of the threshold comparator is within a certain time window relative to the avalanche counter signal.

The computer first reads the coincidence register and then the conversion results of the fired TDC's and BDP's. Then the blocking signal is removed and the system is ready again.

#### The Scintillation Counters Channels

The avalange counters and ionization chambers are not sensitive to low ionizing high energetic light charged particles (LCP). Therefore a shell of 210 CsI(Tl) scintillator counters was decided to be arranged behind the gas detectors.

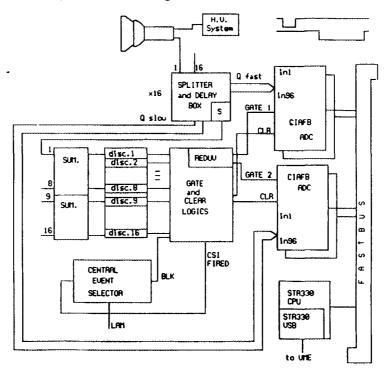

Fig. 5. Block diagram of the CsI(Tl) counter readout system

Figure 5 shows a diagram of the electronics for CsI(Tl) detectors. The anode signals from the photomultipliers are splitted via a passive splitter-and-delay-box into the "fast" and "slow" branches. The signals in the "fast" branch are delayed by 200 ns delay line chips FLOETH PD24-20051D. The branches are connected directly from the splitter to their respective F683C CIAFB ADC. The CIAFB [7] is a 96 channel 12/15 bit gated charge integrating ADC housed in a single width FASTBUS module. The Gatel for  $Q_{fast}$  (400ns) and Gate2 for  $Q_{slow}$  (2 $\mu$ s) are delivered by a REDUV gate and delay generator [8].

Each of the 16 splitter and delay boxes provides a sum signal for its 16 channels, which is fed via a buffer to a discriminator. From the discriminator outputs a simple first level trigger signal is derived and fed into the Gate and Clear logics.

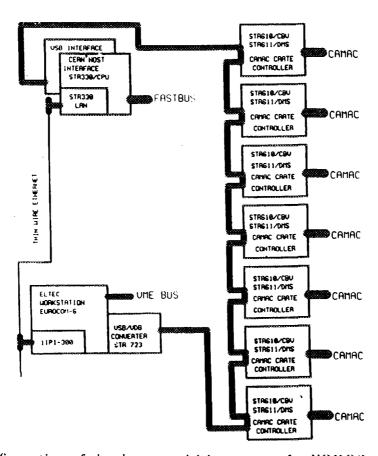

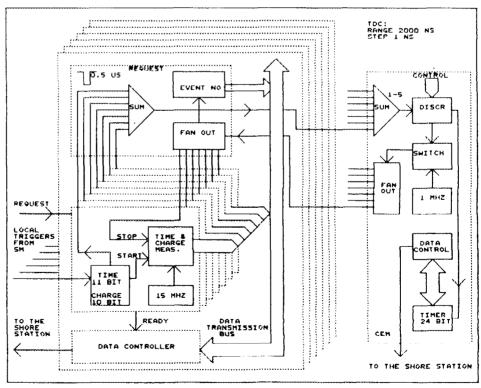

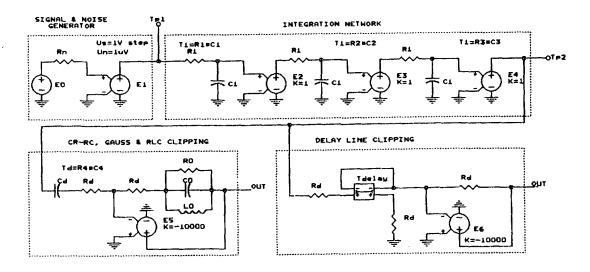

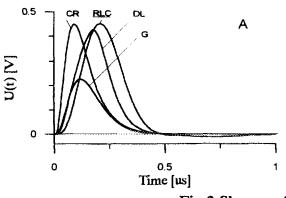

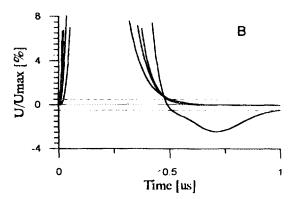

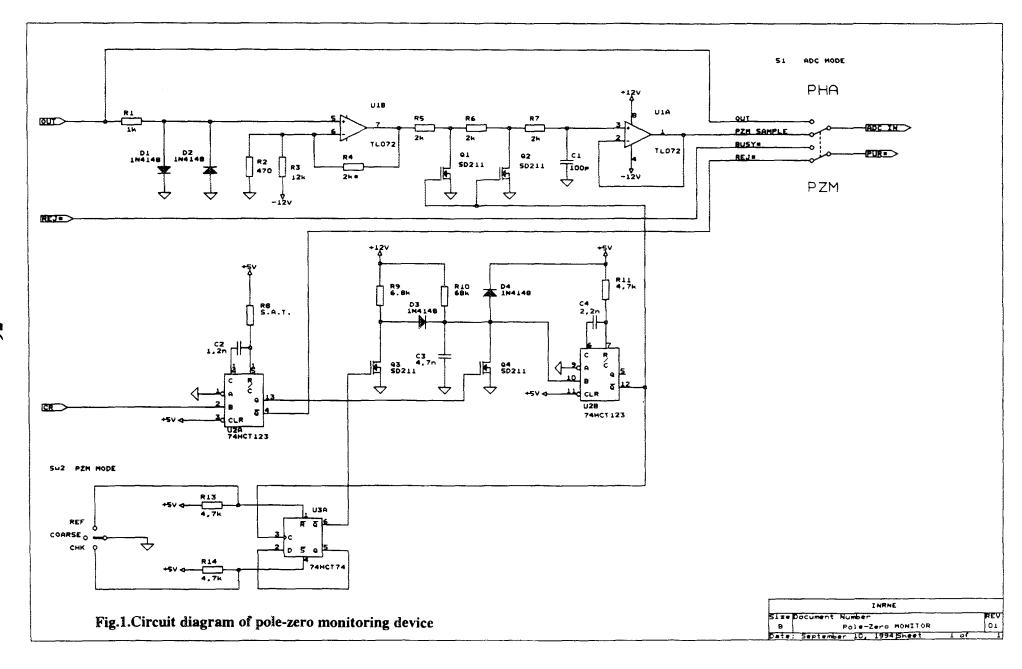

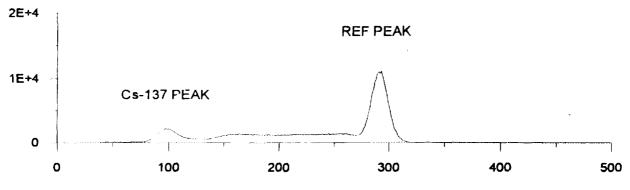

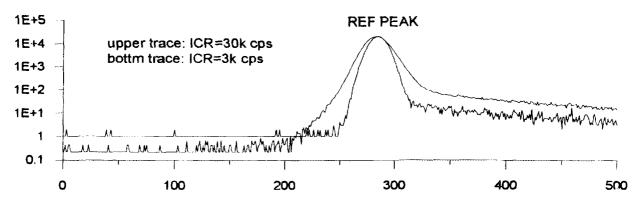

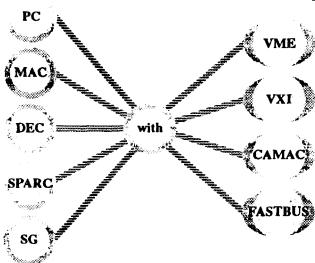

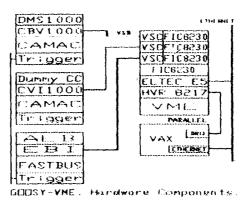

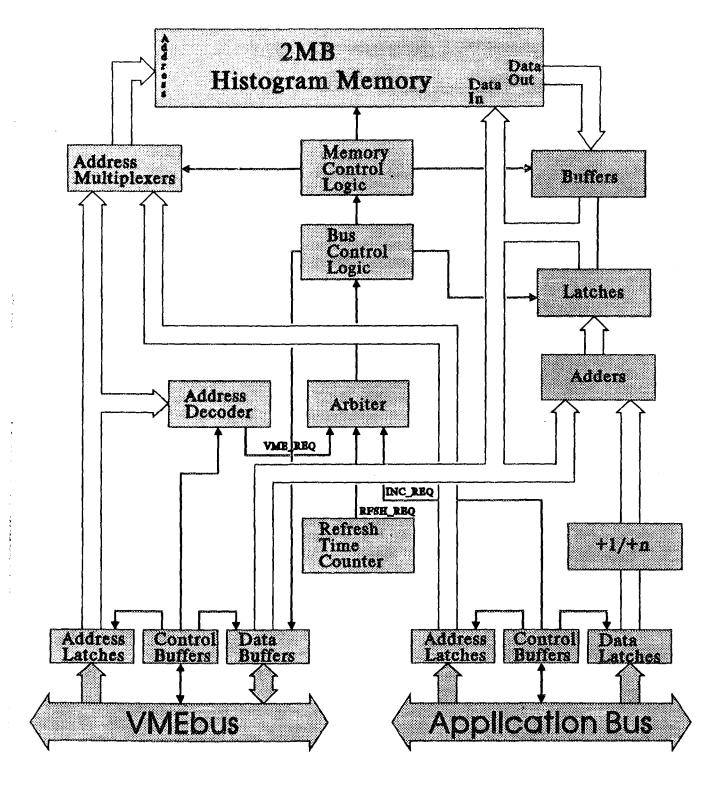

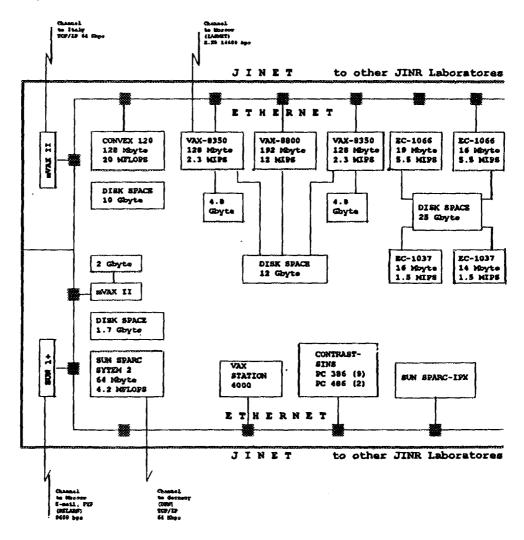

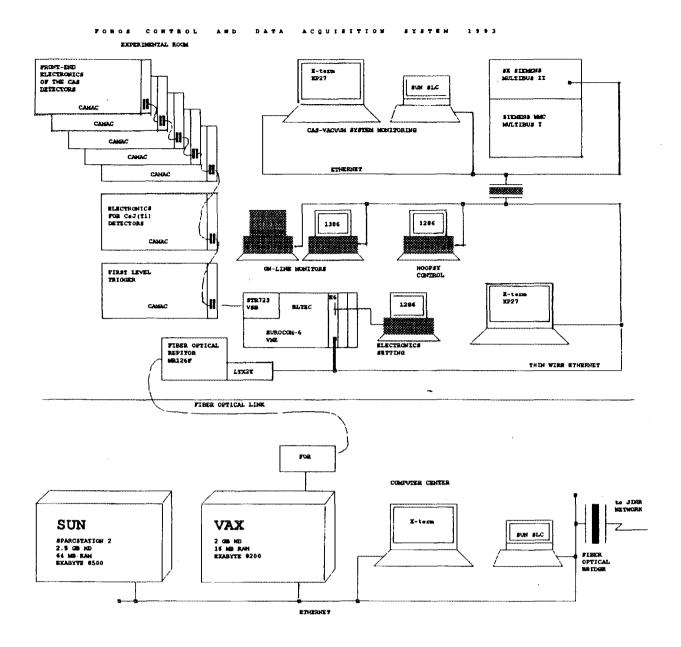

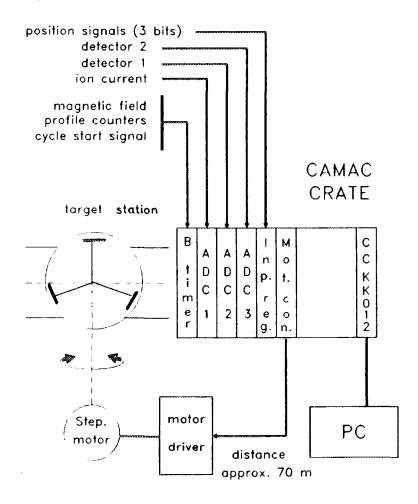

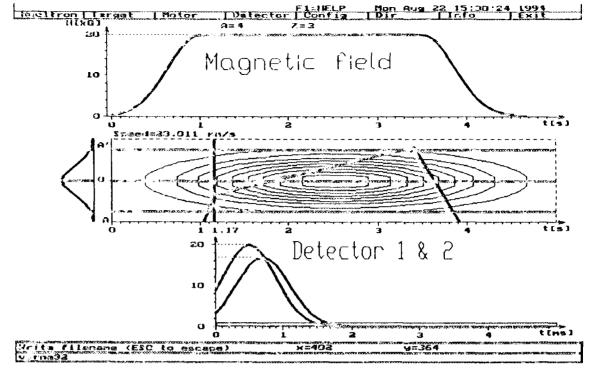

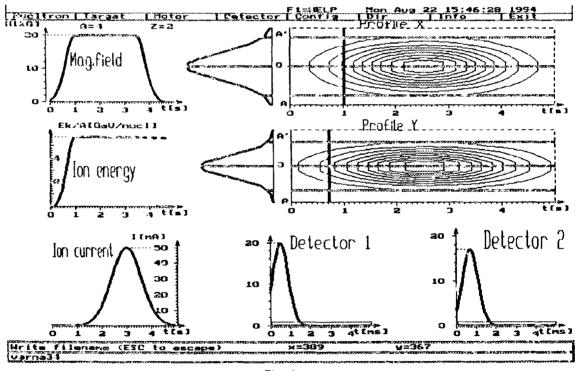

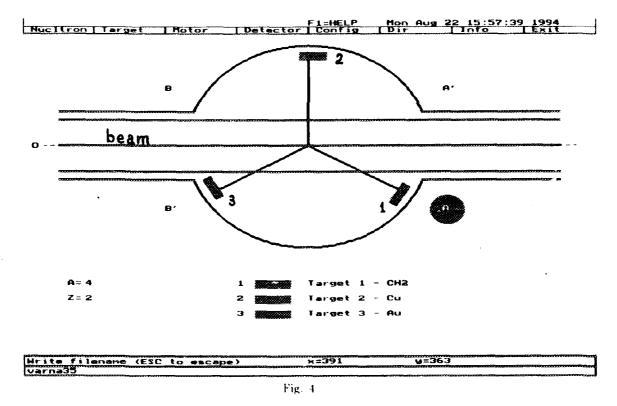

This "CsI fired" signal is sent to the central event selector. Getting LAM the Eurocom-6 VME CPU after reading the gas-ball front-ends looks for the "CsI fired" bit. If it is set, after the finish of the conversion (the conversion time is near 1 ms for the 96 channels of CIAFB ADC) data from FASTBUS modules are transferred to a buffer.