J. E. N. 591

Sp ISSN 0081-3397

**PROYECTO ISLAM: INTERFASE PARA LAS SEÑALES

DE DIVERSAS EXPERIENCIAS DE UN ACELERADOR

VAN DE GRAAF Y UN ORDENADOR PDP 11/44.**

por

MARTINEZ PIQUER, T.A.

YUSTE DE SANTOS, C.

**JUNTA DE ENERGIA NUCLEAR**

**MADRID, 1986**

CLASIFICACION INIS Y DESCRIPTORES:

E42.00

EQUIPEMENT INTERFACES

VAN DE GRAAFF ACCELERATORS

PDP COMPUTERS

DIGITAL SYSTEMS

MICROPROCESSORS

TRANSLATOR

Toda correspondencia en relación con este trabajo debe dirigirse al Servicio de Documentación Biblioteca y Publicaciones, Junta de Energía Nuclear, Ciudad Universitaria, Madrid-3, ESPAÑA.

Las solicitudes de ejemplares deben dirigirse a este mismo Servicio.

Los descriptores se han seleccionado del Thesáuro del INIS para describir las materias que contiene este informe con vistas a su recuperación. Para más detalles consultese el informe IAEA-INIS-12 (INIS: Manual de Indización) y IAEA-INIS-13 (INIS: Thesáuro) publicado por el Organismo Internacional de Energía Atómica.

Se autoriza la reproducción de los resúmenes analíticos que aparecen en esta publicación.

Este trabajo se ha recibido para su impresión en Mayo de 1.986.

PROYECTO ISLAM: INTERFASE PARA LAS

SEÑALES DE DIVERSAS EXPERIENCIAS

EN UN ACELERADOR VAN DE GRAAF Y

UN ORDENADOR PDP 11/44.

La Sección de Control de Procesos de la División de Instrumentación y Control a la que pertenecen los autores, tiene el compromiso con la Dirección de Tecnología de efectuar la reparación de aquellos equipos que, habiendo sido diseñados por personal de la misma para su funcionamiento en algunas de las instalaciones de la JEN, hubieran sufrido alguna avería. Para ello es necesario disponer de una documentación apropiada que permita solventar con relativa facilidad los problemas que pueden surgir pasado un largo período de tiempo desde su construcción.

A la hora de redactar la documentación de equipos que, como éste, trabajan con microprocesadores, es conveniente además destinar una buena parte de la misma a una exposición detallada del programa grabado en su memoria, pues el hecho de analizar un programa tiempo después de su elaboración entraña grandes dificultades, incluso para la misma persona que lo desarrolló.

El objetivo principal de este informe es que pueda ser utilizado como documentación, por lo cual la redacción del mismo puede ser a veces demasiado minuciosa y dada a descender al detalle. Se pretende con ello que una futura labor de reparación o cambio resulte lo más liviana posible.

Se pide pues al lector benevolencia al juzgar el estilo.

Índice:

1. Introducción

2. Equipo electrónico

- 2.1. Fuentes de alimentación

- 2.2. Módulo de adaptación de señales

- 2.3. Módulo del microprocesador

3. Funcionamiento del equipo

4. Programación

- 4.1. Programa principal de operación

- 4.2. Subrutinas de interrupción

- 4.2.1. Subrutina de medida (IRQ)

- 4.2.2. Subrutina de final de medida (NMI)

- 4.3. Subrutinas auxiliares

- 4.3.1. Subrutina de toma de datos

- 4.3.2. Subrutina de multiplexado de datos

- 4.3.3. Subrutina de salida de datos

- 4.3.4. Subrutina de medida de canales

- 4.3.5. Subrutina de vigilancia del registro de datos de salida.

Apéndice A: Figuras

Apéndice B: Listado del programa

## 1. INTRODUCCION

El proyecto ISLAM (Interfase de Señales de una Línea de un Acelerador mediante Microprocesador) es un equipo electrónico que se encarga de transmitir los valores correspondientes a varias medidas eléctricas a un ordenador para su posterior tratamiento. Una serie de señales procedentes de una línea de un acelerador del tipo Van de Graaf son medidas mediante un voltímetro y los correspondientes valores son procesados posteriormente en un ordenador del tipo PDP11/44 con el fin de realizar diversos estudios sobre aspectos de absorción óptica, emisión luminosa y conductividad térmica entre otros. Hasta la puesta en marcha de este equipo el trabajo se realizaba utilizando como soporte de información la cinta perforada con lo que la consecución de una serie de espectros resultaba lenta y tediosa obligando por otra parte a utilizar un equipo poco integrado y de gran tamaño (perforador de cinta y controlador del mismo).

Con el fin de mejorar las condiciones de realización de las experiencias ya indicadas le fué encomendada a la División de Instrumentación y Control el proyecto de una interfase que permitiera procesar las señales en el ordenador directamente y no hubiera por tanto necesidad de utilizar un soporte intermedio.

Las señales eléctricas de la línea del acelerador, que provienen de un monocromador, son enviadas a un voltímetro digital cuya salida es en código BCD de cuatro dígitos y medio. Esta salida de información, ya anticuada, no es del tipo habitual para conexión con ordenador por lo que es necesario realizar un tratamiento previo. El problema evidentemente quedaría resuelto utilizando un voltímetro con una salida normalizada (RS-232, IEEE 488, etc), pero, dado que se pretendía aprovechar el equipo existente, se diseñó una interfase, controlada por microprocesador, poco voluminosa, sencilla y fiable.

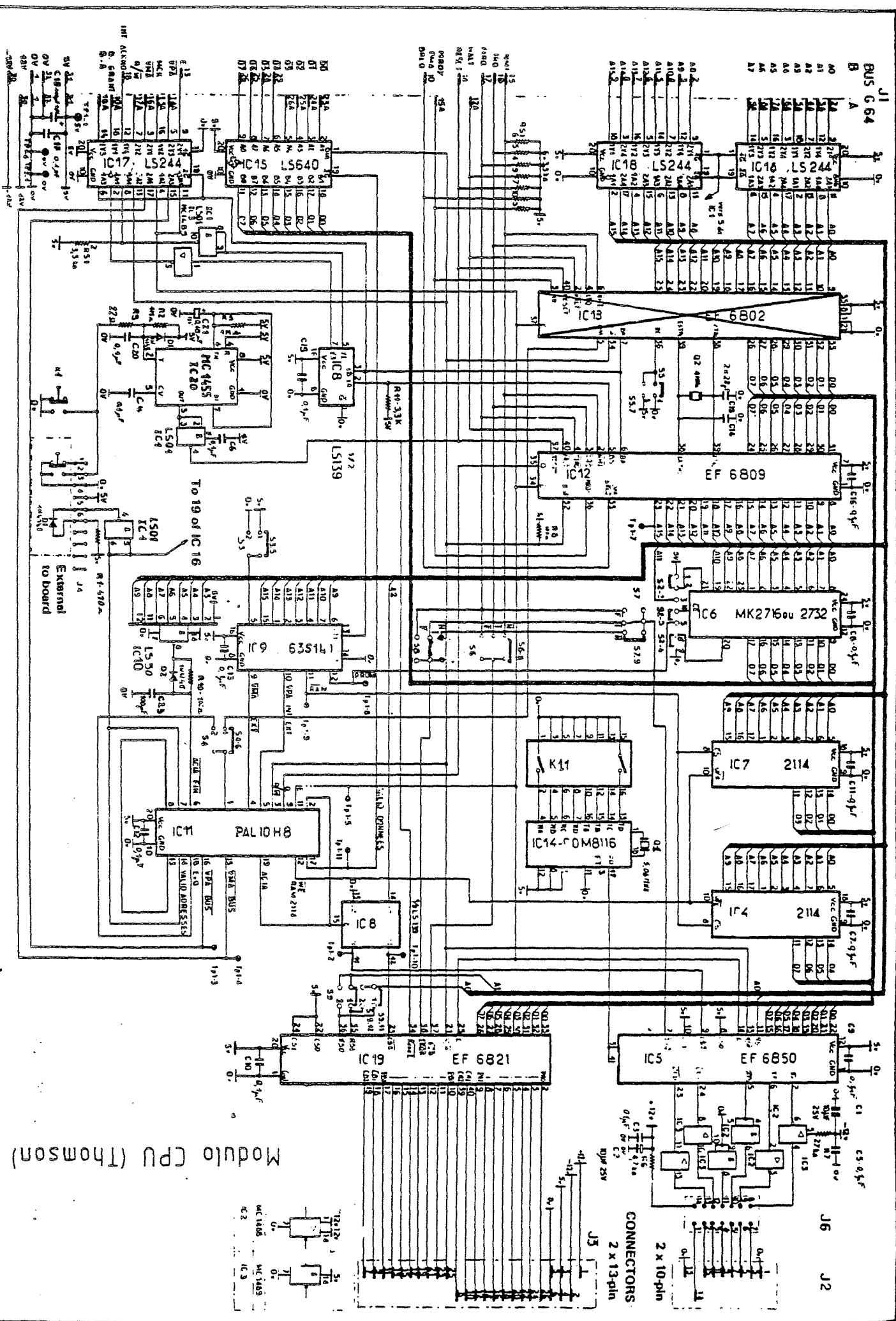

Para la realización de la unidad se siguieron en todo momento las normas que desde hace tiempo utiliza la División de Instrumentación y Control para los trabajos de realización de equipos con microprocesadores de 8 bits. En síntesis, el microprocesador es el M6809, con el que se posee ya gran experiencia y el bus de comunicaciones el denominado G64.

En cuanto a la programación se refiere, el programa de comunicación, que se describirá ampliamente en el apartado correspondiente, está realizado en lenguaje ensamblador y ocupa una extensión de poco menos de 1/2 K.

## 2. EQUIPO ELECTRONICO

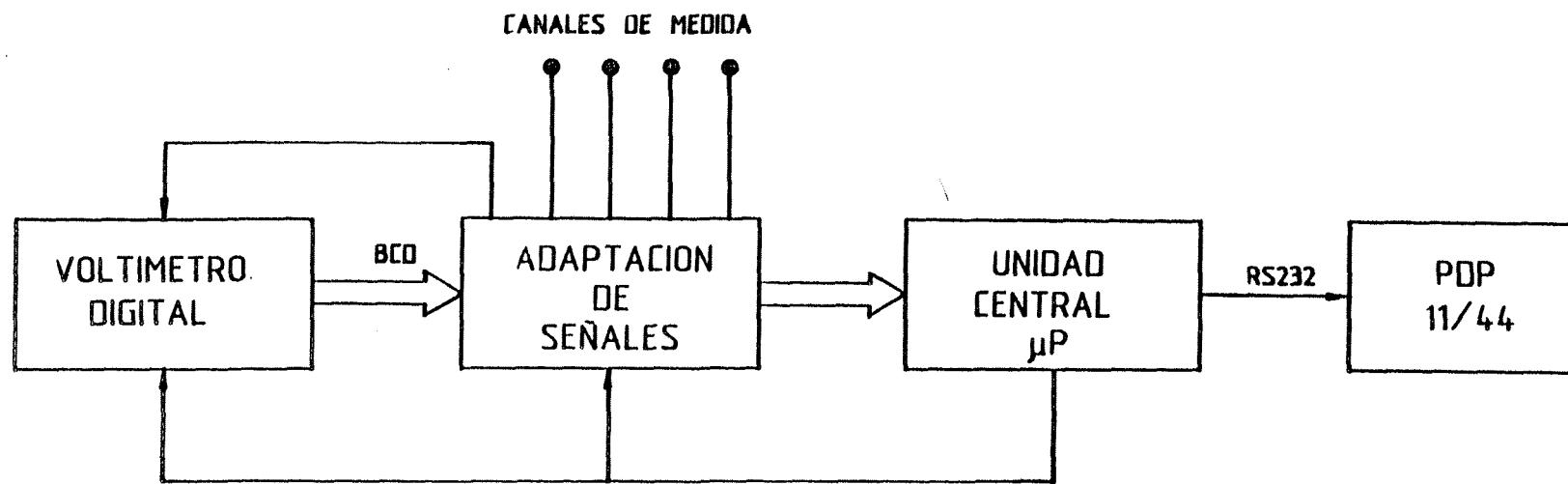

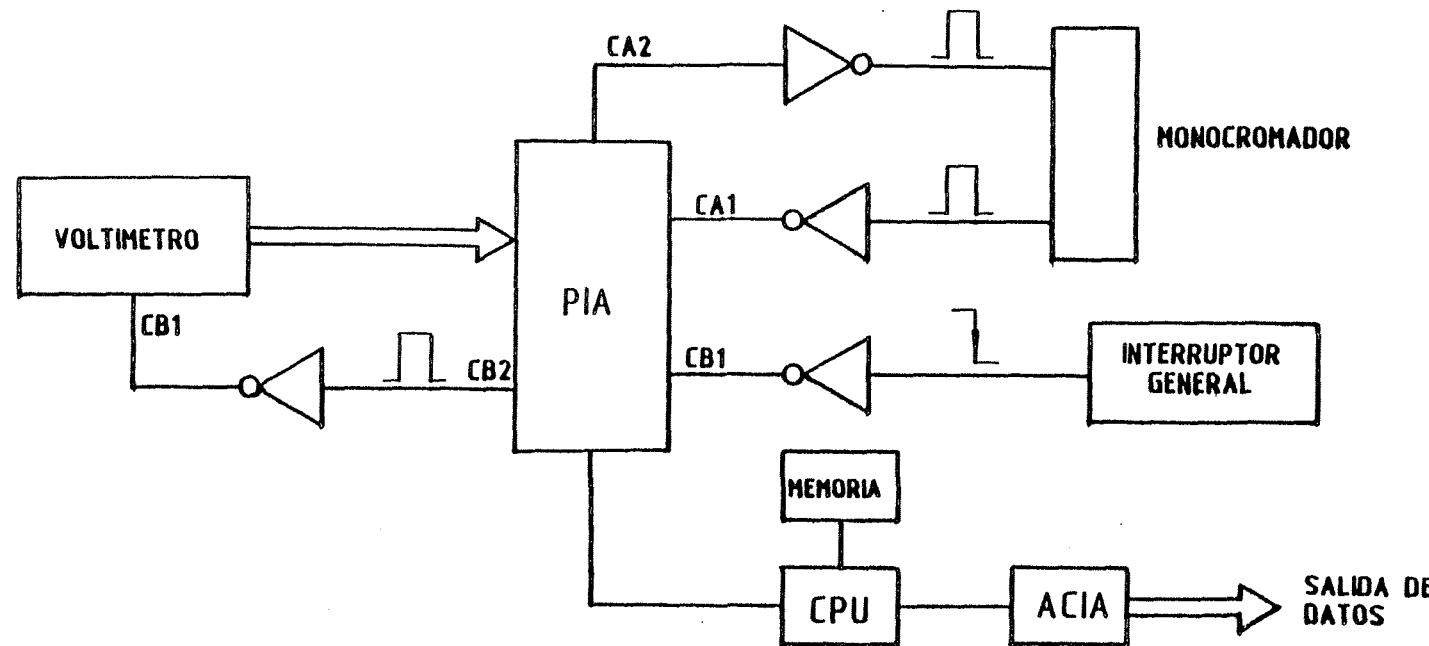

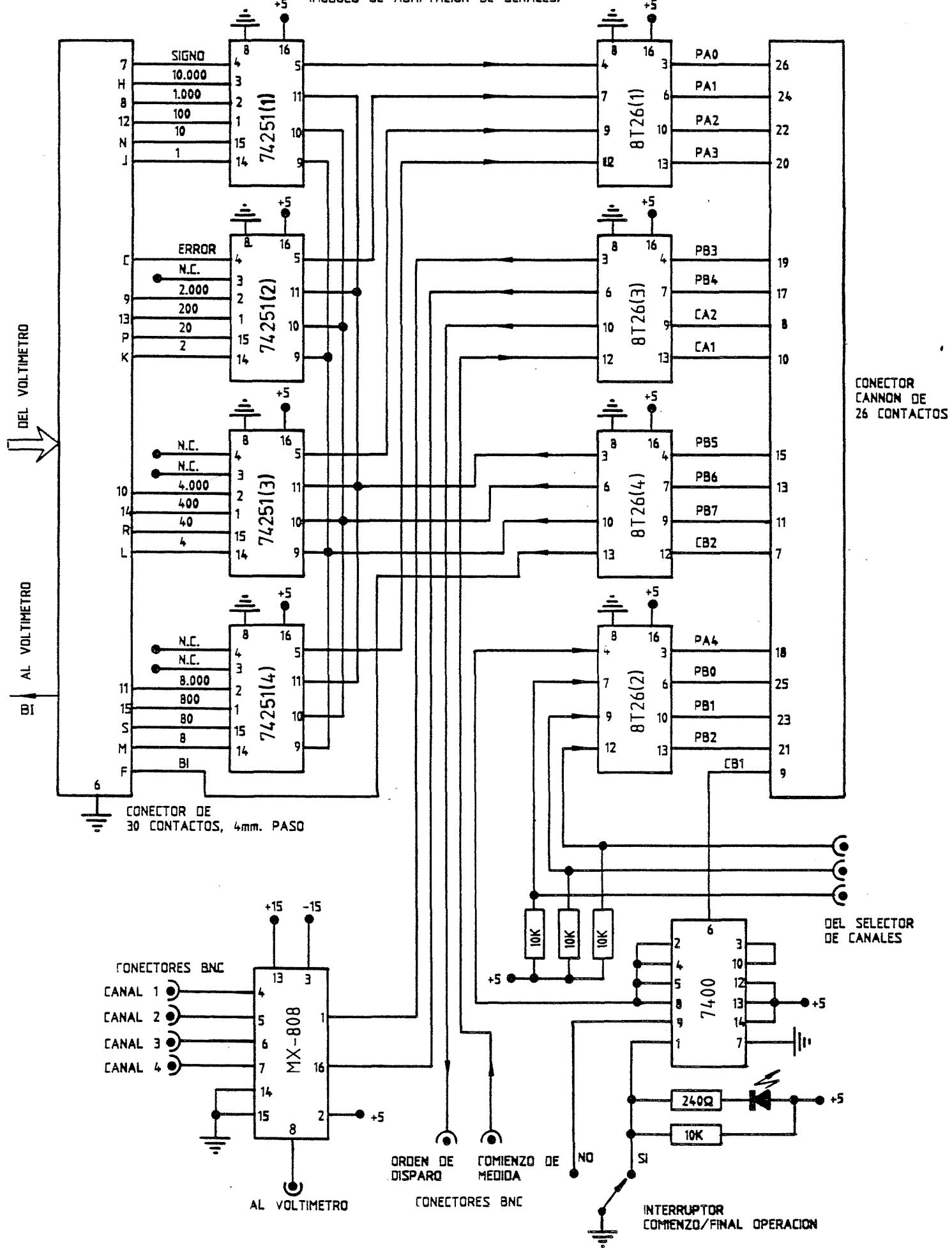

En la figura 1a se puede apreciar un diagrama de bloques del equipo. Las señales eléctricas provenientes del monocromador, en un número máximo de cuatro, son multiplexadas y la medida deseada es enviada al voltímetro digital. La correspondiente información en código BCD, es adaptada convenientemente y enviada a la lógica controlada por el microprocesador que posee una salida serie RS232C mediante la cual se transmite la información al ordenador.

El conjunto electrónico se ha dispuesto en un chasis normalizado de uso habitual en electrónica con tres módulos independiente. En el primero de ellos fueron alojados las fuentes de alimentación; en el segundo, la electrónica necesaria para controlar el voltímetro digital, recoger la información presente a la salida del mismo y presentarla en los elementos entrada/salida de datos del microprocesador y, finalmente, el módulo del microprocesador.

La figura 1b corresponde a un diagrama de conjunto en el que se han reflejado los componentes más característicos.

### 2.1. Fuentes de alimentación.-

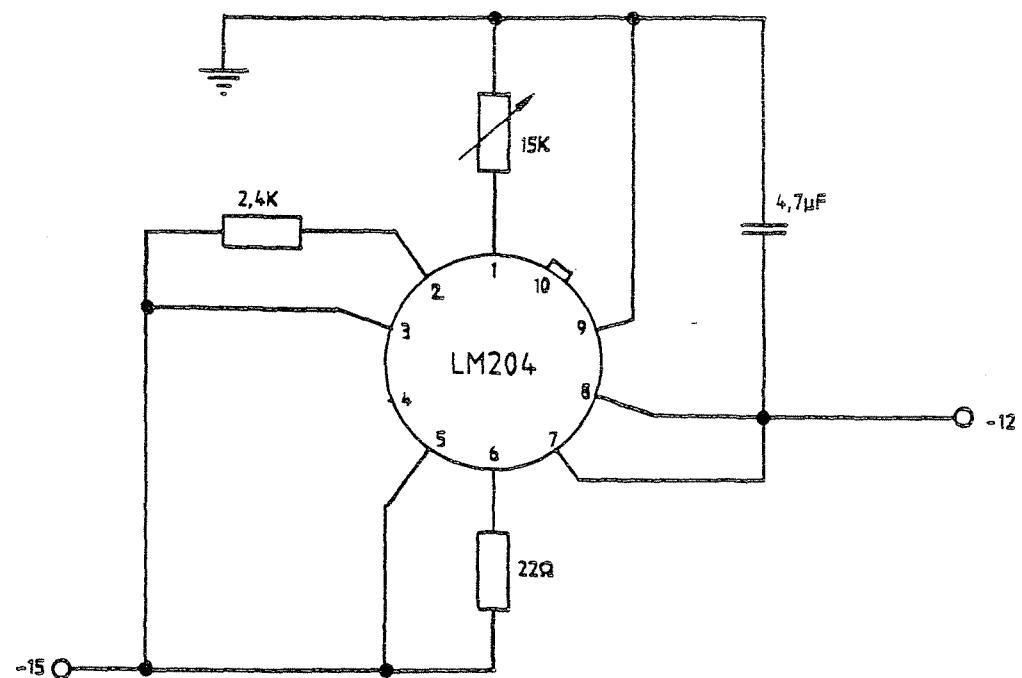

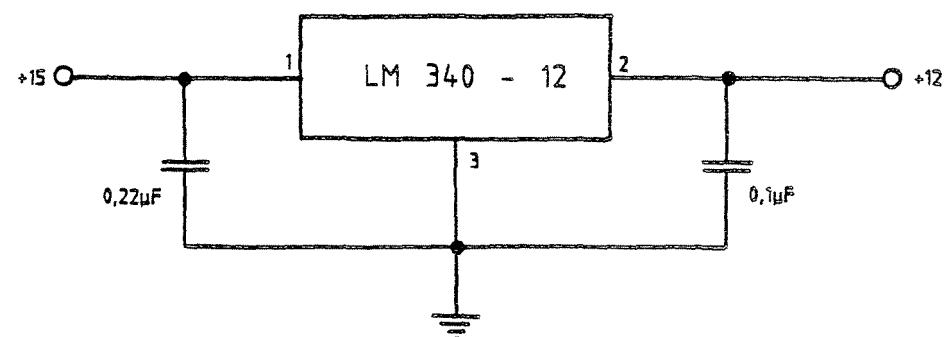

Las tensiones necesarias en el equipo son de 5V,  $\pm 12V$  y  $\pm 15V$ . Estas dos últimas son las que alimentan el multiplexor analógico que pone en comunicación los valores de las señales de la experiencia con el voltímetro, limitando por tanto el valor de las mismas a  $\pm 15V$ .

Para los valores de 5 y  $\pm 15V$  se han utilizado dos fuentes integradas comerciales y para las tensiones de  $\pm 12V$  se han utilizado sendos reguladores de tensión a partir de las tensiones de  $\pm 15V$ . En la figura 2 pueden comprobarse los esquemas eléctricos de las fuentes de  $\pm 12V$ . Si bien el diseño de éstas no es de gran interés se incluyen los esquemas en este informe a fin de su utilización como documentación.

### 2.2. Módulo de adaptación de señales.-

El fin fundamental de éste módulo es, por un lado, la recepción y el envío de las señales de control de la operación y por otro la transmisión de los valores correspondientes a las señales eléctricas recibidas de la experiencia. Un esquema eléctrico de este módulo se encuentra en la figura 3.

Para la realización de los fines aludidos este módulo incorpora una serie de elementos que se encuentran agrupados en cuatro campos bien diferenciados. El primero de ellos se encarga de realizar un multiplexor digital a fin de enviar la información del voltímetro. Para ello se emplean 4 componentes 74251.

La segunda función integrada en este módulo es el multiplexor de los cuatro canales analógicos de entrada. El componente es un MX-808 estando su tensión de trabajo limitada a  $^{+}15V$ .

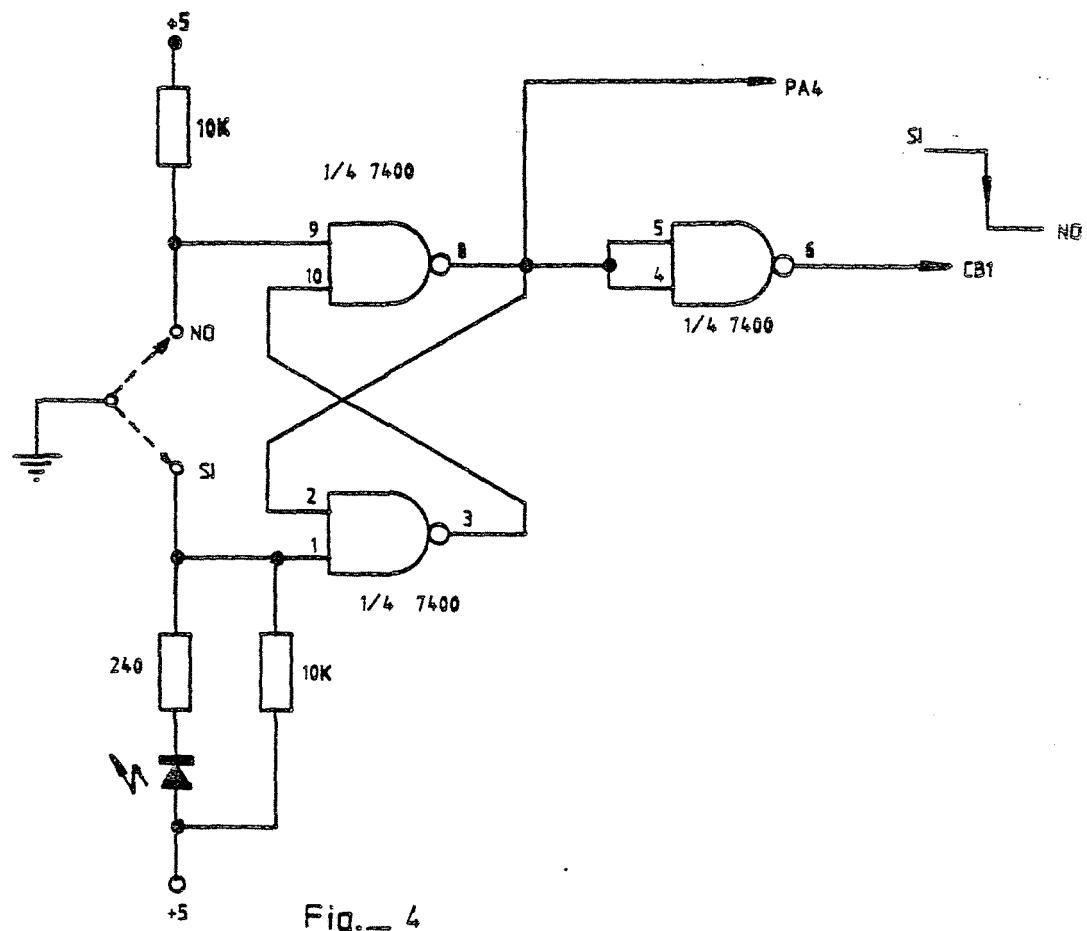

Un tercer campo es el referente a la generación de la señal del comienzo o de la finalización de la operación de medida. Un esquema completo de esta parte se indica en la figura 4. Se incluye en el mismo un dispositivo con antirrebote eléctrico, a fin de impedir falsas maniobras de comienzo/fin, una señalización óptica y una negación, pues son necesarias, como se verá más adelante, la propia señal y su correspondiente negada.

Finalmente, se encuentran en este módulo un grupo de amplificadores de corriente que se encargan de transmitir, o recibir en su caso, las señales ya comentadas y otras de control procedentes del resto del equipo: señal de inhibición/desinhibición de la medida en el voltímetro, señales del selector de canales y las señales encargadas de controlar las diversas medidas durante la operación.

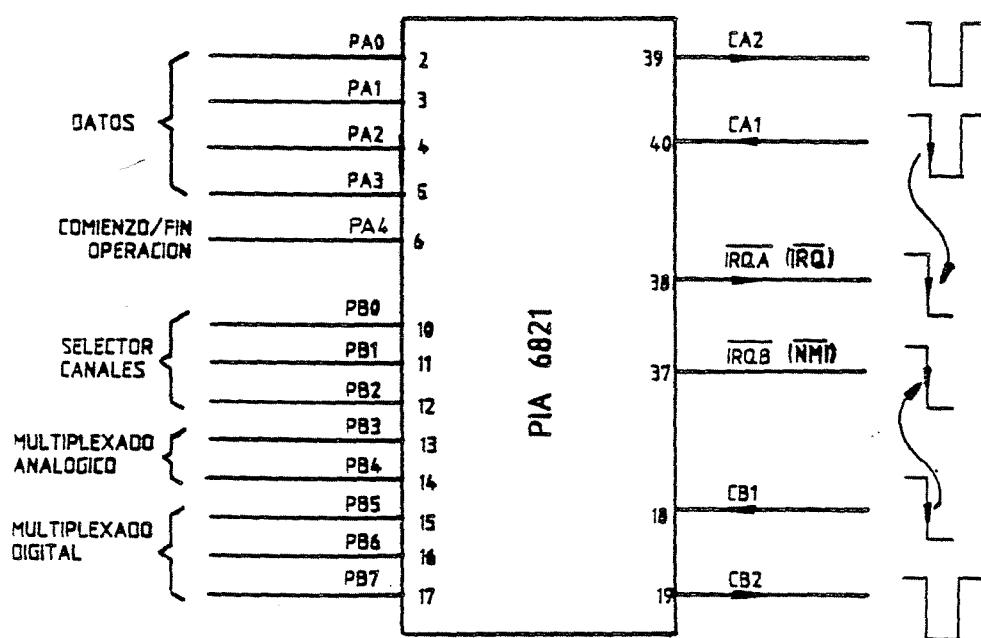

Las señales que este módulo pone en comunicación con el módulo del microprocesador son en total 17 y están identificadas mediante la denominación PA0 a PA4, PBO a PB7, CA1, CA2, CB1 y CB2 y corresponden a la denominación habitual del componente M6821 denominado PIA que es un elemento de entrada/salida de datos al bus del microprocesador. En la figura nº 5 puede observarse el esquema de la PIA6821 con las señales aludidas.

Las funciones que desempeñan estas señales con las siguientes:

- a) Transmisión de la información presente a la salida del voltímetro. Utilizan para ello las líneas PA0/1/2/3 (4 bits). El envío del total de información (4 dígitos y medio) se realiza mediante un proceso de multiplexado en seis etapas: en la primera se envían los dos bits correspondientes al signo y al error (overflow). En la segunda de ellas se envía el bit más significativo y en las cuatro siguientes se transmiten los cuatro dígitos de la medida.

- b) Multiplexado de la información mencionada anteriormente y que llega del microprocesador por las líneas PB5/6/7 (3 bits).

- c) Multiplexado de los cuatro canales analógicos de medida, para lo cual se utilizan las líneas PB3/4 (2 bits).

- d) Determinación del número de canales a medir. Para ello se utiliza un conmutador rotativo cuyas señales se envían al microprocesador por las líneas PB0/1/2 (3 bits).

- e) Inhibición/Desinhibición de la medida presente en el voltímetro. Señal transmitida por la línea CB2 (1 bit).

- f) Control de la realización de los diversos puntos de medida correspondientes a una experiencia. Se utilizan a tal fin las líneas CA1 y CA2 (2 bits).

- g) Control general de la experiencia: comienzo/fin. Se emplean para ello 2 líneas: PA4 y CB1 (2 bits).

### 2.3. Módulo de microprocesador

Es el conjunto central del equipo y tiene como misión fundamental recibir la información del voltímetro, procesarla

adecuadamente, enviarla a los circuitos de entrada del ordenador y controlar la operación de medida en sus diferentes fases. Se trata de un módulo comercial, en este caso de la firma Thomson, cuyos componentes más característicos son los siguientes:

- Procesador central (EF 6809). Es un procesador de 8 bits que trabaja con una frecuencia de reloj de 1 MHz.

- Comunicación en paralelo para entrada/salida (EF 6821). Posee dos secciones de 8 bits cada una para la recepción o transmisión de señales y cuatro líneas de control más dos líneas de interrupciones. Cuenta asimismo con 8 líneas de datos y las correspondientes líneas de control propias del elemento.

- Comunicación en serie (EF 6850). Salida normalizada RS 232C hasta 19200 baudios de velocidad de transmisión.

- Memoria RAM estática con una capacidad de 1 K (2x2114).

- Memoria EPROM con un total de 2 K (2716), donde se encuentra grabado el programa de aplicación.

Un esquema completo del módulo puede contemplarse en la figura 6. Como se dijo anteriormente es un módulo comercial y en este caso la tarjeta está preparada para trabajar con dos tipos de microprocesador (EF 6809 ó EF 6802). En nuestro caso se incorpora el primero de ellos, si bien en el esquema figuran ambos.

### 3. FUNCIONAMIENTO DEL EQUIPO

Previo a una exposición detallada del funcionamiento del equipo se realiza una pequeña descripción del proceso físico de medida en la línea del acelerador.

La experiencia consta, por regla general, de uno o varios espectros para lo cual, por cada uno de ellos, es necesario conseguir un elevado número de puntos de medida. La señal que inicia el proceso de medida en cada espectro es generada por una electrónica asociada al acelerador e indica que el monocromador está dispuesto para la misma. Realizada la medida, el monocromador se sitúa en una nueva posición, envía la señal de preparado y se realiza la nueva medida. Este proceso continúa de forma cíclica y únicamente es detenido por causas extrañas al propio proceso como se verá mas adelante.

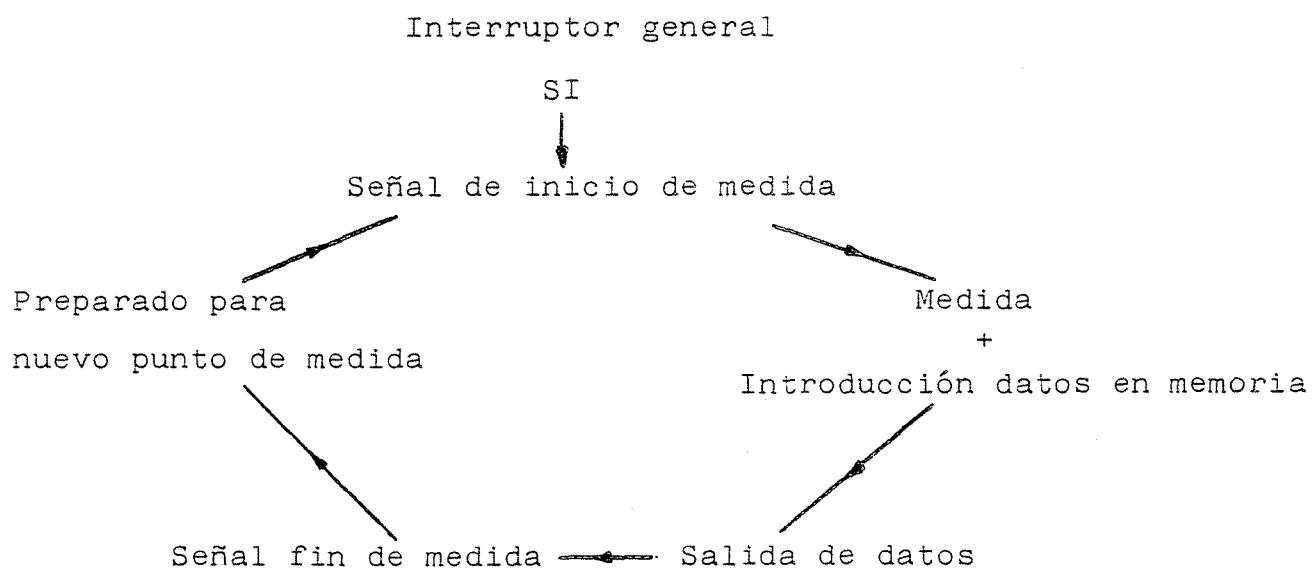

Visto lo anterior, el equipo funciona de la siguiente forma:

Una vez que el operador ha colocado el interruptor general de operación en la posición SI, el equipo se queda a la espera de la señal de comienzo que le debe llegar por la línea de control CA1 de la PIA. La sección A de este elemento se encuentra programada de tal forma que el flanco de bajada de la señal genera una interrupción que conectada a la línea IRQ del microprocesador hace funcionar la subrutina correspondiente y provoca el proceso de medida de un punto. Este, consiste fundamentalmente en un retardo inicial de 100 ms, la determinación del número de canales a medir, la inhibición de la señal en el voltímetro digital para lo cual se activa la línea CB2 y finalmente la toma de datos correspondientes al primer canal tras un retardo de 500 ms. Realizada la toma de datos, se desinhibe la señal del voltímetro, se almacenan aquellos en las posiciones de memoria destinadas a tal fin y se continúa con la medida de los restantes canales mediante el ciclo referido de señal de inhibición-retardo-medida-señal de desinhibición-almacenamiento.

Cuando se ha completado la fase de toma de datos, esto es, se encuentran en la memoria los valores correspondientes a los canales fijados por el operador, se realiza la fase de salida de los mismos mediante la ACIA, con lo cual se completa el ciclo de la primera medida.

A continuación se envía al monocromador una señal por la linea CA2 como final de medida, con lo que aquel se sitúa en la posición correspondiente al siguiente punto de medida. En ello invierte un determinado tiempo, transcurrido el cual el circuito asociado al monocromador envía una nueva señal por CA1 que desencadena la medida del siguiente punto. Un esquema del ciclo de funcionamiento se indica a continuación.

Este proceso continúa indefinidamente a menos que se produzcan los siguientes hechos:

- a) La señal que debe enviar el monocromador por la linea CA1 como comienzo de operación no llega, con lo cual el proceso se queda a la espera del mismo.

b) El operador decide dar por finalizado el proceso, o bien abortar el mismo, para lo cual coloca el interruptor general de operación en la posición NO.

En este último caso el cambio de estado del interruptor genera una señal eléctrica que entra a la sección B de la PIA por la línea de control CB1. Esta sección, programada de la misma forma que la sección A, genera con el flanco de bajada de CB1 una interrupción que es conectada a la línea NMI del microprocesador. La lógica interna de éste concede carácter prioritario a esta interrupción, de forma tal que atiende la subrutina correspondiente de forma inmediata y hace parar el proceso.

En el caso de que la interrupción NMI se produzca durante el proceso de medida generado por la IRQ, el procesador atenderá primero aquella y, una vez finalizada, proseguirá con la segunda; acabada la cual el equipo se queda desactivado. Un nuevo proceso de medida pasa necesariamente por la activación del interruptor comienzo/fin de operación. (Posición SI).

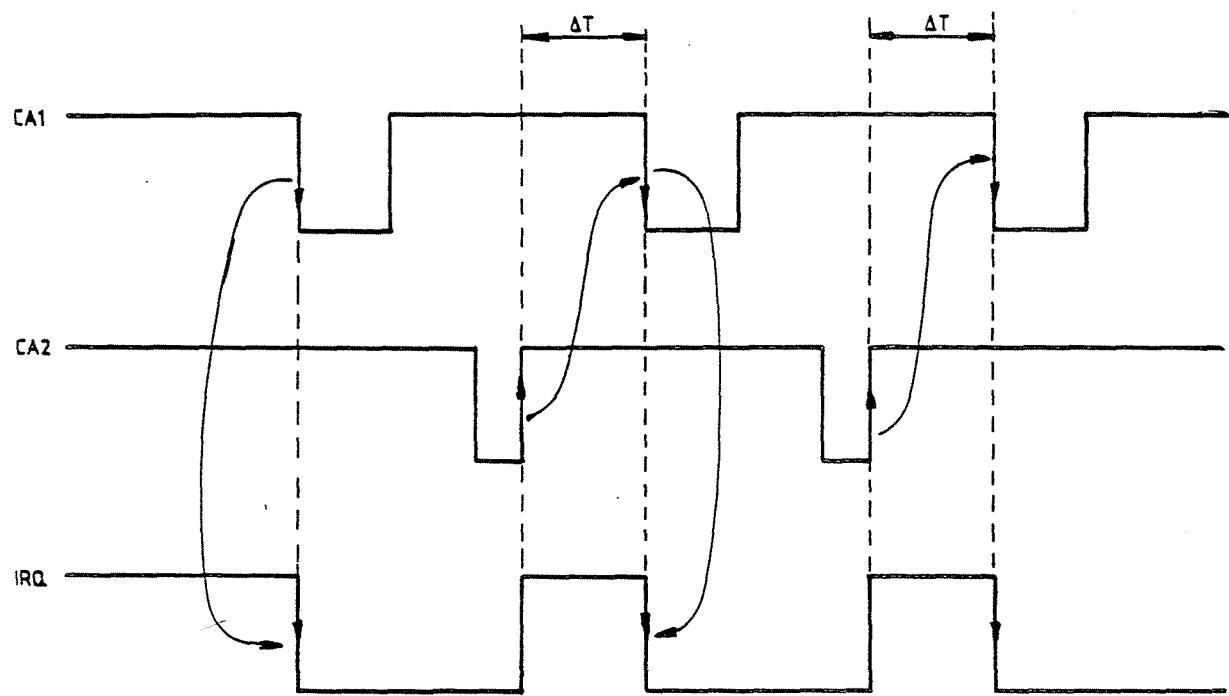

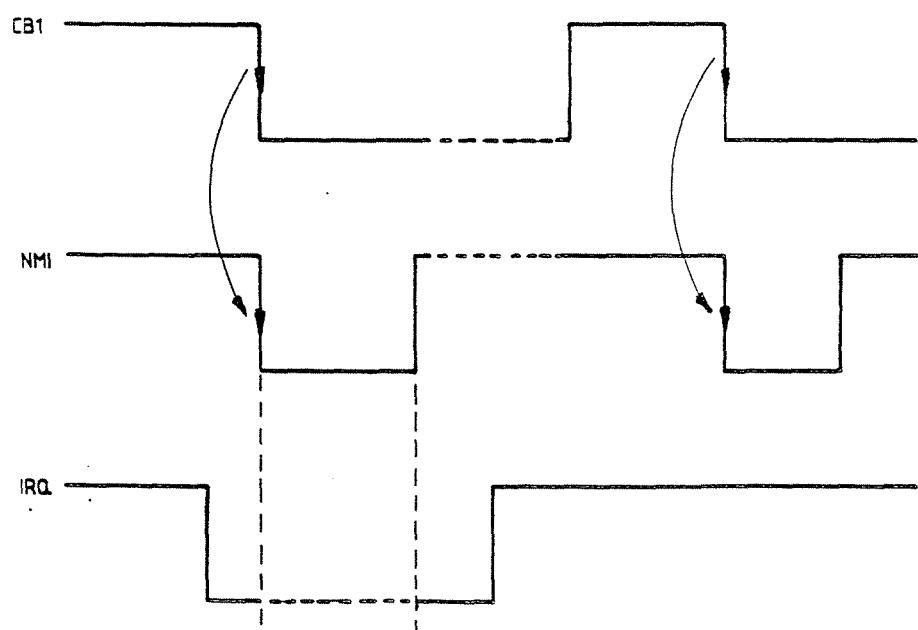

Un diagrama de tiempos de las diferentes señales de control se refleja en la figura 7.

#### 4. Programación

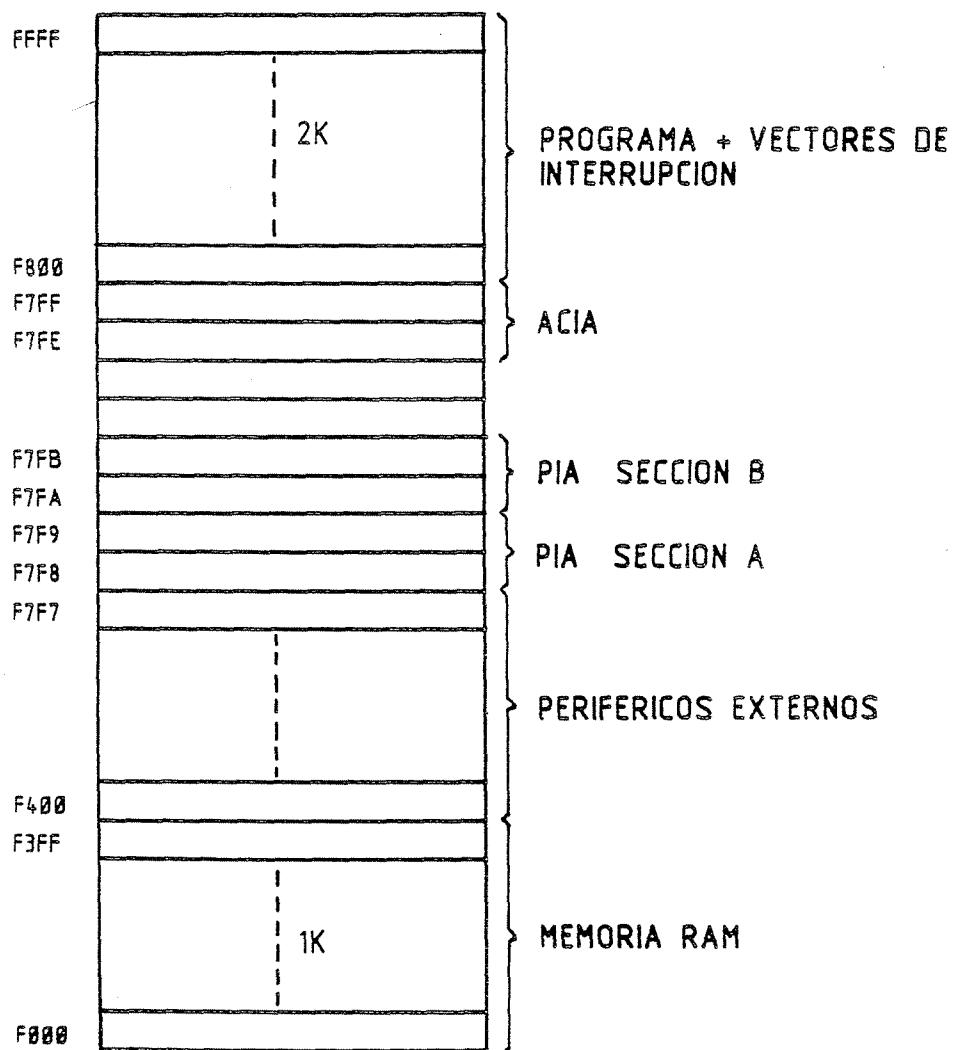

El mapa de memoria se encuentra reflejado en la figura 8 donde puede observarse que el programa de aplicación grabado en EPROM comienza a partir de la posición F800. La última posición del mismo es la F9CC por lo cual la extensión (en decimal) es de 464 posiciones.

El resto de la zona de memoria es la correspondiente a la memoria RAM, periféricos externos (que en este caso no se incorporan) y las posiciones en que están situadas la PIA y ACIA.

En las últimas posiciones de la memoria se encuentran los vectores de interrupción y el reset, tal cual puede verse en la misma figura 8.

La programación de los elementos periféricos internos de entrada-salida está realizada de la siguiente forma:

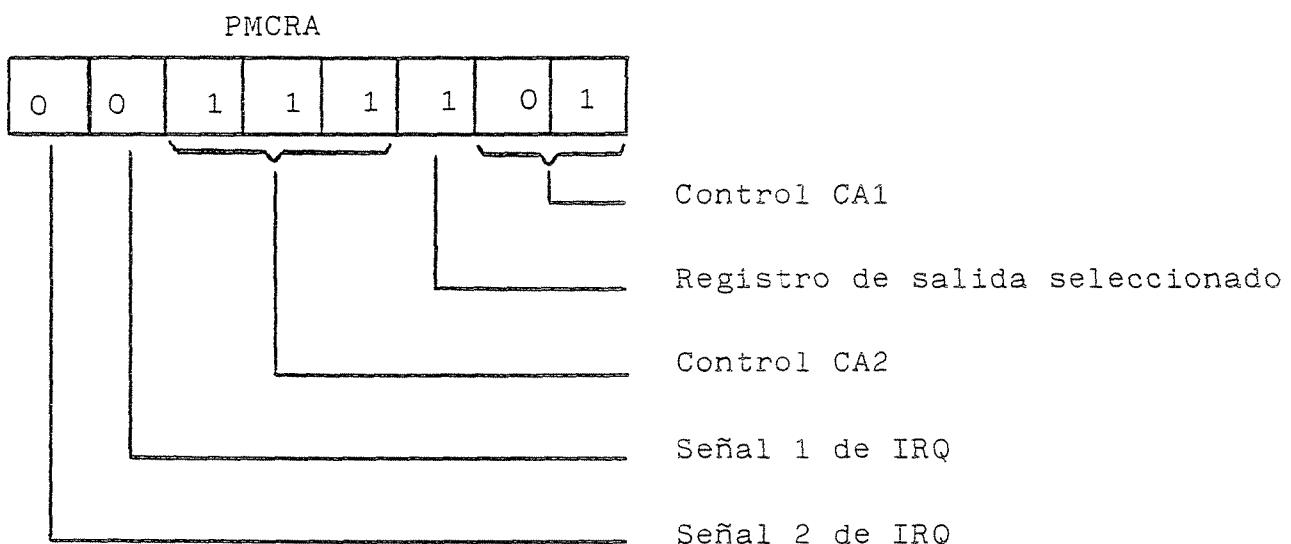

La sección A de la PIA está programada en modo set-reset, con salida de CA2 en alto y de tal forma que se produzca la interrupción con la señal de entrada por CA1 en el flanko de bajada. Todas estas características corresponden a un formato del registro de control como sigue:

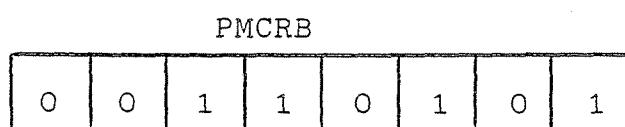

En cuanto a la sección B, el modo de funcionamiento de la experiencia hace que la programación sea idéntica excepto en que el estado de reposo de la línea CB2 es esta vez bajo. Así, el registro de control en este caso tiene el siguiente formato:

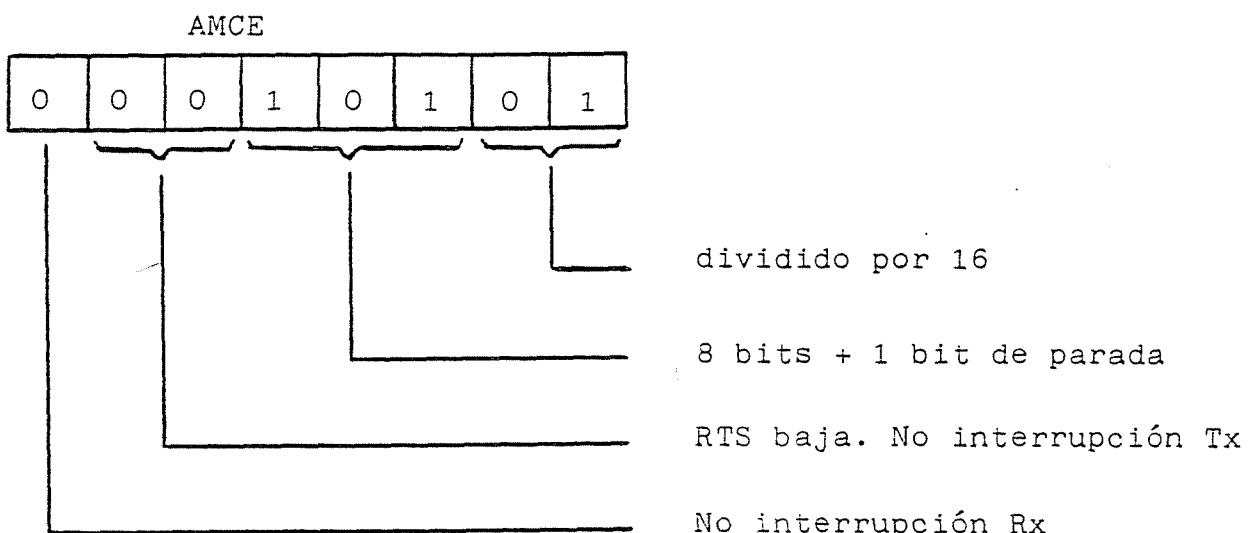

Por otro lado, el elemento serie de entrada-salida ACIA 6850 va programado de la siguiente forma: 8 bits de información con un bit de parada sin incluir paridad, relación de división 16, no RTS y sin interrupciones. Todo ello corresponde a un registro de control con la información siguiente:

El programa de aplicación consta de un programa principal y de diversas subrutinas que serán expuestas en los sucesivos apartados.

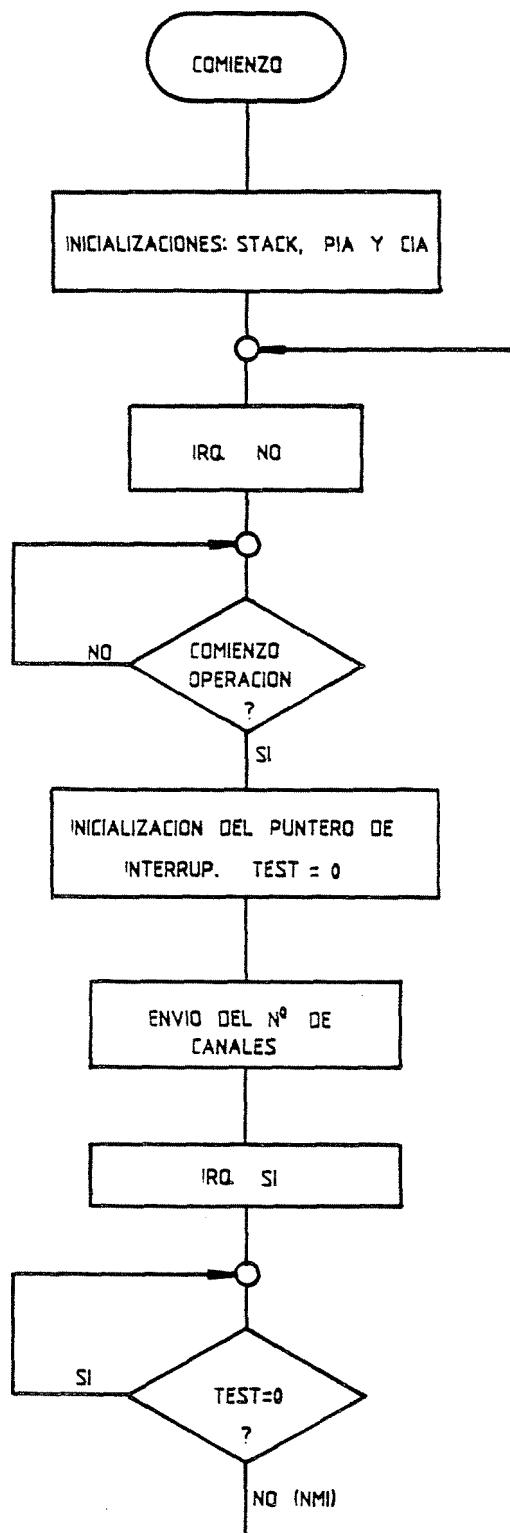

#### 4.1. Programa principal de operación

La filosofía del programa principal está basada en torneo a dos lazos de espera, que vigilan en cada momento el estado del interruptor general de operación. El primero de ellos que debe de partir de un estado del citado interruptor desactivado, comprueba cuando el operador decide comenzar el proceso para lo cual sitúa el interruptor en la posición SI. En esta situación el programa pasa, tras algunas instrucciones, al segundo lazo donde queda a la espera de las interrupciones IRQ o NMI.

A partir de este momento el programa vigila el nuevo estado del interruptor general. Las medidas se efectúan mediante las interrupciones IRQ, si éstas se producen, y únicamente se sale del lazo cuando suceden las interrupciones NMI. El programa utiliza para ello una palabra (TEST) que toma el valor 0 cuando no se produce la interrupción NMI y 1 cuando se produce.

En torno a los dos lazos reseñados va pues estructurado el programa principal cuya descripción completa es la siguiente:

Se comienza inicializando el stack, así como la PIA y la ACIA. Se inhiben a continuación las interrupciones a fin de evitar falsas actuaciones y se entra en el primer lazo de los dos aludidos. Una vez que se ha activado el interruptor de operación, se inicializa el puntero de interrupciones de NMI (TEST=0), se envía por la línea de salida el número de canales a medir, se permiten las interrupciones y se entra ya en el segundo lazo.

En este momento el programa está a la espera de las interrupciones. Si se produce la IRQ, se realiza el proceso de lectura y como durante el mismo no se hace variar el puntero TEST, se van efectuando una tras otra otras las medidas. Ahora bien, si se produce la interrupción NMI, el puntero TEST toma el valor 1 con lo cual el control del programa retorna al comienzo del mismo y queda detenido en el primer lazo.

El diagrama de flujo de este programa se encuentra en la figura 9.

#### 4.2. Subrutinas de interrupción

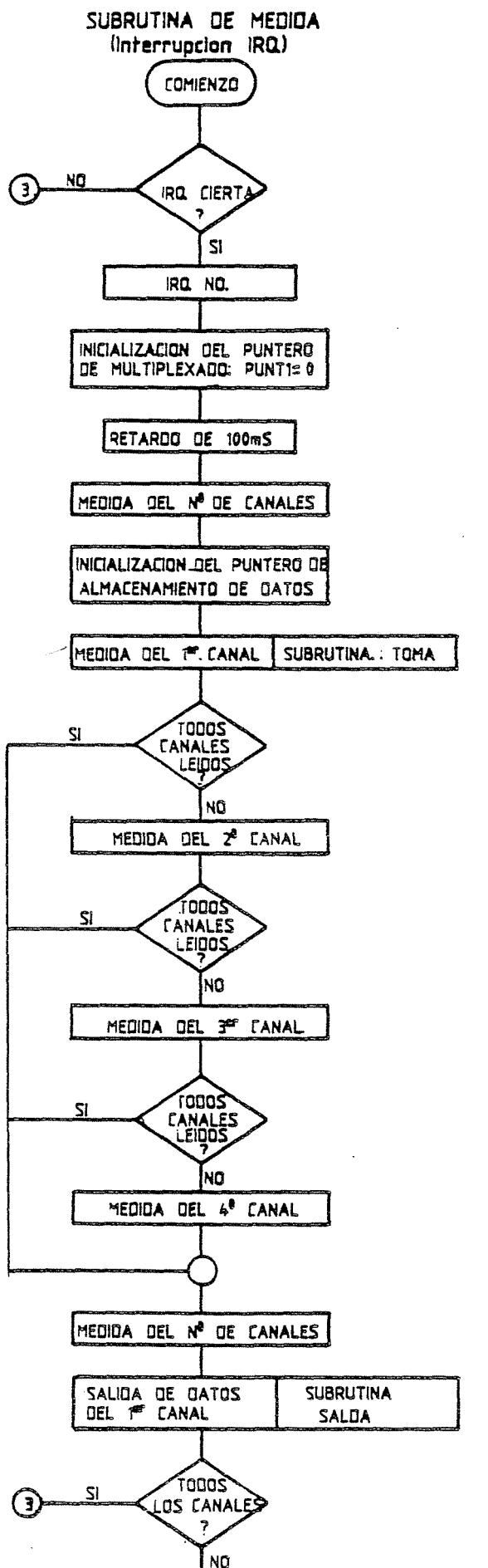

Son aquellas correspondientes a las interrupciones IRQ y NMI cuyos diagramas de flujo pueden verse en la figura 10.

#### 4.2.1. Subrutinas de medida (IRQ)

Cuando se produce la interrupción IRQ, se transfiere el programa a esta subrutina que es la encargada de realizar el proceso de medida de cada punto y a la vez de enviar al monocromador la orden necesaria para situarla en un nuevo punto.

La subrutina comienza analizando si la interrupción producida es correcta, para lo cual analiza el bit mas significativo del registro de control PMCRA de la PIA (Si la interrupción es cierta el bit debe ser 1).

Se inhibe a continuación la interrupción IRQ y tras un retardo de 100 ms para realizar la primera medida se determina el número de canales y se inicializa el puntero de datos (lugar de la memoria a partir del cual se van a situar los datos: en este caso es la \$F000). A continuación se realiza la medida del primer canal utilizando para ello la subrutina TOMA, y se comprueba posteriormente si se realiza la medida de todos los canales activados. Una vez que han sido leídos todos, se comienza la fase de salida de datos, para lo cual se utiliza la subrutina SALDA. Uno tras otro van saliendo por la ACIA los valores correspondientes y tras el último de ellos, se envía la orden de disparo al monocromador y finalmente se vuelve a permitir la interrupción IRQ.

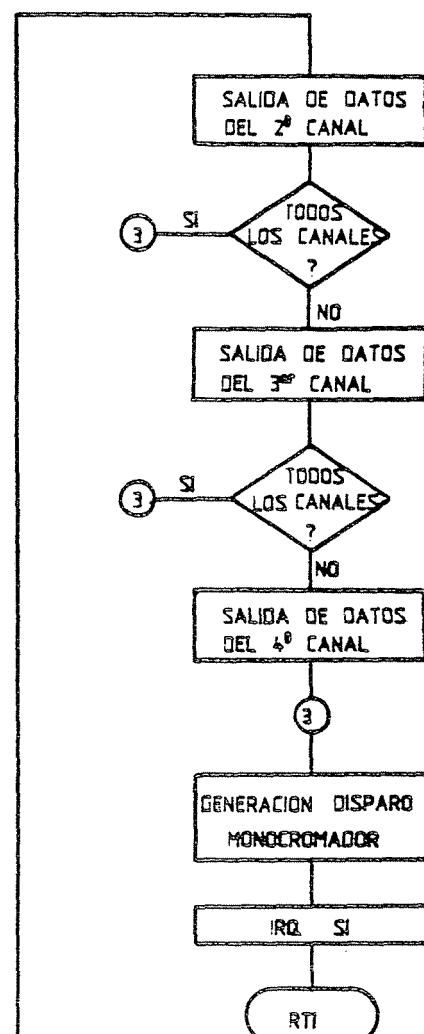

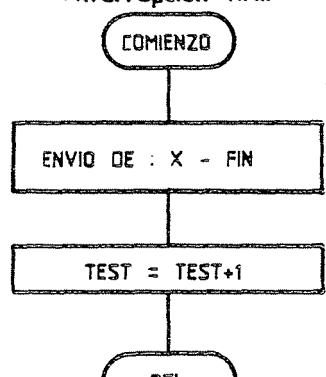

#### 4.2.2. Subrutina de final de medida (NMI)

Esta subrutina tiene un carácter prioritario de ejecución dadas sus características. Sea cual sea el punto en que se encuentra el programa ejecutándose, producida la interrupción NMI se transfiere el control a esta subrutina.

Consta tan sólo del envío del cartel X-FIN y del incremento del puntero TEST. Así, retornado el control al programa principal, el nuevo valor del puntero hace que el programa comience de nuevo a ejecutarse desde el comienzo.

#### 4.3. Subrutinas auxiliares

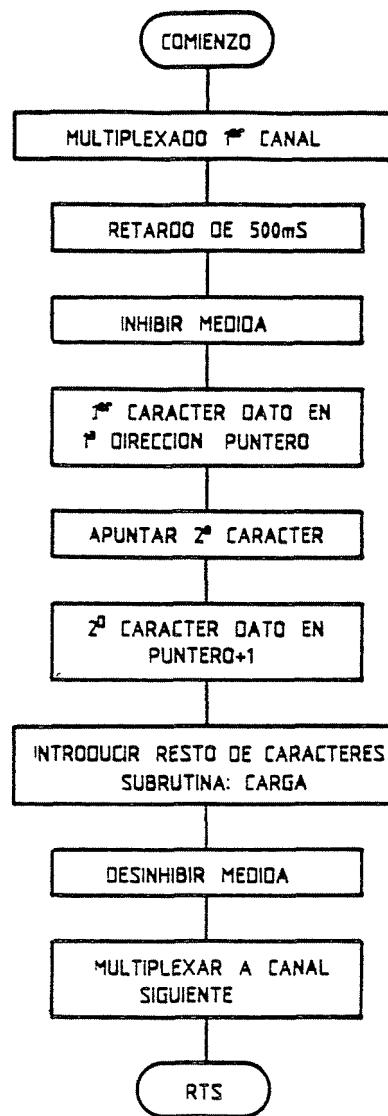

##### 4.3.1. Subrutina de toma de datos: TOMA

Se encarga de extraer los datos presentes en la salida del voltímetro correspondientes a cada canal, así como de alojarlos en la memoria.

En primer lugar realiza el multiplexado necesario para efectuar la medida del primer canal, efectúa a continuación un retardo de 500 ms para dejar estabilizar la medida en el voltímetro y pasado este tiempo inhibe la misma. Introduce posteriormente uno tras otro todos los caracteres de la información de la medida en la memoria, para lo cual utiliza en parte la subrutina CARGA, y finalizado esto, desinhibe la señal y multiplexa para efectuar la lectura del siguiente canal.

Tanto esta subrutina como la siguiente CARGA pueden observarse en su totalidad en la figura nº 11.

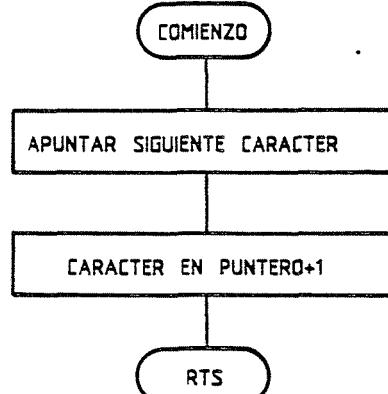

##### 4.3.2. Subrutina de multiplexado de datos: CARGA

Se encarga de realizar un multiplexado tal que los diversos caracteres de la información (correspondientes a los dígitos de la medida) se vayan introduciendo secuencialmente en la memoria.

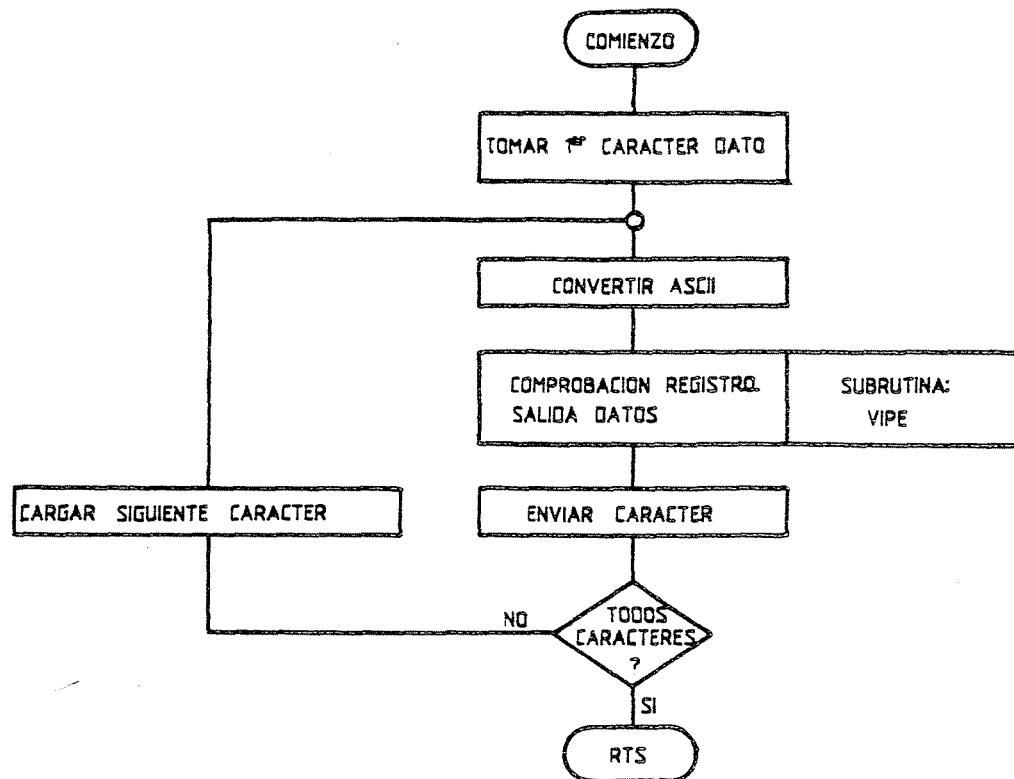

#### 4.3.3. Subrutina de salida de datos: SALDA

Realiza la salida de los datos existentes en memoria por la línea RS232C que comunica con el ordenador. Para ello toma el primer carácter de la memoria (Recuérdese a título de ejemplo que en esta primera información van almacenados los bits correspondientes al signo y al error); convierte éste carácter al código ASCII y lo envía al exterior presentándolo en el registro de datos de la ACIA. Antes de realizar esta última operación es necesario comprobar que el citado registro está vacío, para lo cual se utiliza la subrutina VIPE. A continuación toma consecutivamente todos los caracteres de la información y cuando ha finalizado la transmisión de todos ellos retorna a la subrutina de medida.

El diagrama de flujo de esta subrutina está en la figura 12.

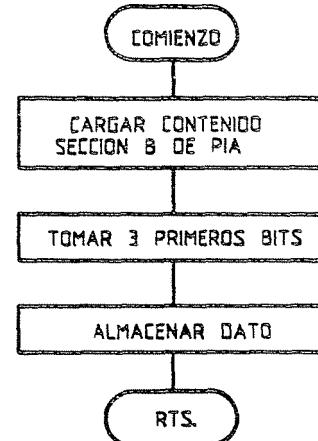

#### 4.3.4. Subrutina de medida de canales: MECA

Esta subrutina se encarga de medir el contenido de los tres bits correspondientes al selector de canales situado en el frontis del equipo. En este selector el operador hace figurar el número de canales que es necesario medir en la experiencia.

El diagrama de flujo puede observarse en la figura 12.

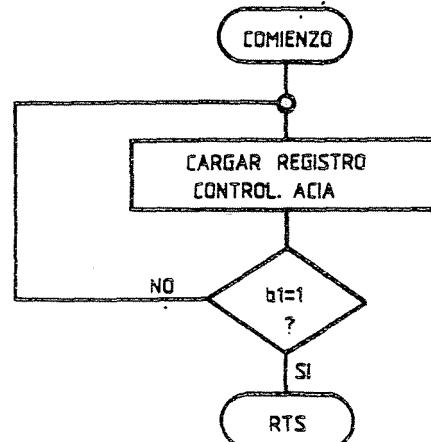

#### 4.3.5. Subrutina de vigilancia de registro de datos: VIPE

En la transmisión de los datos al ordenador es necesario que antes de cargar los mismos en el registro de salida se compruebe si éste está vacío de contenido. Esta subrutina cumple tal cometido y para ello controla la palabra de estado de la ACIA cuyo segundo bit menos significativo nos da información del estado del registro de salida de datos.

En la misma figura 12 se encuentra el diagrama de flujo correspondiente a esta subrutina.

Un listado del programa se encuentra en el apéndice B.

## APENDICE A

Fig. 1a

Fig. 1b

FUENTES DE  $\pm 12V$

Fig. — 2

# TARJETA INTERFASE DE DATOS Y SEÑALES DE CONTROL

(MODULO DE ADAPTACION DE SEÑALES)

### INTERRUPTOR COMIENZO/FINAL DE OPERACION

ENTRADA PARALELO (PIA)

Fig.— 5

g - 614

DIAGRAMA DE TIEMPOS

( a )

( b )

Fig.-7

|      |             |    |

|------|-------------|----|

| FFFF | RESET(BAJO) | 80 |

| FFFE | RESET(ALTO) | F8 |

| FFFD | NMI (BAJO)  | 4E |

| FFFC | NMI (ALTO)  | F8 |

|      | SWI (BAJO)  | —  |

|      | SWI (ALTO)  | —  |

| FFF9 | IRQ (BAJO)  | 86 |

| FFF8 | IRQ (ALTO)  | F8 |

DIRECCIONES

DE LOS VECTORES

DE INTERRUPCION

### VECTORES DE INTERRUPCION

Fig.\_ 8

## PROGRAMA PRINCIPAL DE OPERACION

Fig.\_9

( a )

**SUBRUTINA DE FINAL DE MEDIDA

(Interrupcion NMI)**

( b ).

Fig.---10

### SUBRUTINA DE TOMA DE DATOS (TOMA)

### SUBRUTINA DE MULTIPLEXADO DE DATOS (CARGA)

Fig.-11

### SUBRUTINA DE SALIDA DE DATOS (SALDA)

### SUBRUTINA DE MEDIDA DE CANALES (MECA)

### SUBRUTINA DE VIGILANCIA DE REGISTRO DE DATOS (VIPE)

Fig.\_ 12

APENDICE B

```

1. SECTION CONFU

2. ; PROGRAMA DE INTERFASE

3. ; CROMATOGRAFO-FID FUSION

4.

5. ;OPT LOAD

6.

7. ; ASIGNACIONES

8.

9.

10. F100 PUNT1 EQU 00F100H

11. F102 NUCAR EQU 00F102H

12. F104 CANAL EQU 00F104H

13. F106 GRIX EQU 00F106H

14. F108 TEST EQU 00F108H

15. F7F8 PMDRA EQU 00F7F8H

16. F7F9 PMCRA EQU 00F7F9H

17. F7FA PMDRB EQU 00F7FAH

18. F7FB PMCRB EQU 00F7FBH

19. F7FE AMCE EQU 00F7FEH

20. F7FF AMEL EQU 00F7FFH

21. F800 R ORG 0F800H

22.

23.

24.

25. 0000F800 10CEF3FF START LDS #0F3FFH

26. 0000F804 B0F9A7 R JSR INPIA ;INICIALIZACION DE PIA

27. 0000F807 B0F9C1 R JSR INACIA ;INICIALIZACION DE ACIA

28. 0000F80A 1A10 IN ORCC #0010H ; INHIBE IRQ

29. 0000F80C B6F7F8 COOP LIA PMDRA ;

30. 0000F80F 48 ASLA ;

31. 0000F810 48 ASLA ; LAZO DE ESPERA DE COMIENZO OPERACION

32. 0000F811 48 ASLA ;

33. 0000F812 48 ASLA ;

34. 0000F813 24F7 BCC COOP ; SI PA4=1 SALTAR

35. 0000F815 4F CLRA ; INICIALIZACION DEL PUNTERO DE

36. 0000F816 B7F108 STA TEST ; INTERRUPCIONES. IRQ=0, NMI=1.

37. 0000F819 8600 LIA #0DH

38. 0000F81B B7F7FF STA AMEL

39. 0000F81E B0F99F R JSR VIPE

40. 0000F821 860A LIA #0AH

41. 0000F823 B7F7FF STA AMEL

42. 0000F826 B0F99F R JSR VIPE

43. 0000F829 B0F996 R JSR MECA ; ENVIO DEL NO. DE CANALES

44. 0000F82C 8830 ADDA #30H

45. 0000F82E B0F99F R JSR VIPE

46. 0000F831 B7F7FF STA AMEL

47. 0000F834 860D LIA #0DH

48. 0000F836 B0F99F R JSR VIPE

49. 0000F839 B7F7FF STA AMEL

50. 0000F83C 860A LIA #0AH

51. 0000F83E B0F99F R JSR VIPE

52. 0000F841 B7F7FF STA AMEL ; ENVIO DE C.R. Y L.F.

```

asm MC6809

V02.01-09 (8560)

```

53 0000F844 1CEF      ANDCC #00EFH ; PERMITE IRQ

54 0000F846 B6F108    OPER LDA TEST ;

55 0000F849 27FB      BEQ OPER      ; A LA ESPERA DE IRQ Y NMI

56 0000F84B 7EF80A    R   JMP IN       ; SI NMI, COMIENZO

57

58 ; SUBRUTINA DE FINAL DE MEDIDA(NMI)

59

60 0000F84E 8658      R   LDA #58H   ;

61 0000F850 BDF99F    R   JSR VIPE   ;

62 0000F853 B7F7FF    R   STA AMEL   ; ENVIO DE [X] SENAL FIN DE OPERACION

63 0000F856 8620      R   LDA #020H   ;

64 0000F858 BDF99F    R   JSR VIPE   ;

65 0000F85B B7F7FF    R   STA AMEL   ; ENVIO DE --

66 0000F85E 8646      R   LDA #46H   ;

67 0000F860 BDF99F    R   JSR VIPE   ;

68 0000F863 B7F7FF    R   STA AMEL   ;

69 0000F866 8649      R   LDA #49H   ;

70 0000F868 BDF99F    R   JSR VIPE   ;

71 0000F86B B7F7FF    R   STA AMEL   ;

72 0000F86E 864E      R   LDA #4EH   ;

73 0000F870 BDF99F    R   JSR VIPE   ;

74 0000F873 B7F7FF    R   STA AMEL   ; ENVIO DE CARTEL:FIN

75 0000F876 8620      R   LDA #20H   ;

76 0000F878 BDF99F    R   JSR VIPE   ;

77 0000F87B B7F7FF    R   STA AMEL   ;

78 0000F87E B6F108    R   LDA TEST   ;

79 0000F881 4C         R   INCA      ;

80 0000F882 B7F108    R   STA TEST   ;

81 0000F885 3B         R   RTI       ;

82

83 ; SUBRUTINA DE MEDIDA(IRQ)

84

85 0000F886 B6F7F9    R   LDA PMCRA  ;

86 0000F889 48         R   ASLA      ;

87 0000F88A 246E      R   BCC AUX    ; SI NO IRQ SALIR

88 0000F88C 5F         R   CLR B    ;

89 0000F88D 53         R   COMB     ;

90 0000F88E F7F100    R   STB PUNTI ;

91 0000F891 8E30D4    R   LDX #12500  ;

92 0000F894 301F      R   RET1 LEAX -1,X ; RETARDO DE 100 MS

93 0000F895 26FC      R   BNE RET1  ;

94 0000F898 BDF996    R   JSR MECA ; MEDIDA DEL NUMERO DE CANALES

95 0000F89B 8EF000    R   LDX #0F000H ; PUNTERO DE DATOS

96 0000F89E BDF907    R   JSR TOMA ; MEDIDA DEL PRIMER CANAL

97 0000F8A1 B6F104    R   LDA CANAL ;

98 0000F8A4 2713      R   BEQ FIN1 ; SI UN CANAL, SALIR

99 0000F8A6 BDF907    R   JSR TOMA ; MEDIDA DEL SEGUNDO CANAL

100 0000F8A9 B6F104    R   LDA CANAL ;

101 0000F8AC 270B      R   BEQ FIN1 ; SI DOS CANALES, SALIR

102 0000F8AE BDF907    R   JSR TOMA ; MEDIDA DEL TERCER CANAL

103 0000F8B1 B6F104    R   LDA CANAL ;

104 0000F8B4 2703      R   BEQ FIN1 ; SI TRES CANALES SALIR

```

asm MC6809

U02.01-09 (8560)

105 0000F8B6 BDF907 R JSR TOMA ; MEDIDA DEL CUARTO CANAL

106 0000F8B9 BDF996 R FIN1 JSR MECA

107 0000F8BC 8EF000 LIX \*0F000H

108 0000F8BF 4F CLRA

109 0000F8C0 B7F102 STA NUCAR ;

110 0000F8C3 BDF969 R JSR SALIDA ; SALIDA DE DATOS DEL PRIMER CANAL

111 0000F8C6 B6F104 LDA CANAL ;

112 0000F8C9 271F BEQ FIN2 ; SI UN CANAL, SALIR

113 0000F8CB 4F CLRA

114 0000F8CC B7F102 STA NUCAR

115 0000F8CF BDF969 R JSR SALIDA ; SALIDA DE DATOS DEL SEGUNDO CANAL.

116 0000F8D2 B6F104 LDA CANAL ;

117 0000F8D5 2713 BEQ FIN2 ; SI DOS CANALES, SALIR

118 0000F8D7 4F CLRA

119 0000F8D8 B7F102 STA NUCAR

120 0000F8D8 BDF969 R JSR SALIDA ; SALIDA DE DATOS DEL TERCER CANAL

121 0000F8D8 B6F104 LDA CANAL ;

122 0000F8E1 2707 BEQ FIN2 ; SI TRES CANALES, SALIR

123 0000F8E3 4F CLRA

124 0000F8E4 B7F102 STA NUCAR

125 0000F8E7 BDF969 R JSR SALIDA ; SALIDA DE DATOS DEL CUARTO CANAL.

126 0000F8EA 860D FIN2 LDA \*0DH

127 0000F8EC BDF99F R JSR VIFE

128 0000F8EF B7F7FF STA AMEL ; ENVIO DEL RETORNO DE CARRO

129 0000F8F2 860A LDA \*0AH

130 0000F8F4 BDF99F R JSR VIFE

131 0000F8F7 B7F7FF STA AMEL ; ENVIO DE L.F.

132 0000F8FA 1CEF AUX ANDCC \*00EFH ; PERMITE IRQ

133 0000F8FC 8635 LDA \*35H ;

134 0000F8FE B7F7F9 STA PMCRA ;

135 0000F901 863D LDA \*3DH ;

136 0000F903 B7F7F9 STA PMCRA ; SET-RESET: ORDEN DISPARO MONOCROM.

137 0000F906 3B RTI

138 ;

139 ; SUBRUTINA DE TOMA DE DATOS

140 ;

141 0000F907 F6F100 TOMA LDB PUNTI ;

142 0000F90A F7F7FA STB PMDRB ; MULTIFLEXADO

143 0000F90D BFF105 STX GRIX ;

144 0000F910 8EF424 LDX \*62500 ;

145 0000F913 301F DES LEAX -1,X ;

146 0000F915 26FC BNE DES ; RETARDO DE 500MS.

147 0000F917 BEF106 LDX GRIX ;

148 0000F91A 863D LDA \*3DH ;

149 0000F91C B7F7FB STA PMCRA ; B.II ALTO (MEDIDA BLOQUEADA)

150 0000F91F B6F7F8 LDA PMDRA ;

151 0000F922 43 COMA ;

152 0000F923 8403 ANDA \*03H ;

153 0000F925 A784 STA 0,X ; PRIMER CARACTER PUNTERO+0/6/12/18

154 0000F927 C020 SUBB \*20H ;

155 0000F929 F7F7FA STB PMDRB ;

156 0000F92C B6F7F8 LDA PMDRA

asm MC6809

V02.01-09 (8560)

```

157 0000F92F 43          COMA          ;

158 0000F930 8401          ANDA #01H ;

159 0000F932 3001          LEAX 1,X ;

160 0000F934 A784          STA 0,X ; SGDO. CARACTER PUNTERO+1/7/13/19

161 0000F936 B0F959          R   JSR CARGA ; TERCER CARACTER PUNTERO+2/8/14/20

162 0000F939 B0F959          R   JSR CARGA ; CUARTO CARACTER PUNTERO+3/9/15/21

163 0000F93C B0F959          R   JSR CARGA ; QUINTO CARACTER PUNTERO+4/10/16/22

164 0000F93F B0F959          R   JSR CARGA ; SEXTO CARACTER PUNTERO+5/11/17/23

165 0000F942 B6F104          LDA CANAL

166 0000F945 4A          DECA

167 0000F946 B7F104          STA CANAL

168 0000F949 8635          LDA #35H ;

169 0000F94B B7F7FB          STA FMCRB ; B.I. ALTO

170 0000F94E F6F100          LDB PUNT1 ;

171 0000F951 C008          SUBB #08H ; MULTIPLEXADO DE CANALES

172 0000F953 F7F100          STB PUNT1 ;

173 0000F956 3001          LEAX 1,X

174 0000F958 39          RTS

175

176

177

178 0000F959 C020          ;

179 0000F95B F7F7FA          CARGA SUBB #20H

180 0000F95E B6F7F8          STB FMDRB

181 0000F961 43          LDA FMDRB

182 0000F962 840F          COMA

183 0000F964 3001          ANDA #0FH

184 0000F966 A784          LEAX 1,X

185 0000F968 39          STA 0,X

186

187

188

189 0000F969 A6B4          RTS

190 0000F96B 8B30          ;

191 0000F96D B0F99F          R   SALIDA LDA 0,X

192 0000F970 B7F7FF          ADDA #30H

193 0000F973 3001          JSR VIPE

194 0000F975 B6F102          STA AMEL ; ENVIO CAR. (SIGNO-ERROR+MSB+1+2+3+4)

195 0000F978 4C          LEAX 1,X

196 0000F979 B7F102          LDA NUCAR

197 0000F97C 8006          INCA

198 0000F97E 2DE9          STA NUCAR ; NUMERO CARACTERES ENVIADOS(DIGITOS)

199 0000F980 8620          SUBA #6H

200 0000F982 B0F99F          BLT SALIDA ; SI<6 VOLVER

201 0000F985 B7F7FF          LDA #20H

202 0000F988 B0F99F          JSR VIPE

203 0000F98B B7F7FF          STA AMEL ; ENVIO DE UN BLANCO

204 0000F98E F6F104          LDB CANAL

205 0000F991 5A          DECB

206 0000F992 F7F104          STB CANAL

207 0000F995 39          RTS

208

```

asm MC6809

V02.01-09 (8560)

```

209          ; SUBRUTINA DE MEDIDA DE CANALES

210          ;

211 0000F996 B6F7FA  MECA LIA PMDRB

212 0000F999 8407    ANDA #07H ; SOLO B0/1/2

213 0000F99B B7F104  STA CANAL

214 0000F99E 39      RTS

215          ;

216          ; SUBRUTINA DE VIGILANCIA DE REGISTRO DE DATOS

217          ;

218 0000F99F F6F7FE  VIPE LDB AMCE

219 0000F9A2 57      ASRB

220 0000F9A3 57      ASRB

221 0000F9A4 24F9    BCC VIPE ; SI BIT=1 SALIR (TDR VACIO)

222 0000F9A6 39      RTS

223          ;

224          ; SUBRUTINA DE INICIALIZACION DE PIAS

225          ;

226 0000F9A7 7FF7F9  INPIA CLR PMCRA

227 0000F9AA 7FF7FB  CLR PMCRA

228 0000F9AD 4F      CLRA

229 0000F9AE B7F7F8  STA PMDRA ; SECCION A TODO ENTRADAS

230 0000F9B1 86F8    LIA #00F8H

231 0000F9B3 B7F7FA  STA PMDRB ; SECCION B TODO SALIDAS EXC. PB0/1/2

232 0000F9B6 863D    LIA #3DH

233 0000F9B8 B7F7F9  STA PMCRA ; CA2 SAL. ALTA, IRQ->CA1, SET-RESET (3D-35)

234 0000F9BB 8635    LIA #35H

235 0000F9BD B7F7FB  STA PMCRA ; CB2 SAL. BAJA, IRQ->CB1, SET-RESET (35-3D)

236 0000F9C0 39      RTS

237          ;

238          ; INICIALIZACION DE ACIA

239          ;

240 0000F9C1 C603    INACIA LDB #03H ; MASTER RESET

241 0000F9C3 F7F7FE  STB AMCE

242 0000F9C6 C615    LDB #15H

243 0000F9C8 F7F7FE  STB AMCE ; (IRQ+RTS)NO ; 8 BITS+NF+1 STOP; DIV. POR 16

244 0000F9CB 39      RTS

245          LIST DBG

246          END START

```