# **Audio Power Amplifier Techniques With Energy Efficient Power Conversion**

**Volume I**

Ph.D. Thesis

Karsten Nielsen

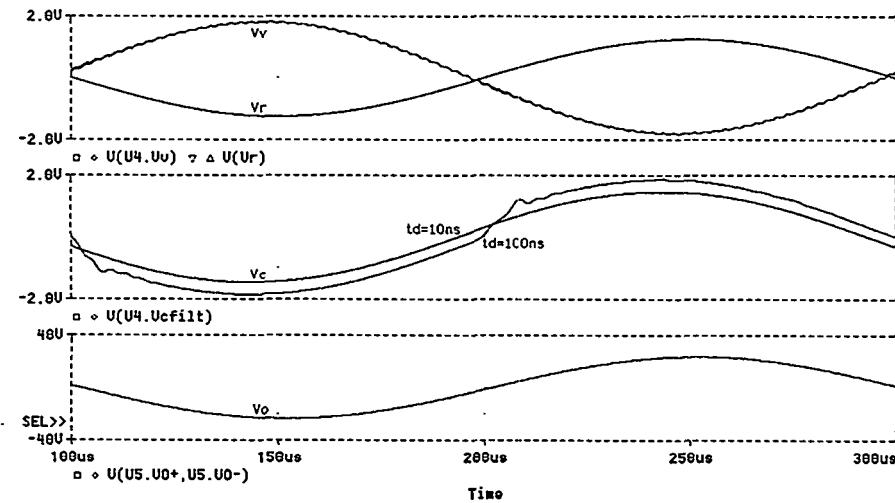

Department of Applied Electronics, Building 451

Technical University of Denmark

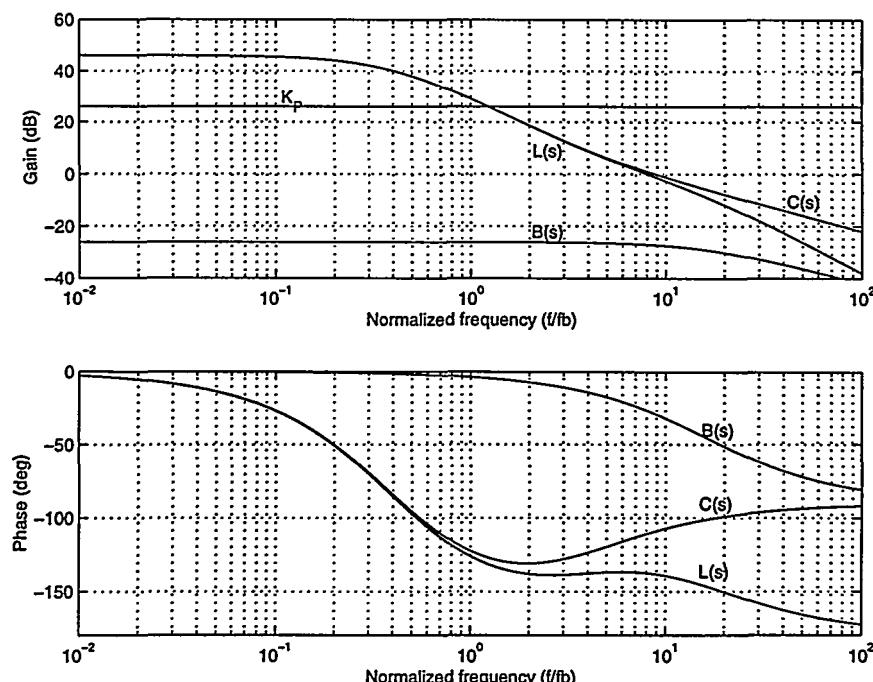

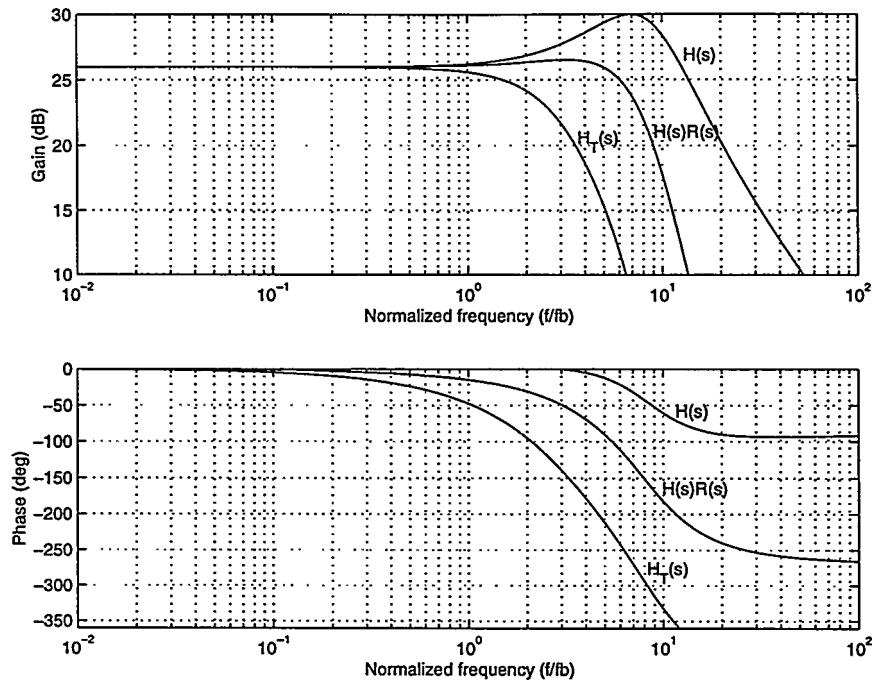

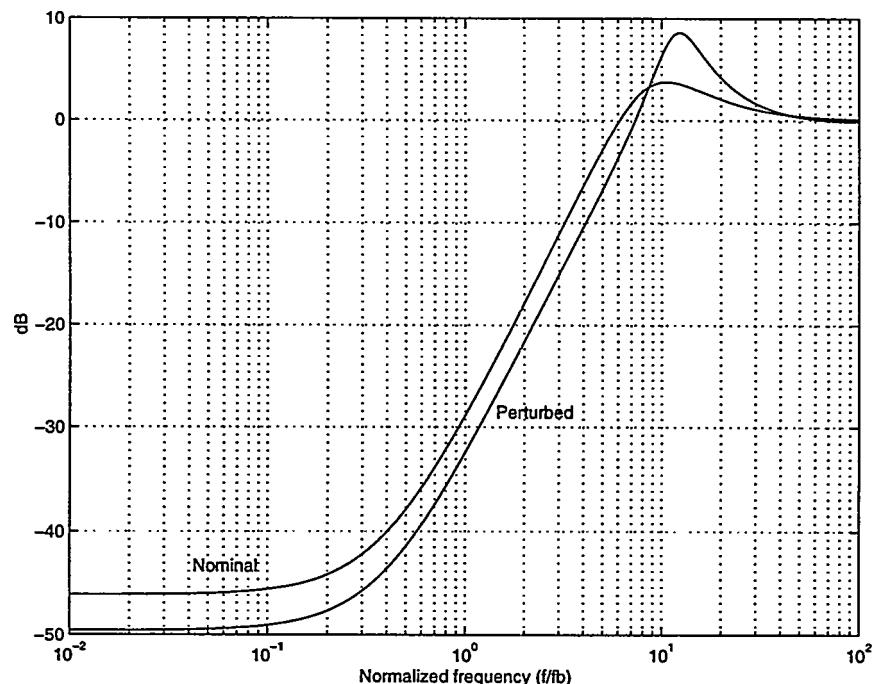

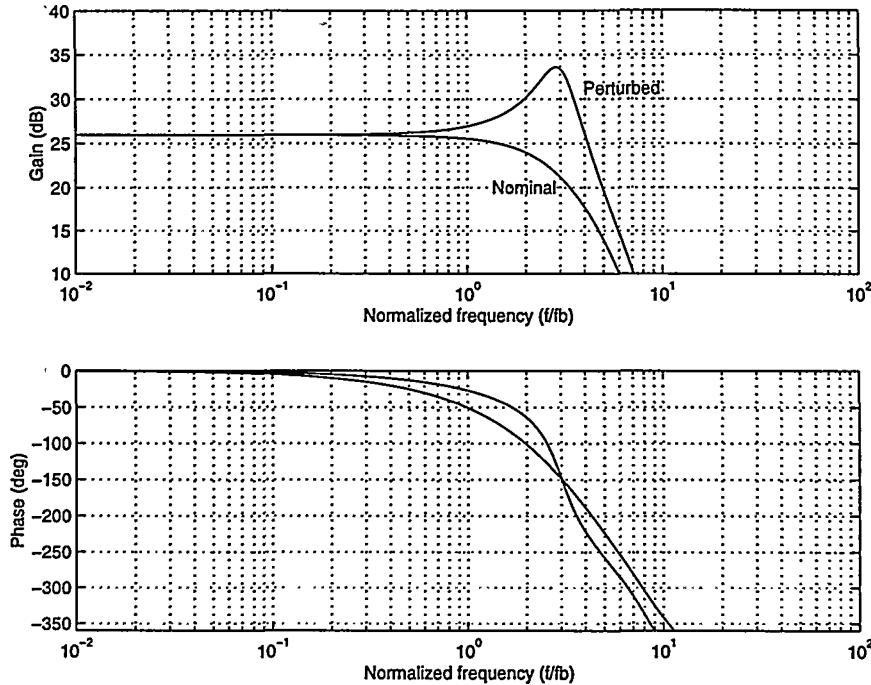

DK-2800 Lyngby

April 30, 1998

## **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

# Contents

## Preface

## Abstract

## Resumé på dansk

|                                                                   |    |

|-------------------------------------------------------------------|----|

| <b>Chapter 1 – Introduction .....</b>                             | 1  |

| Introduction .....                                                | 1  |

| 1.1 Audio power stage topologies .....                            | 2  |

| 1.1.1 Power and energy efficiency .....                           | 3  |

| 1.1.2 Energy efficiency considerations .....                      | 5  |

| 1.1.3 The switching (Class D) power stage topology .....          | 8  |

| 1.2 The Pulse Modulation Amplifier (PMA) .....                    | 9  |

| 1.2.1 Design problems and challenges .....                        | 10 |

| 1.2.2 Other considerations .....                                  | 11 |

| 1.3 Thesis structure .....                                        | 12 |

| <br>                                                              |    |

| <b>Chapter 2 – Analog Pulse Modulation .....</b>                  | 15 |

| 2.1 Fundamental pulse modulation methods .....                    | 15 |

| 2.2 Analog Pulse Density Modulation (PDM) .....                   | 17 |

| 2.3 Analog Pulse Width Modulation .....                           | 18 |

| 2.3.1 Analysis methodology .....                                  | 20 |

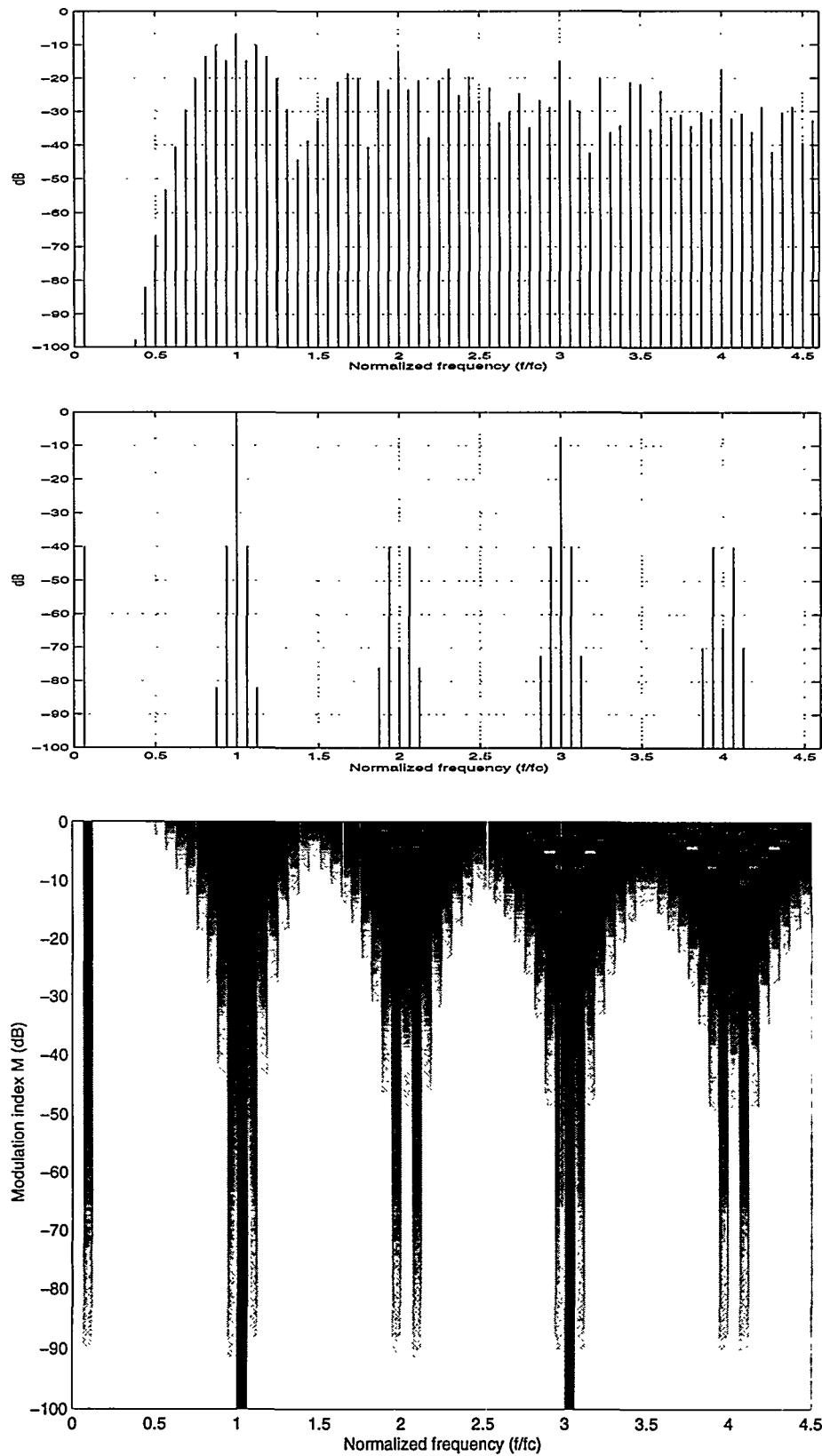

| 2.4 DFS synthesis for NPWM methods .....                          | 24 |

| 2.4.1 Analysis and comparison .....                               | 25 |

| 2.5 Phase Shifter Carrier PWM (PSCPWM) .....                      | 33 |

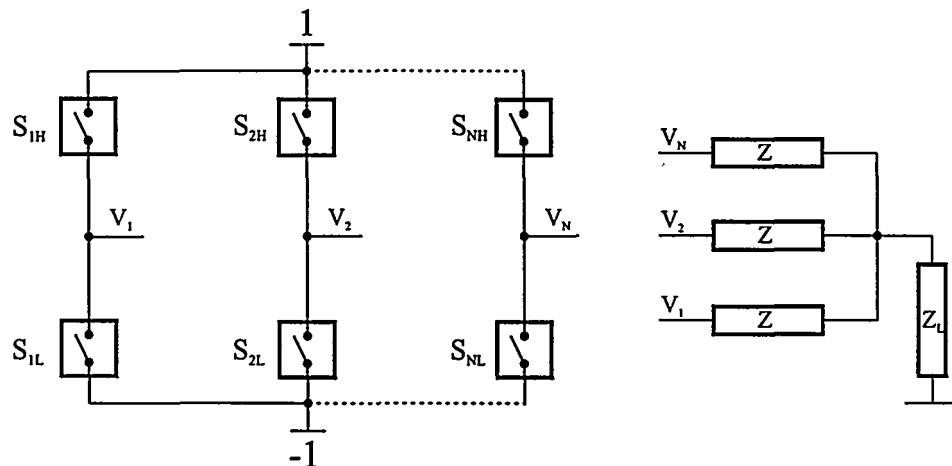

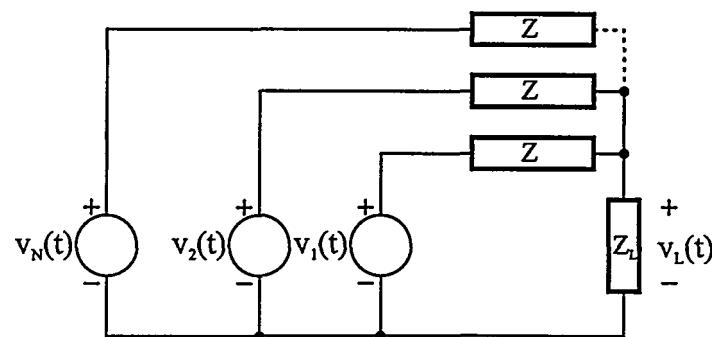

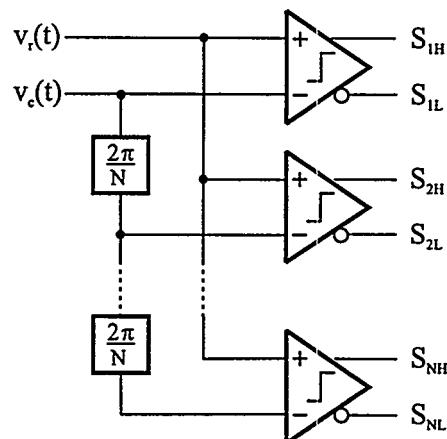

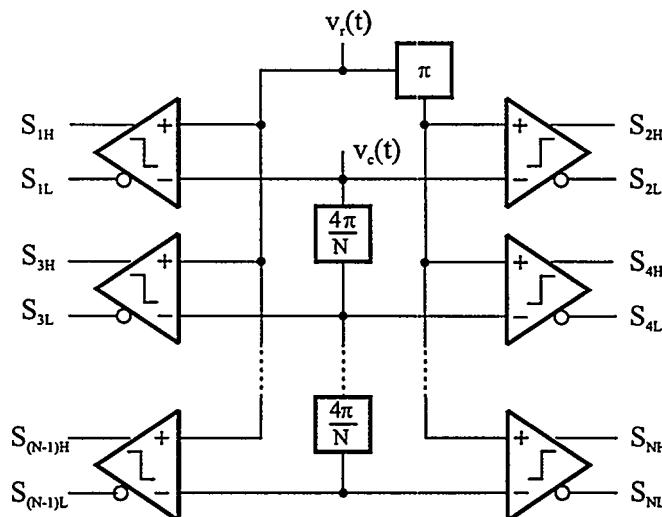

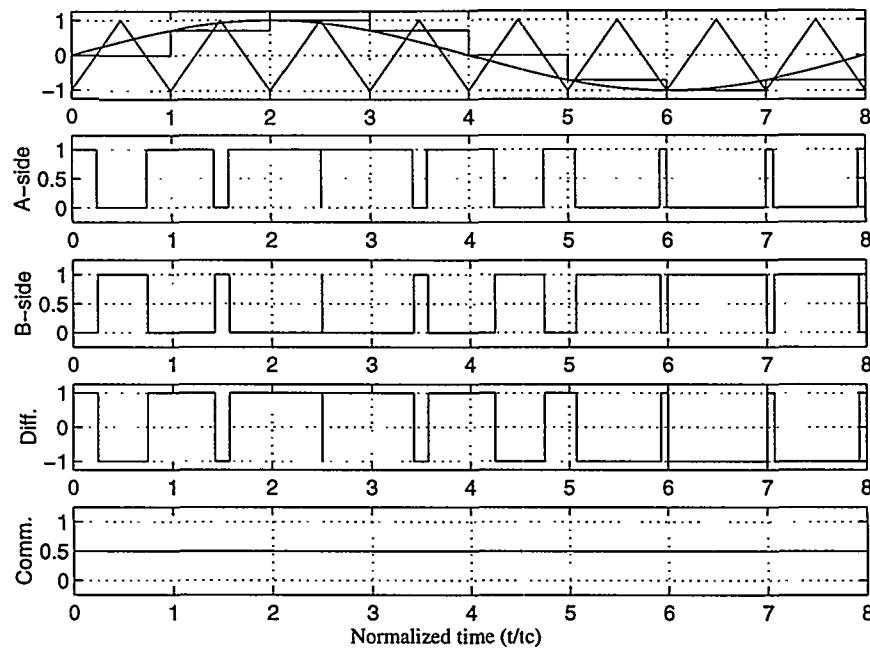

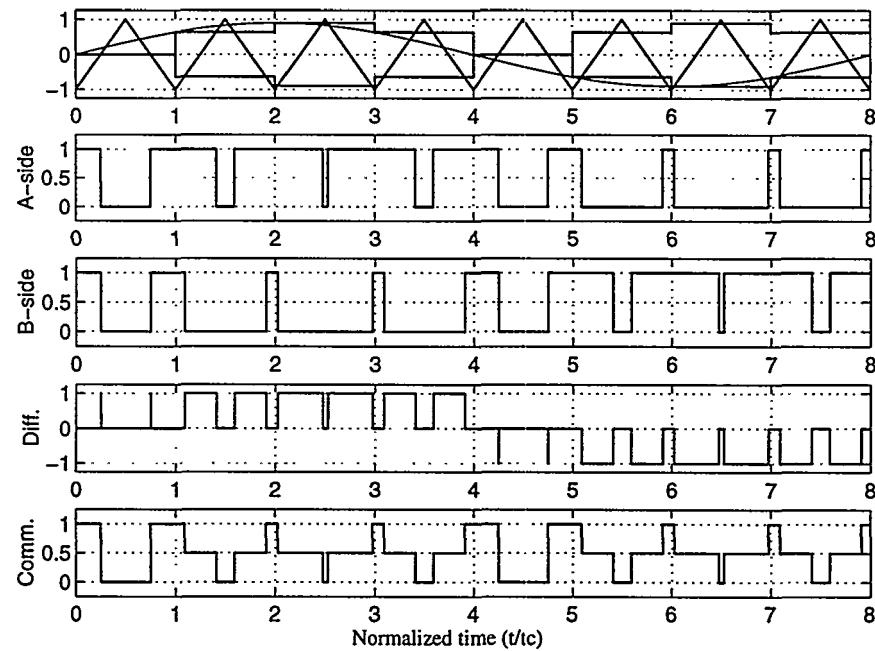

| 2.5.1 PSCPWM control algorithms .....                             | 34 |

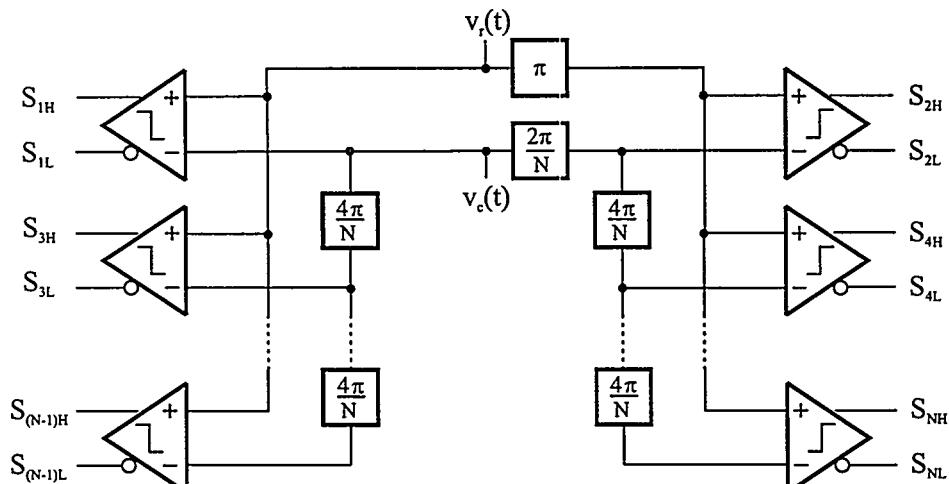

| 2.5.2 Control algorithms for balanced PSCPWM .....                | 37 |

| 2.6 PSCPWM analysis .....                                         | 40 |

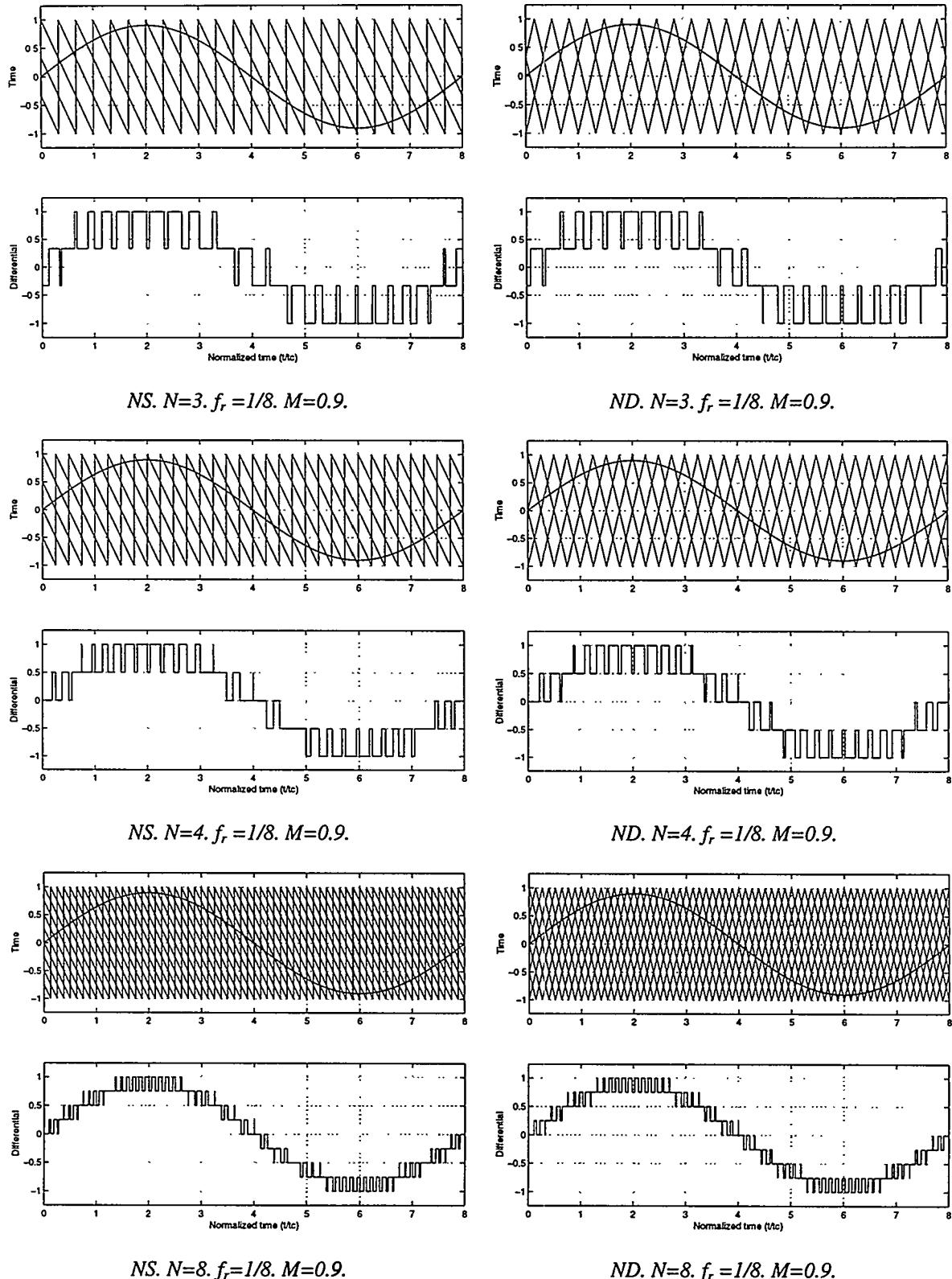

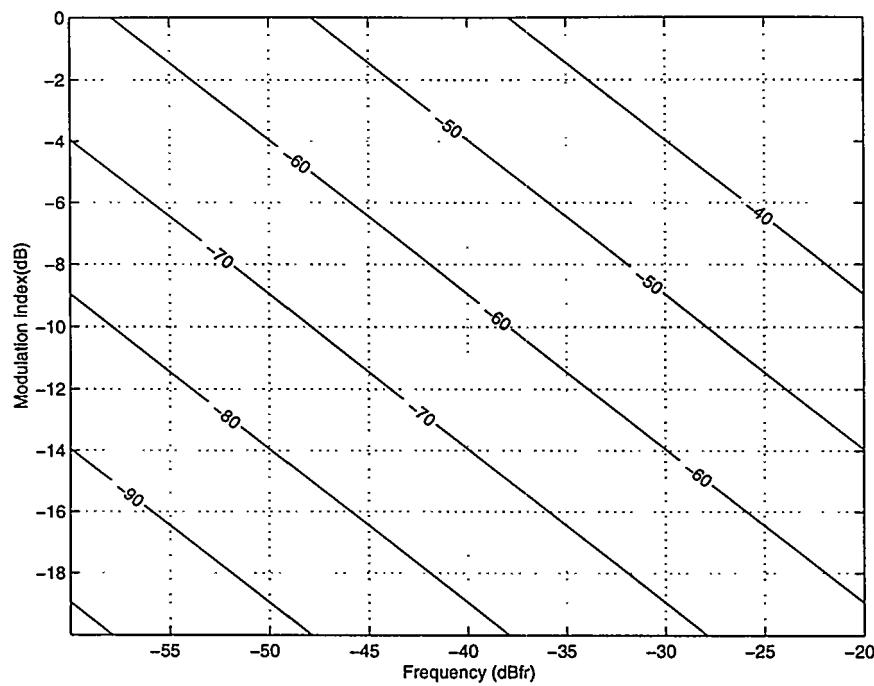

| 2.6.1 DFS synthesis for NS and ND .....                           | 40 |

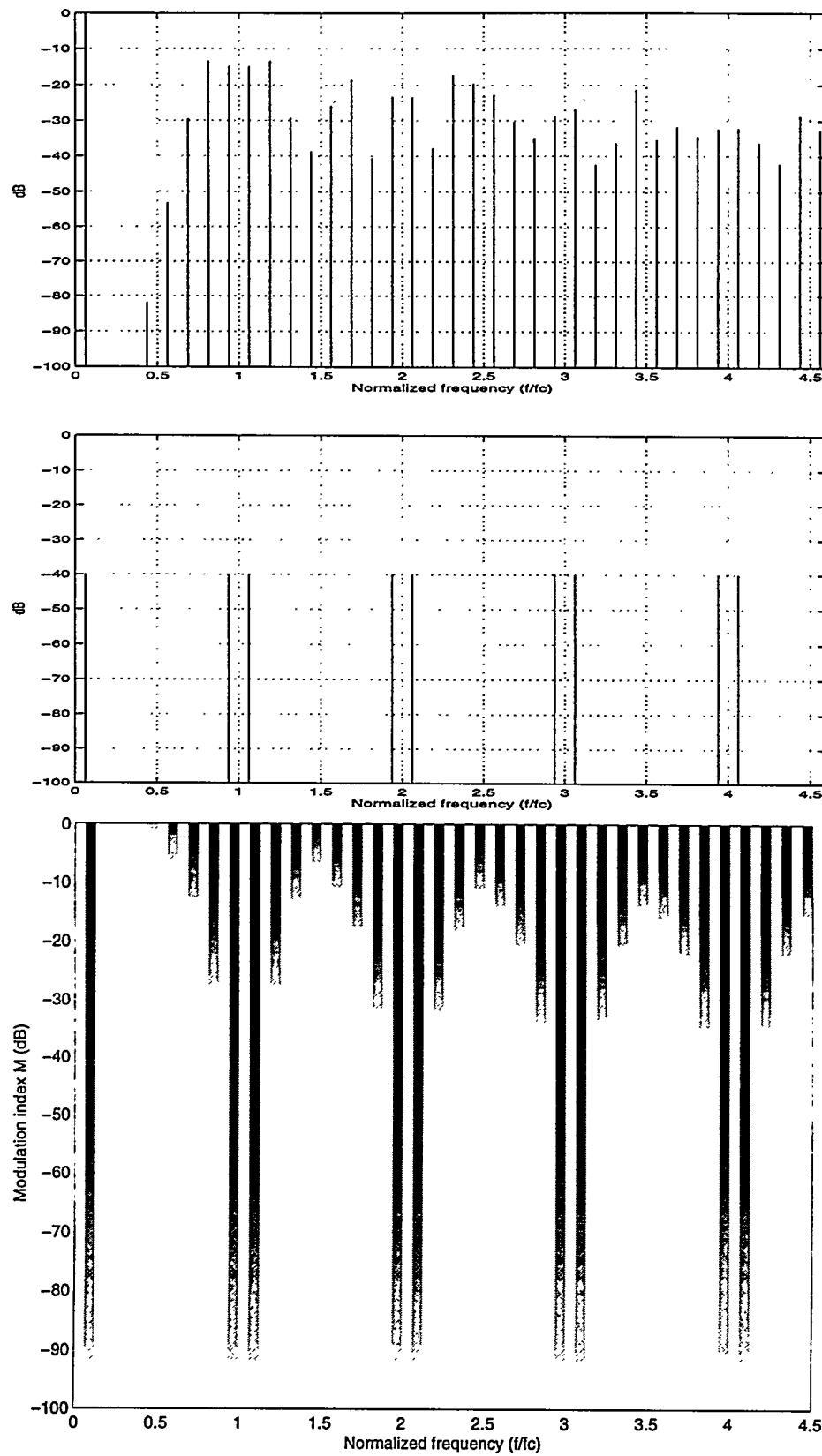

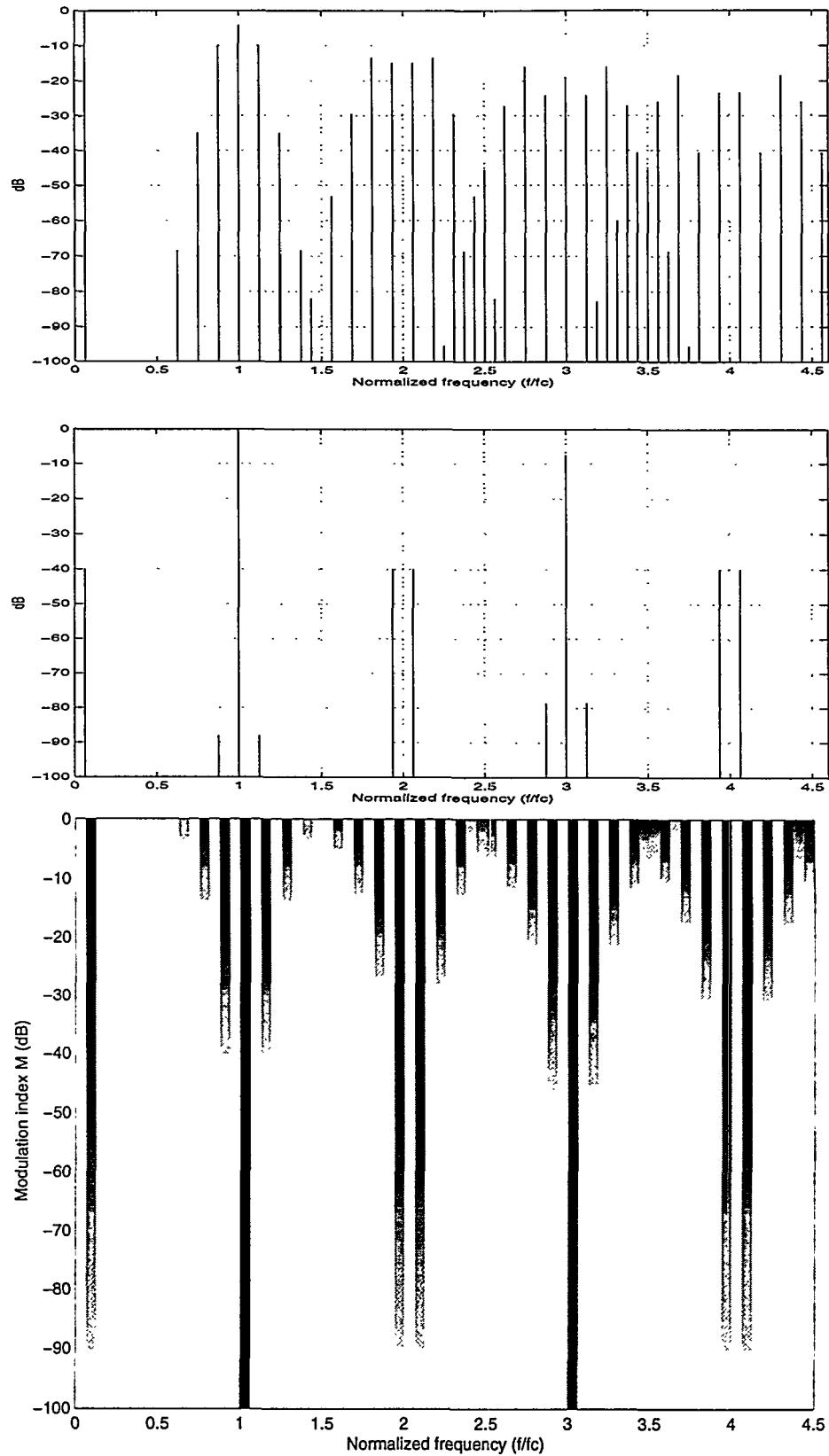

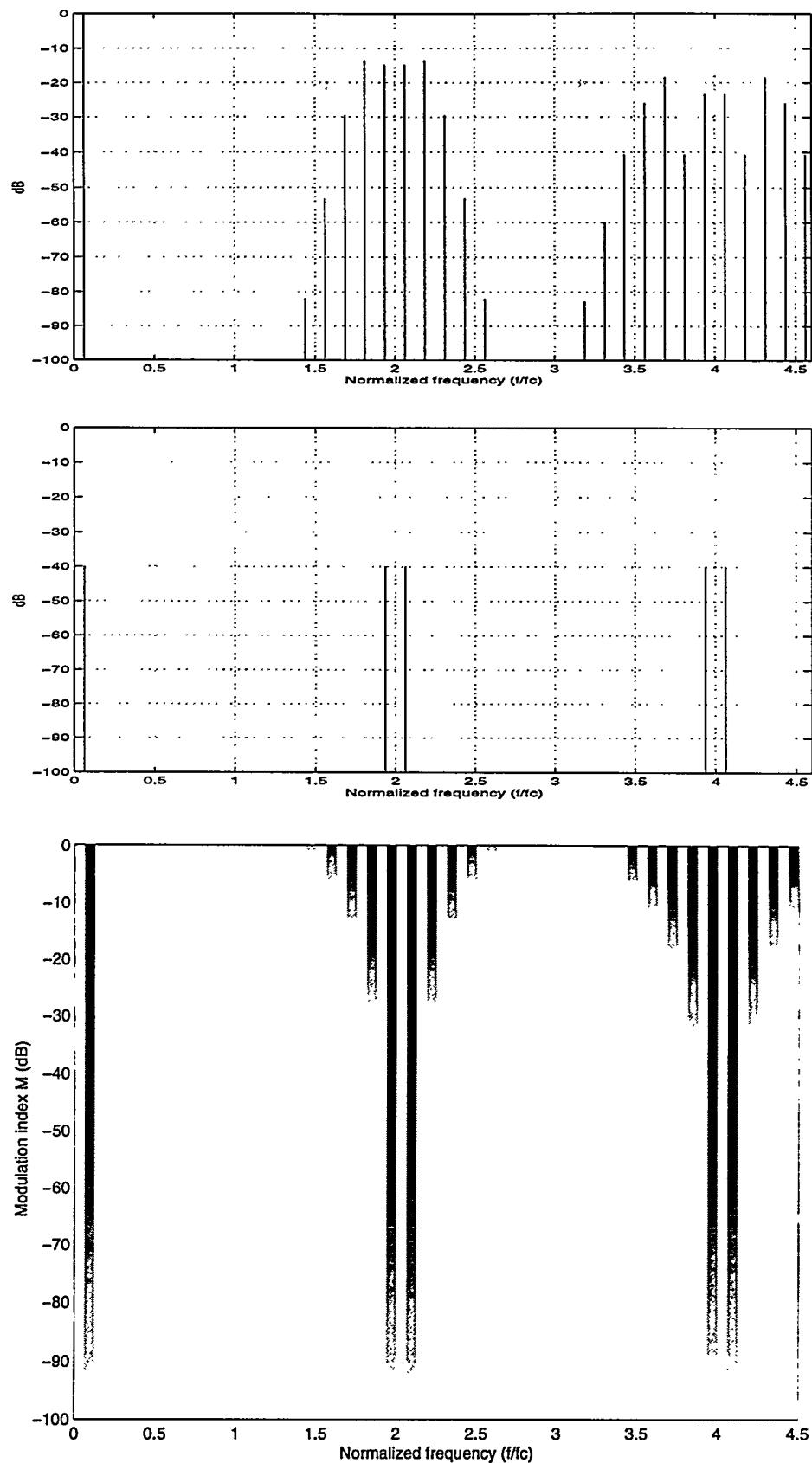

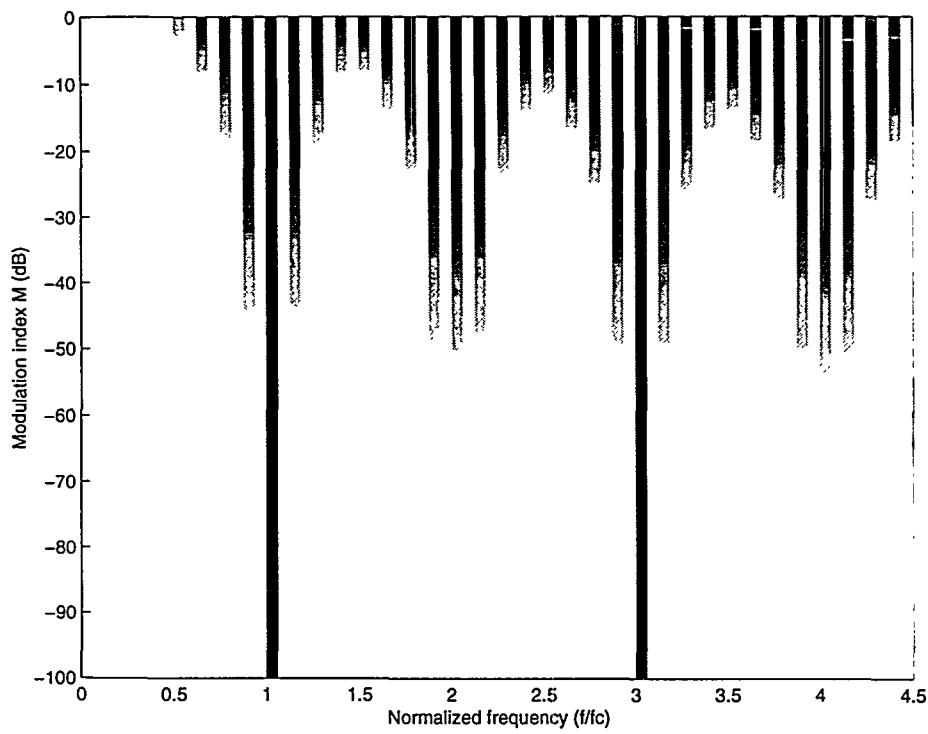

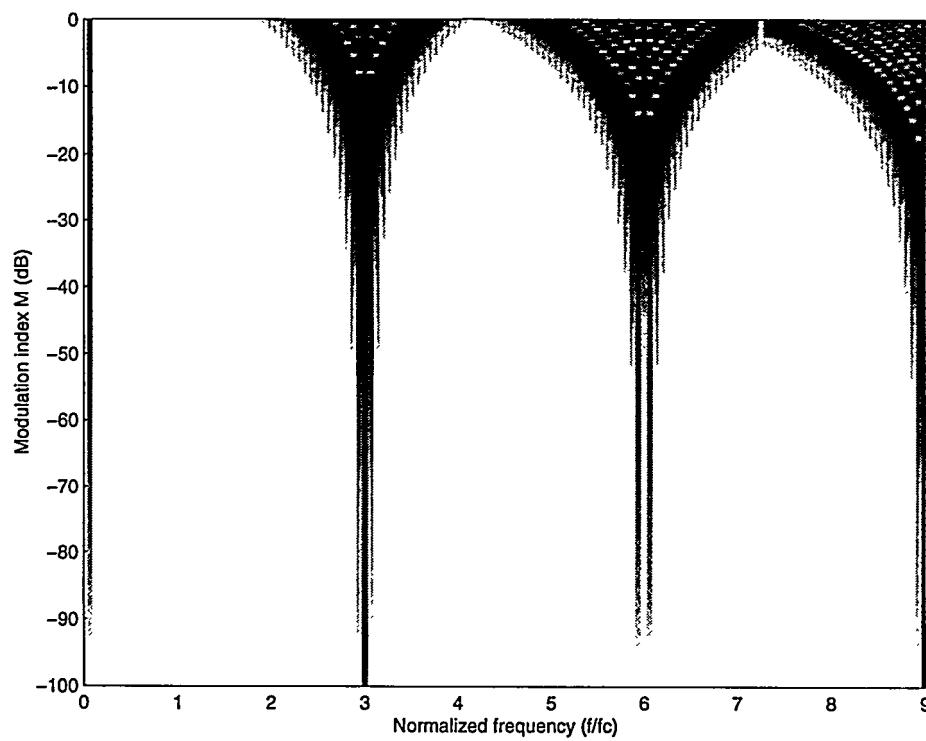

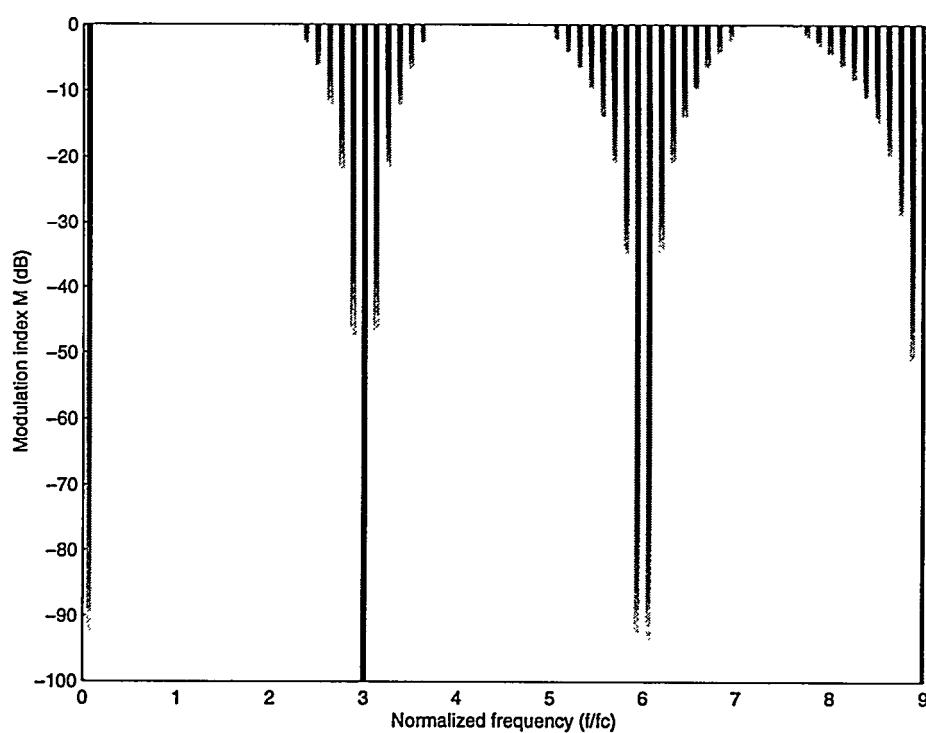

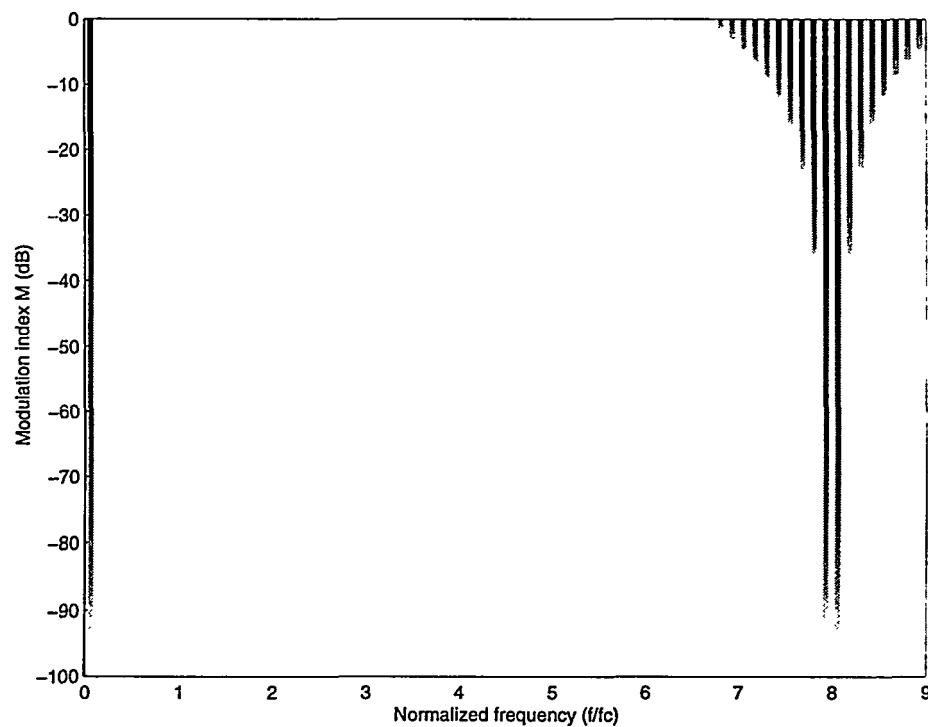

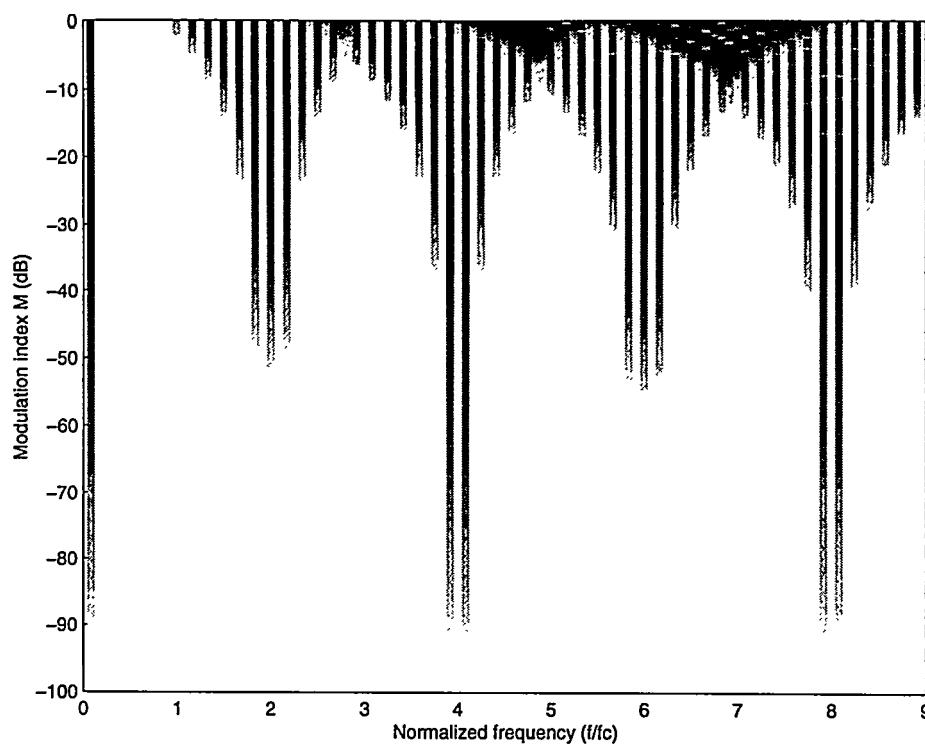

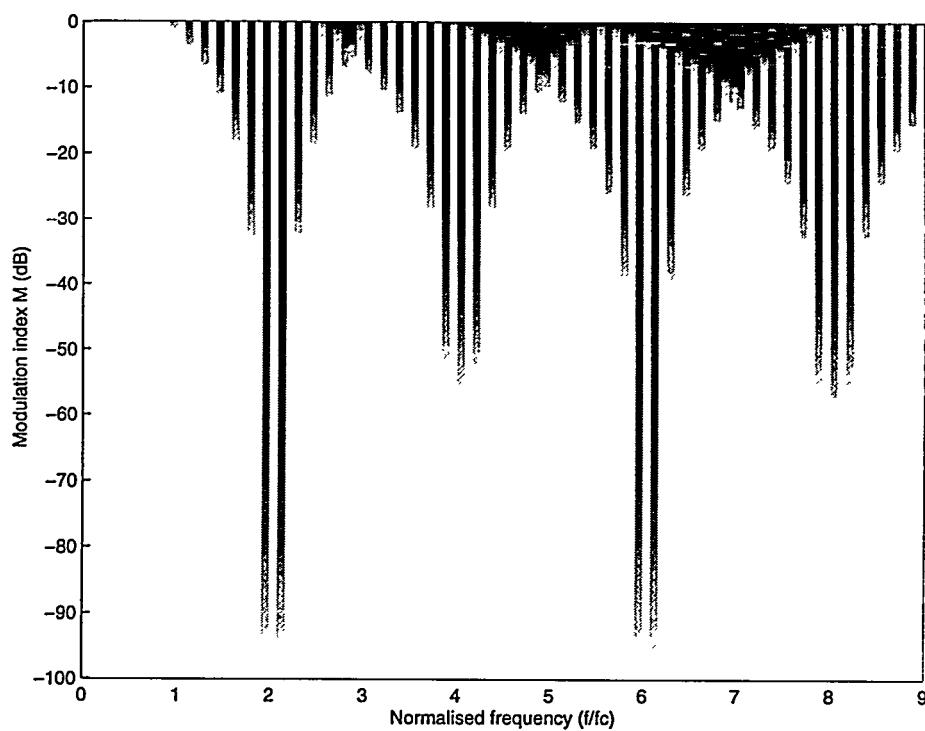

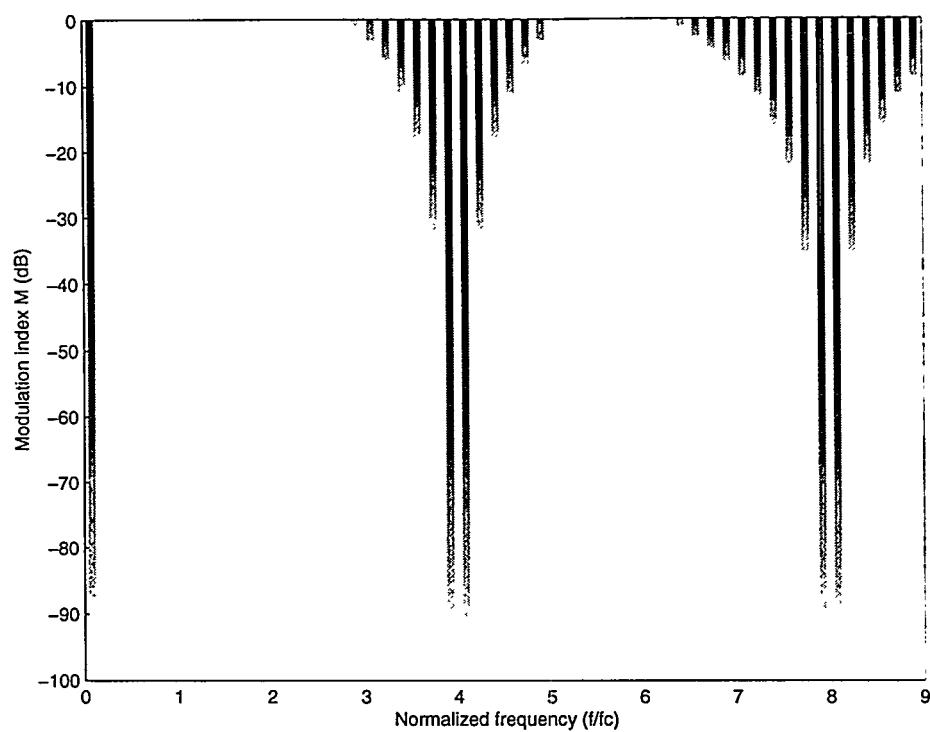

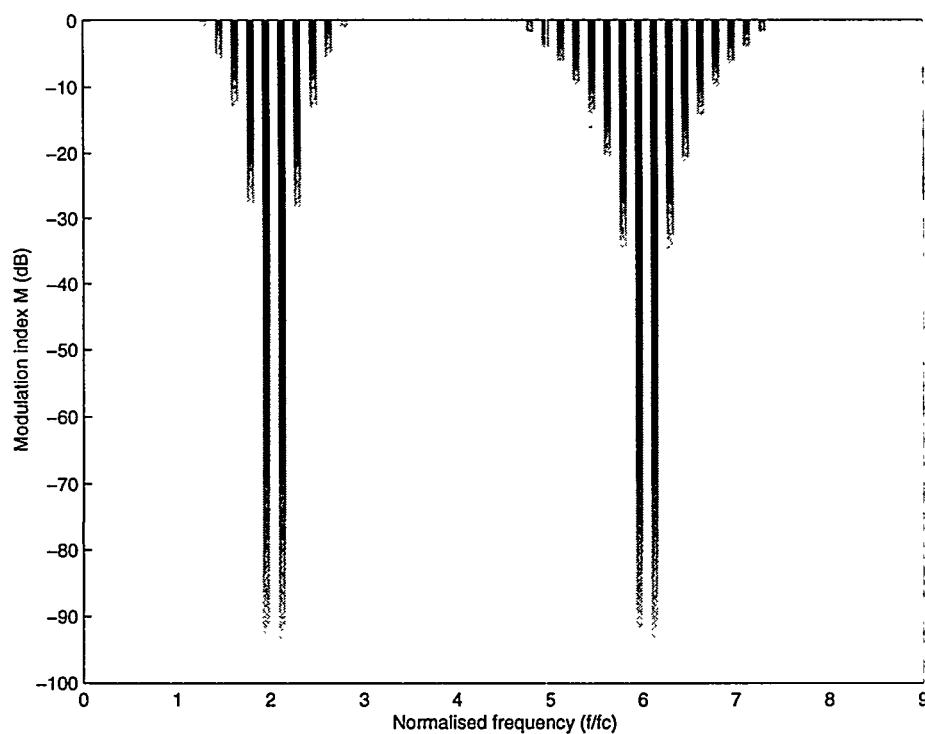

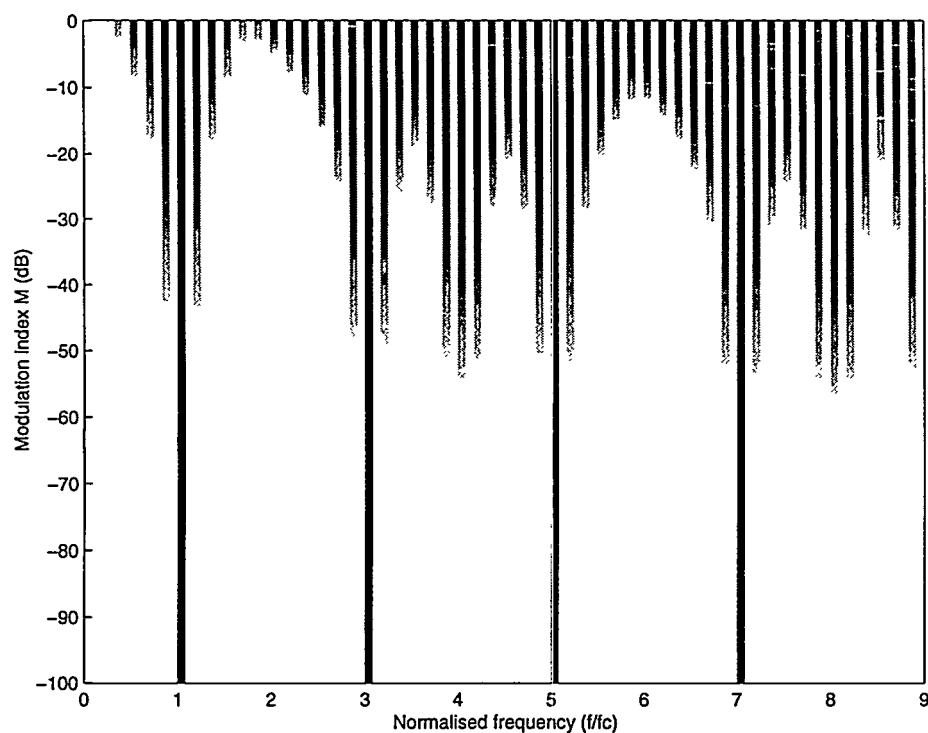

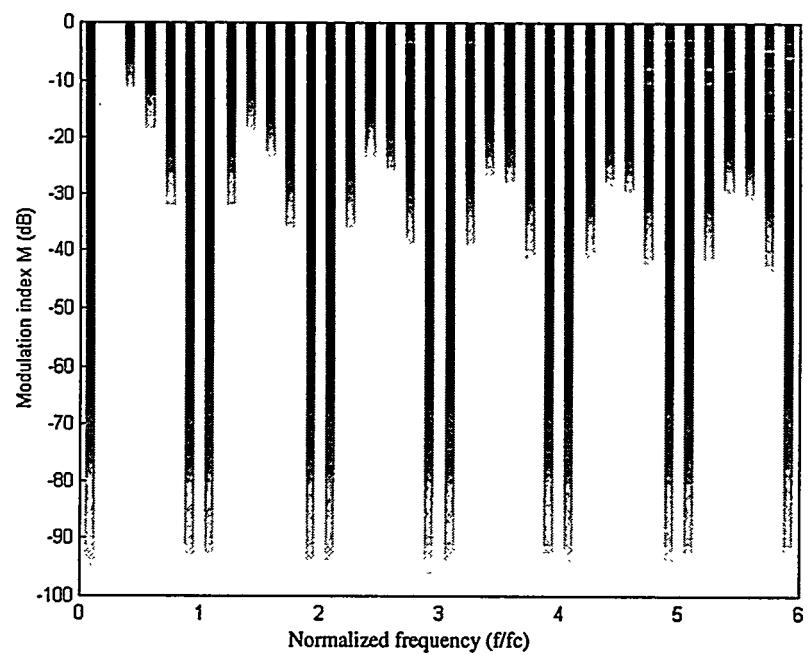

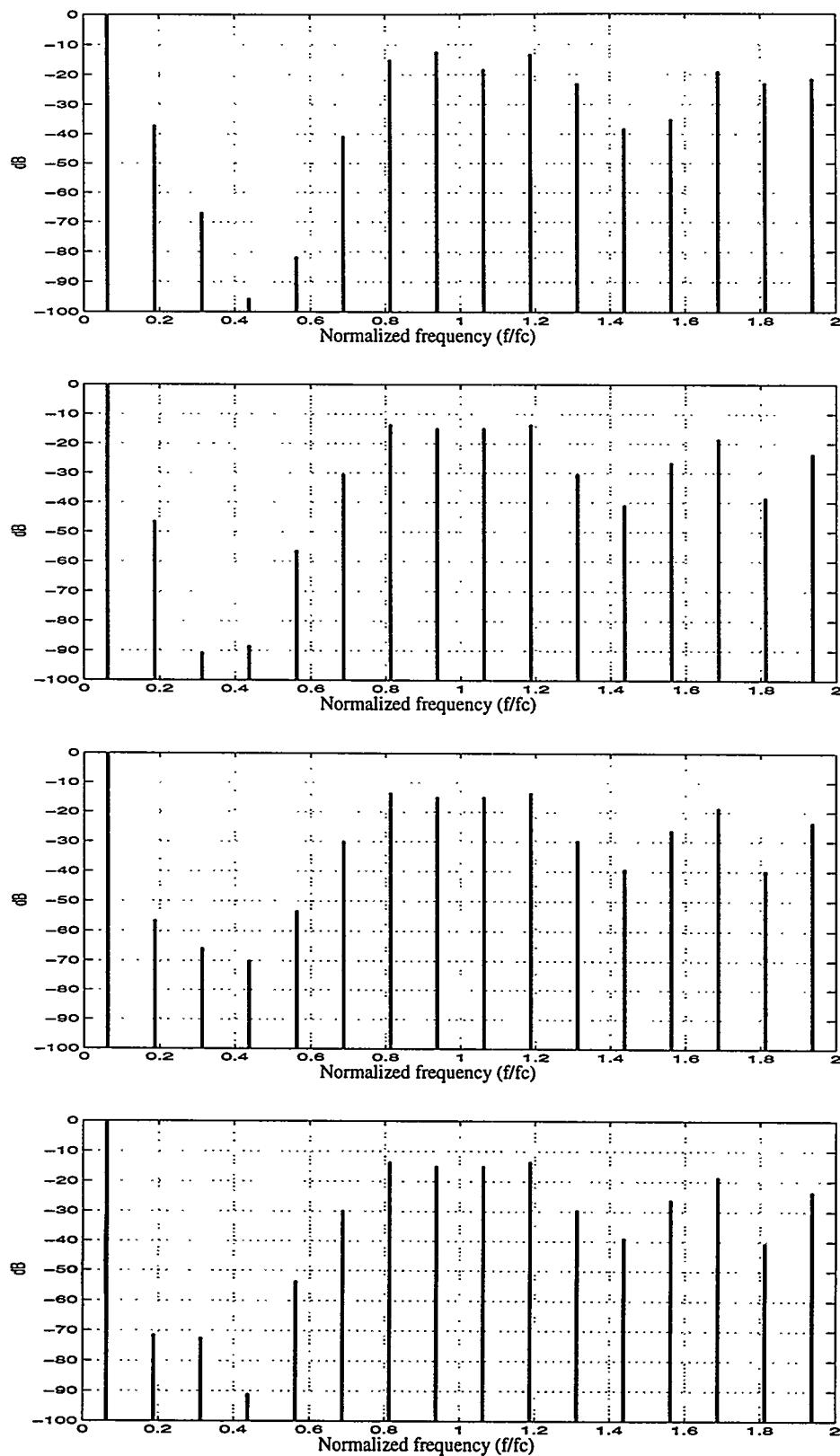

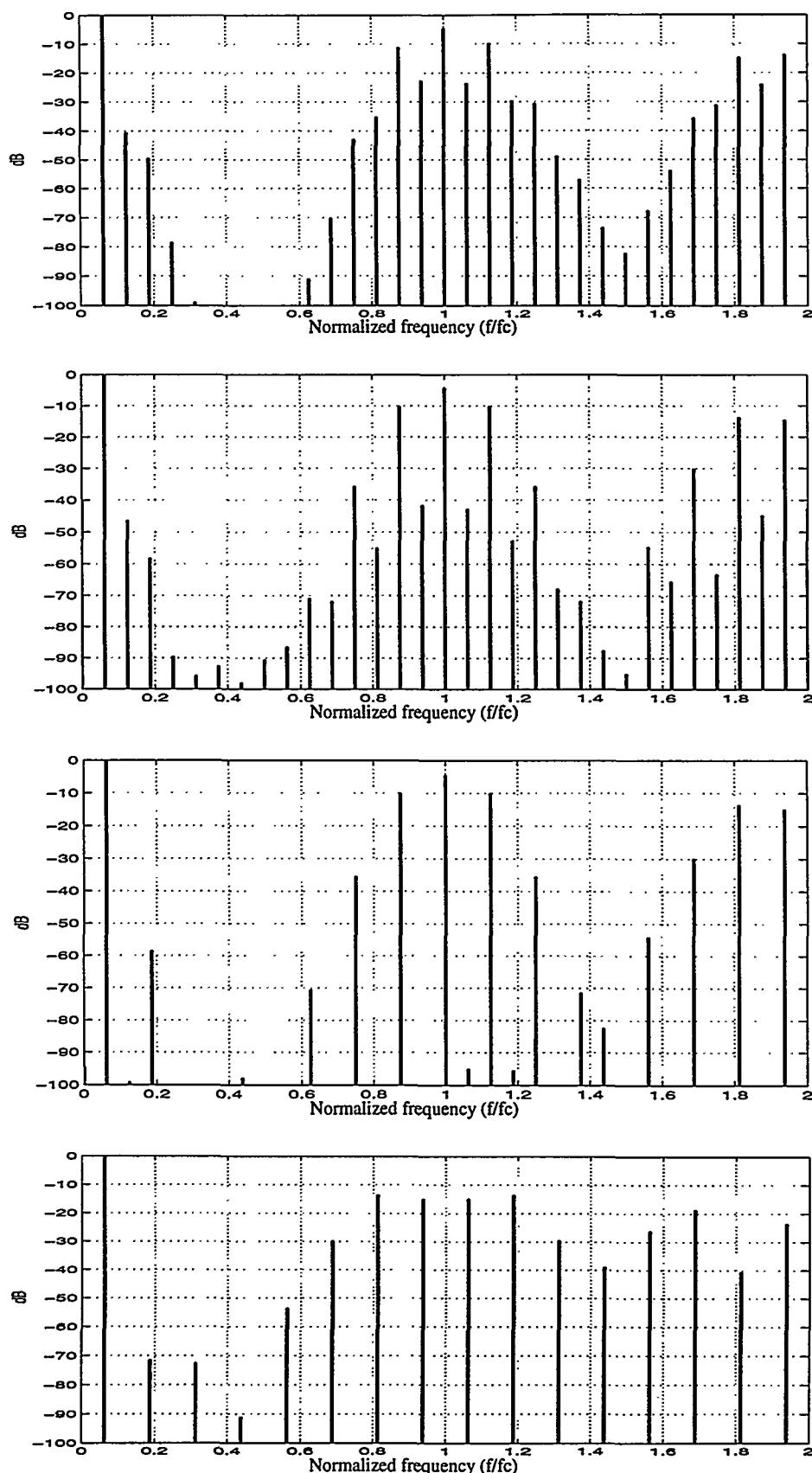

| 2.6.2 Spectral characteristics .....                              | 41 |

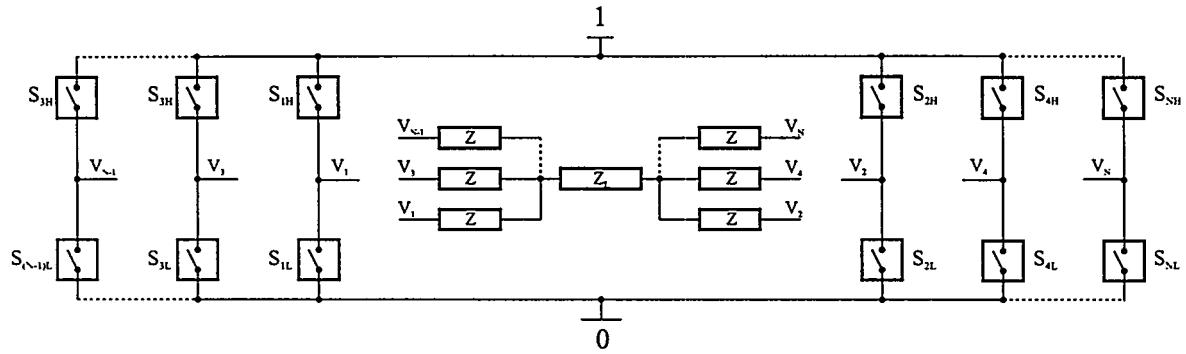

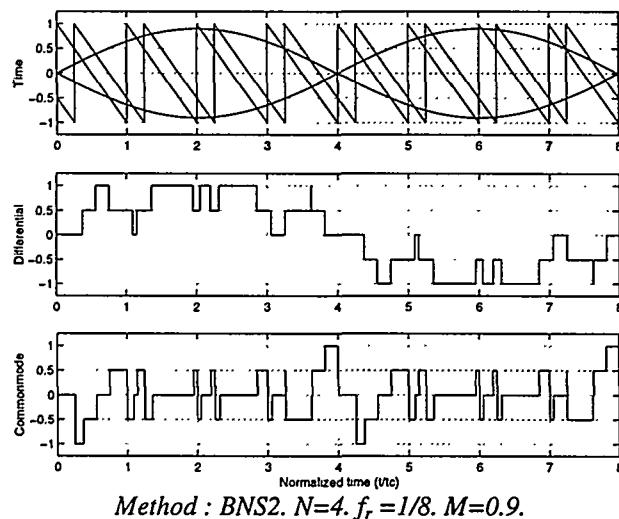

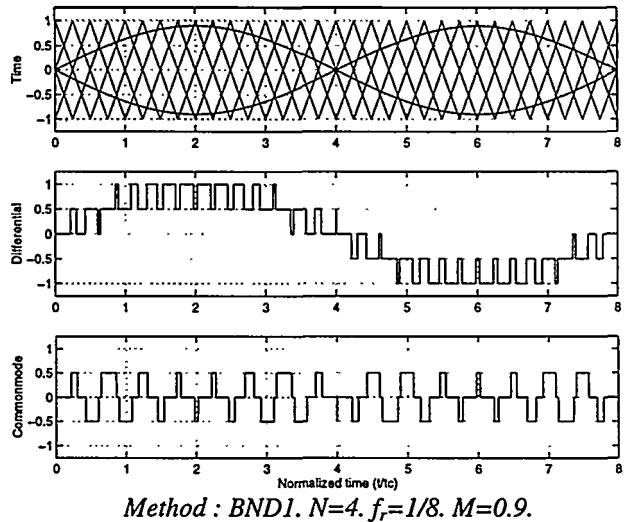

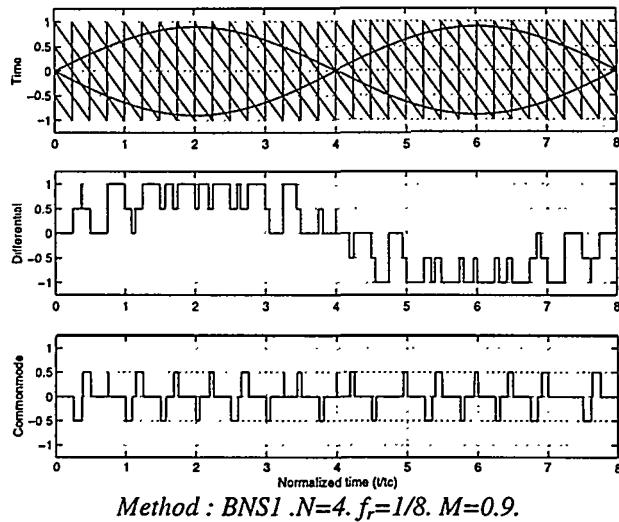

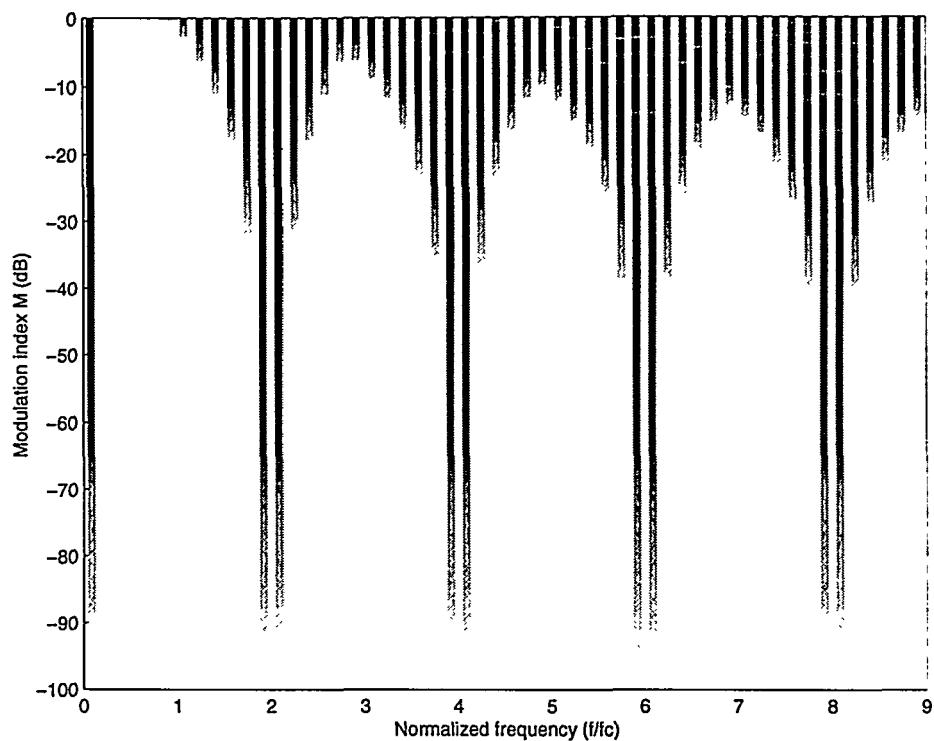

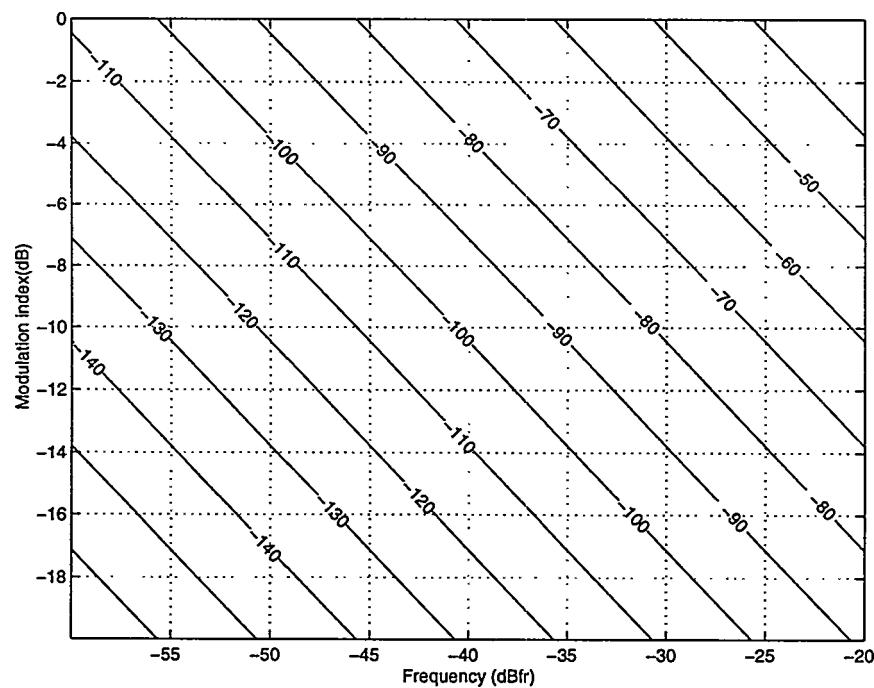

| 2.6.3 Balanced PSCPWM type 1 (BNS1/BND1) .....                    | 46 |

| 2.6.4 Spectral characteristics for Balanced PSCPWM – Type 1 ..... | 47 |

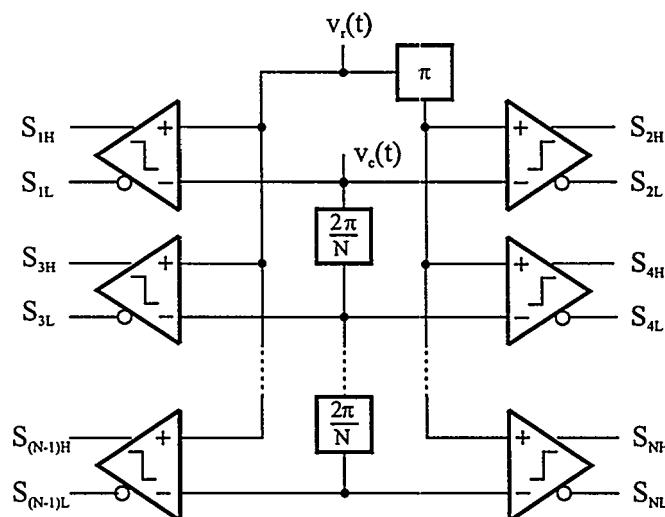

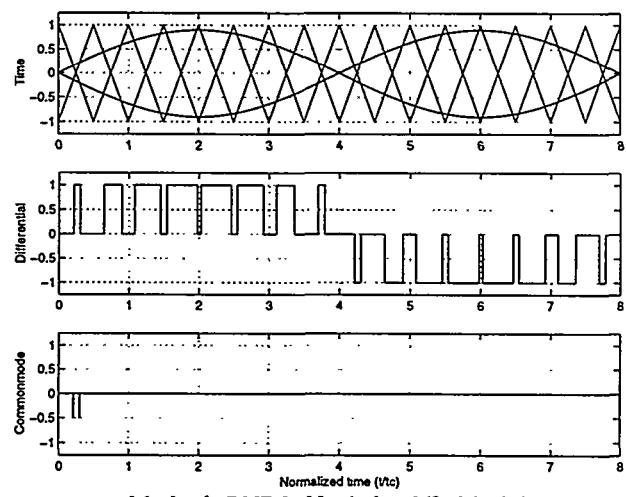

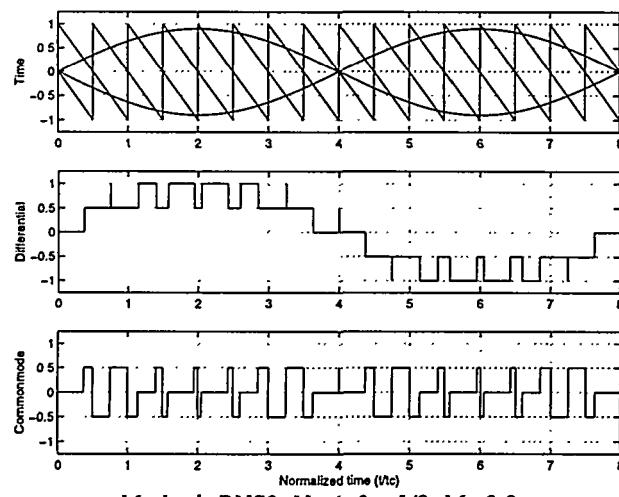

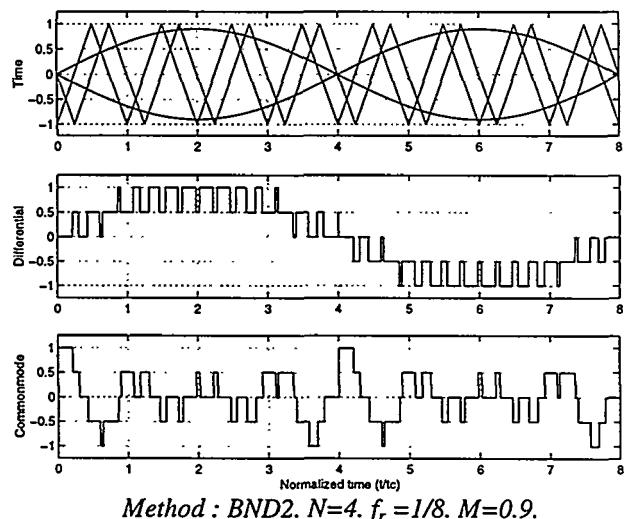

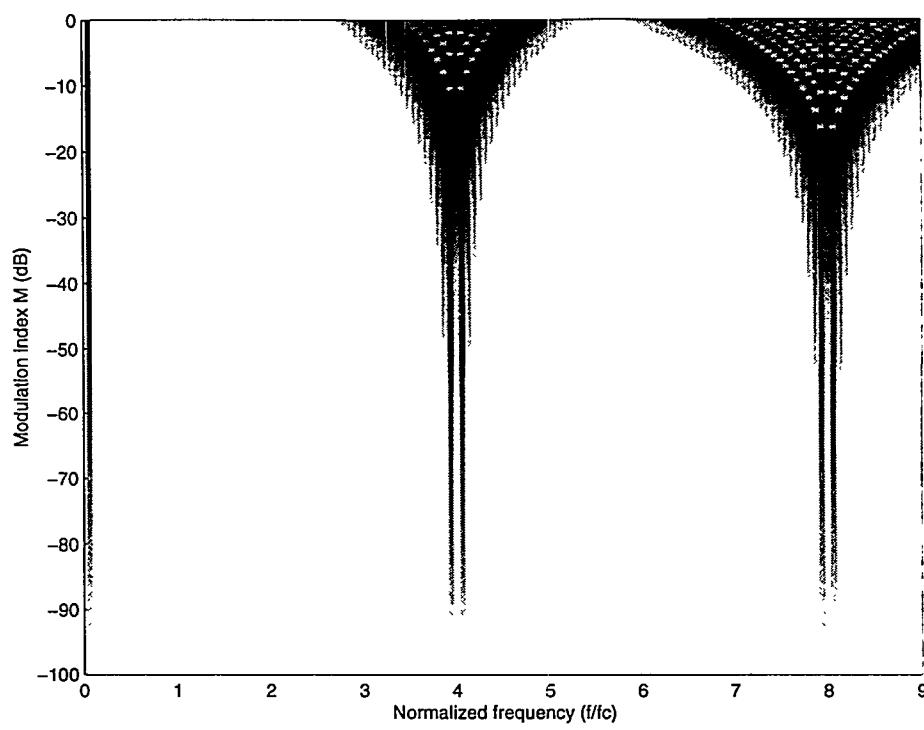

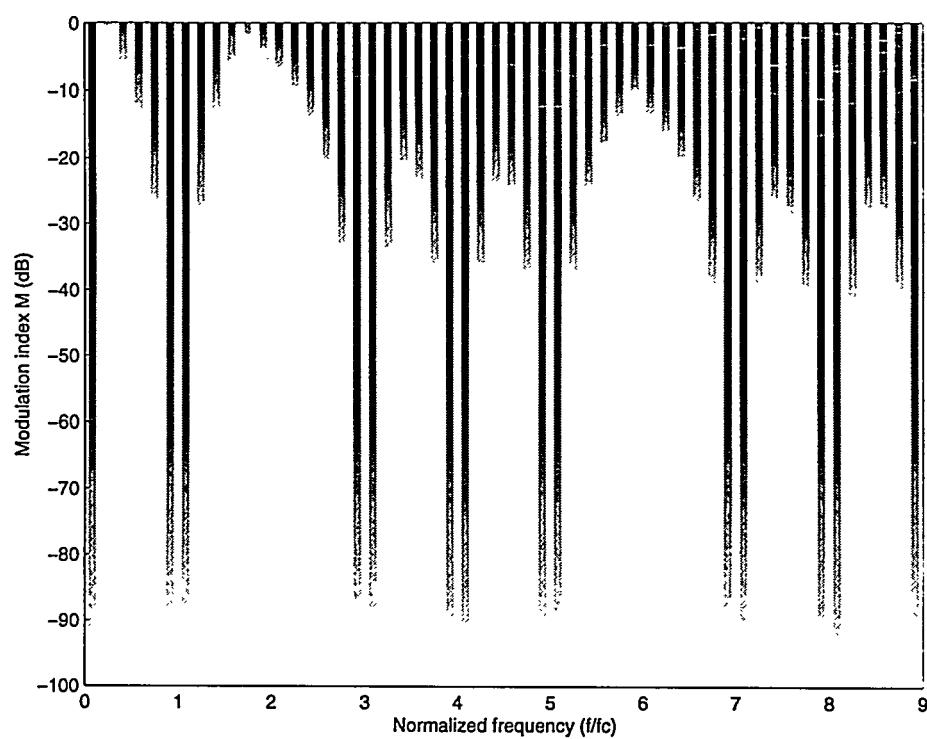

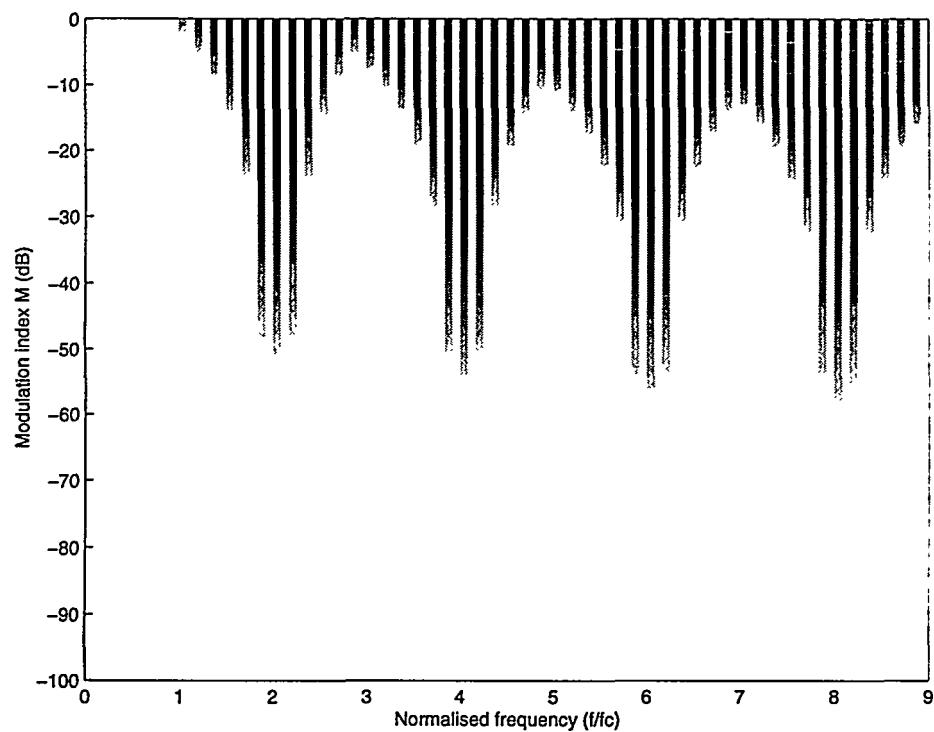

| 2.6.5 Balanced PSCPWM type 2 (BNS2/BND2) .....                    | 51 |

| 2.6.6 Spectral characteristics for Balanced PSCPWM – Type 2 ..... | 52 |

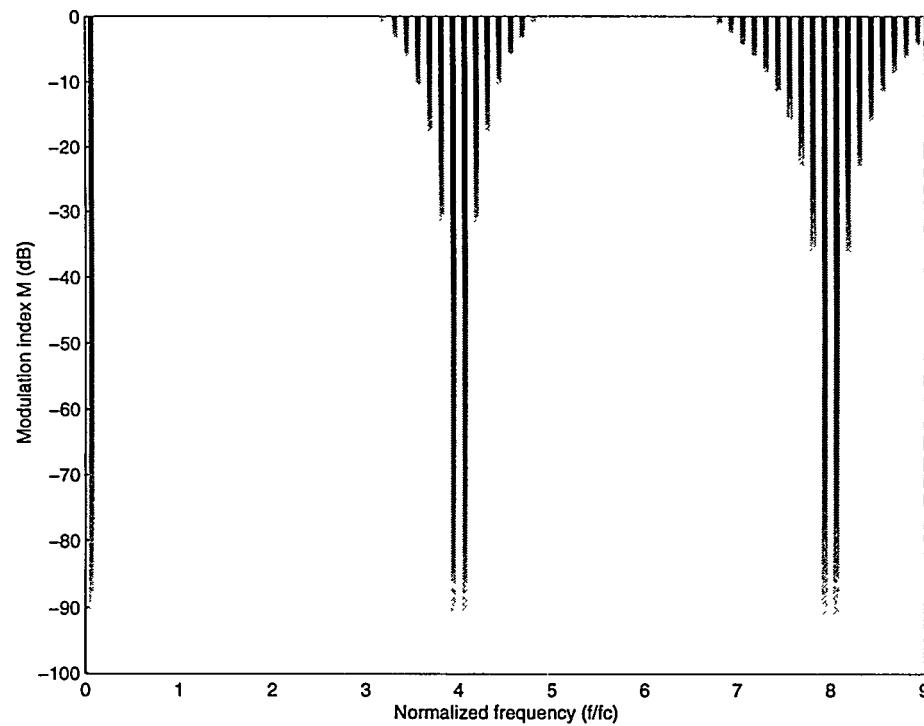

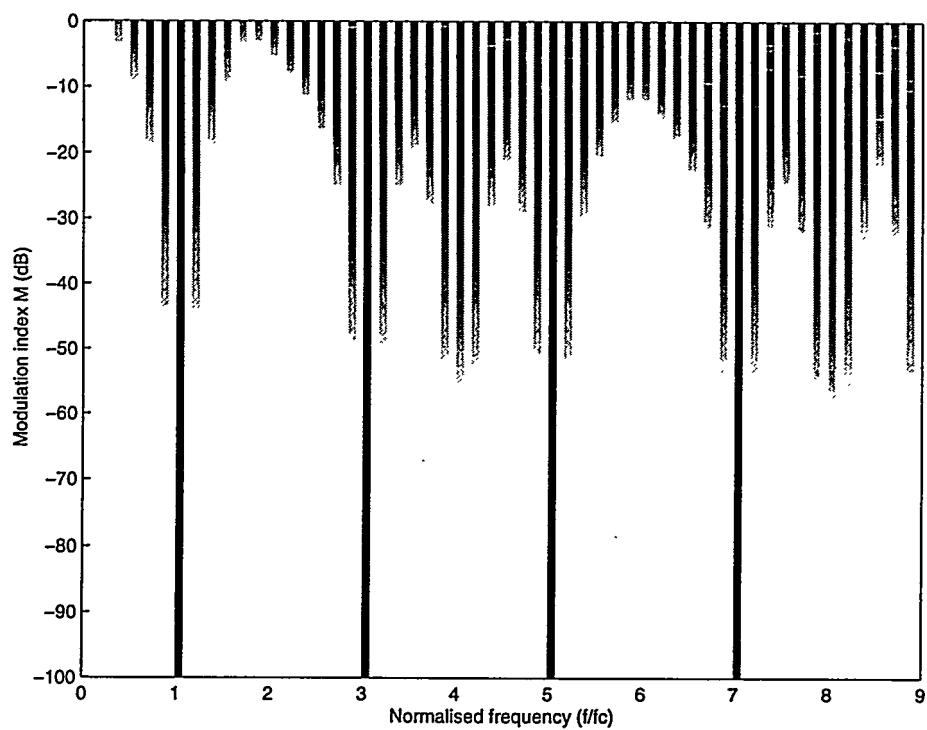

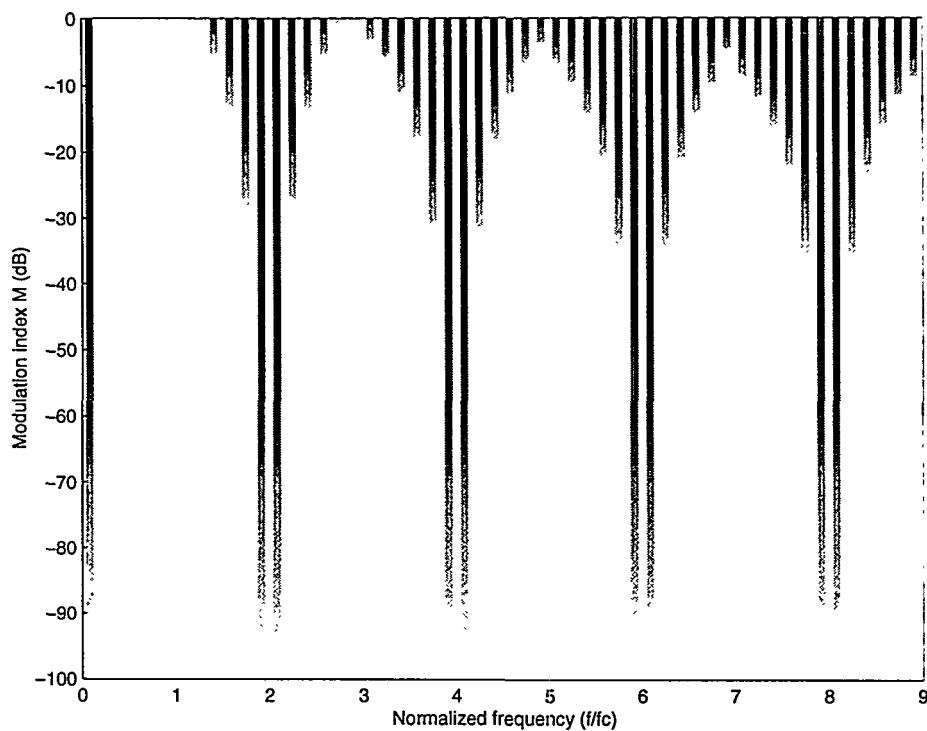

| 2.6.7 Balanced PSCPWM type 3 (BNS3/BND3) .....                    | 55 |

| 2.6.8 Spectral characteristics for Balanced PSCPWM – Type 3 ..... | 56 |

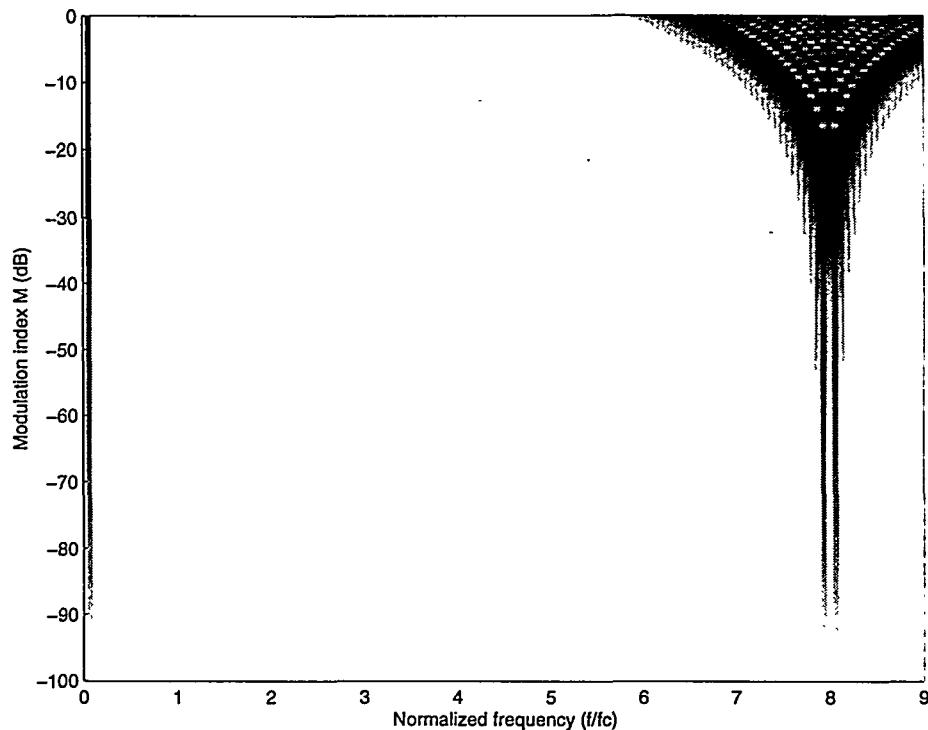

| 2.7 Selection of PSCPWM method .....                              | 59 |

| 2.8 Other Multilevel PWM methods .....                            | 60 |

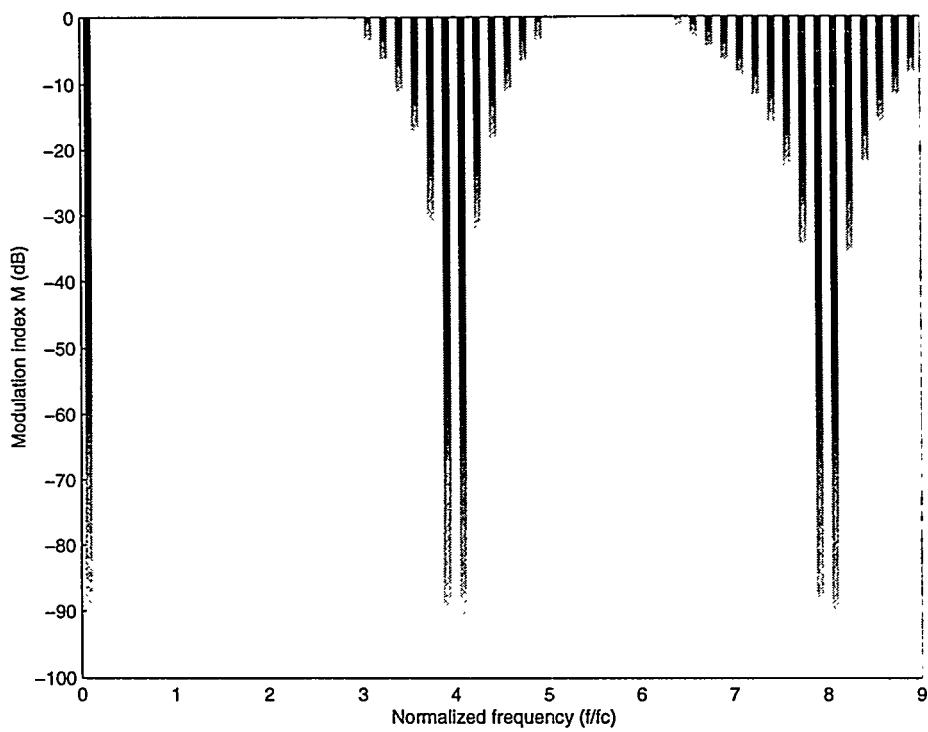

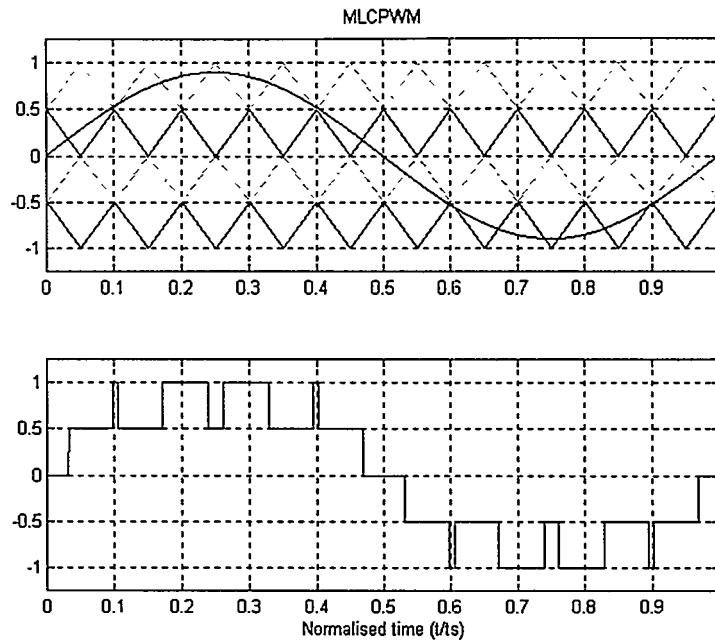

| 2.8.1 Multiple Leveled Carrier PWM (MLCPWM) .....                 | 60 |

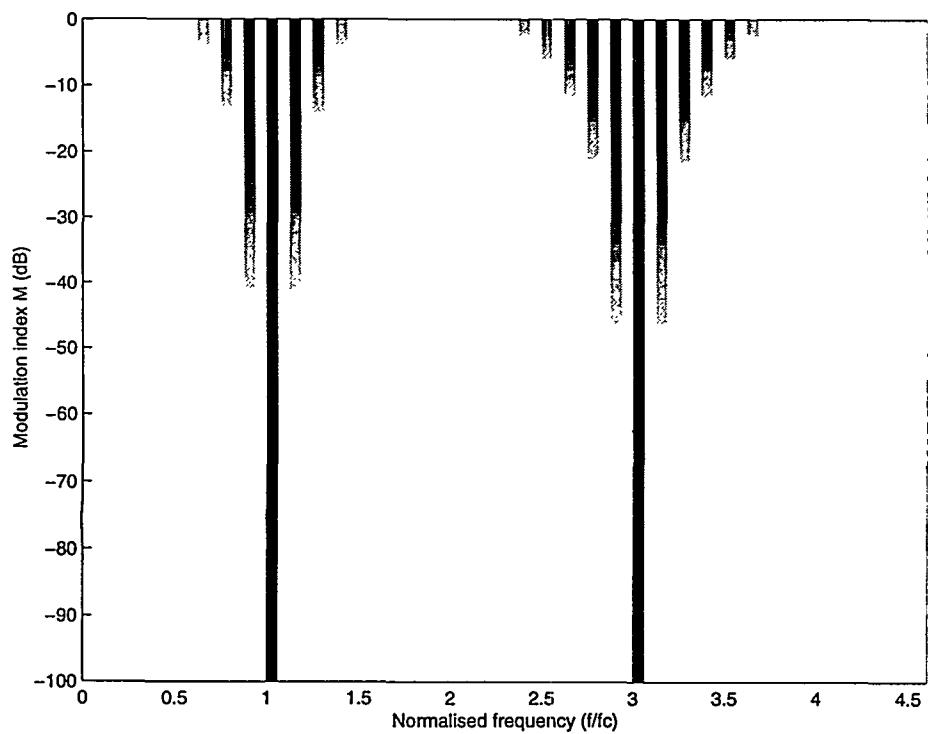

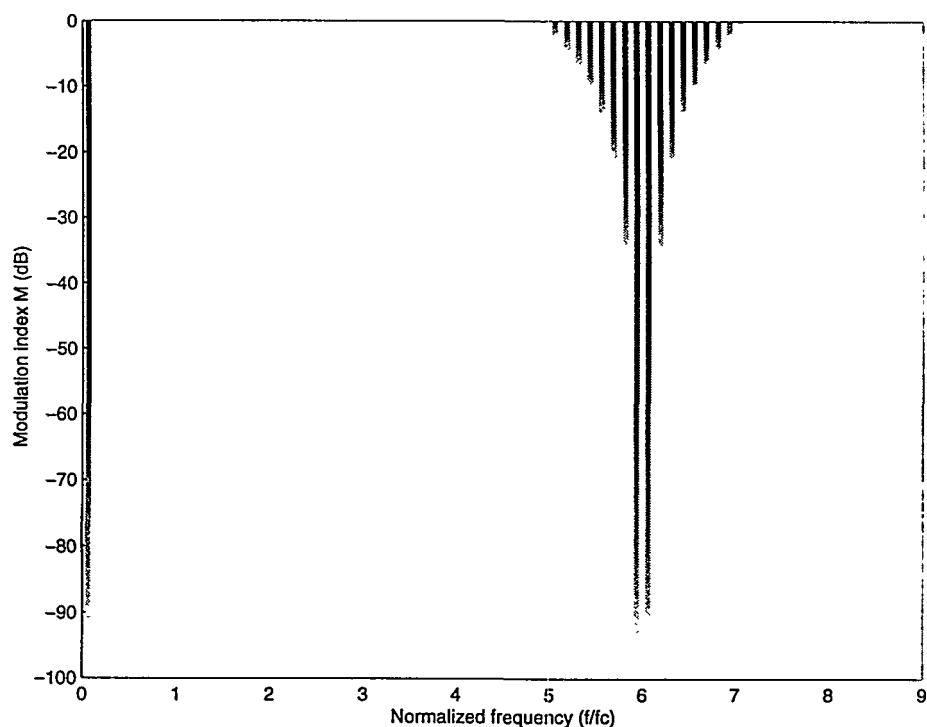

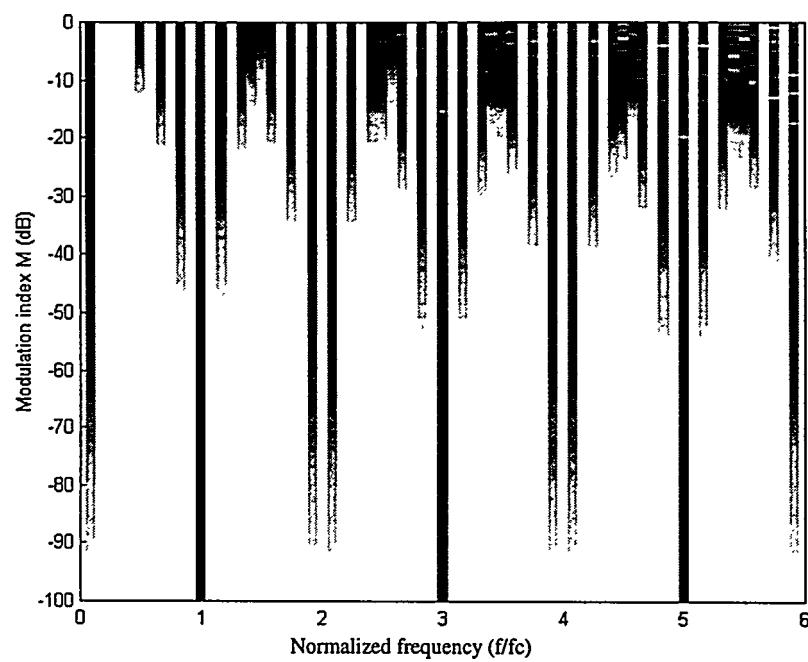

| 2.8.2 MLCPWM spectral characteristics .....                       | 62 |

| 2.9 Summary .....                                                 | 64 |

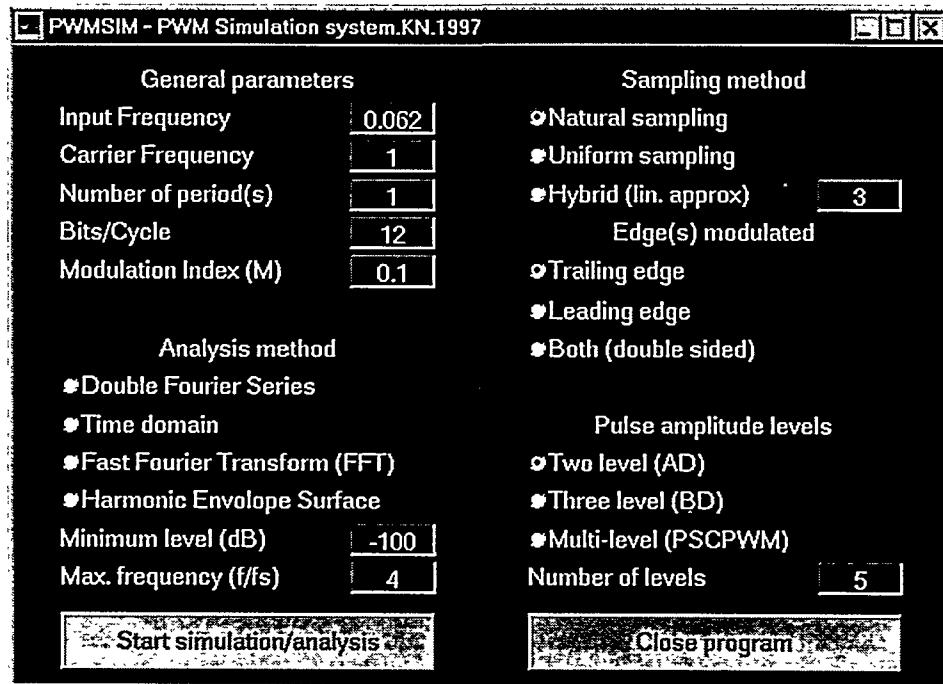

| 2.9.1 PWMSIM – GUI based toolbox for MATLAB .....                 | 65 |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| <b>Chapter 3 – Digital Pulse Modulation.....</b>                           | 67  |

| 3.1 The digital PMA paradox.....                                           | 67  |

| 3.2 Digital Pulse modulation methods .....                                 | 68  |

| 3.2.1 Digital PDM.....                                                     | 68  |

| 3.2.2 Digital PWM.....                                                     | 69  |

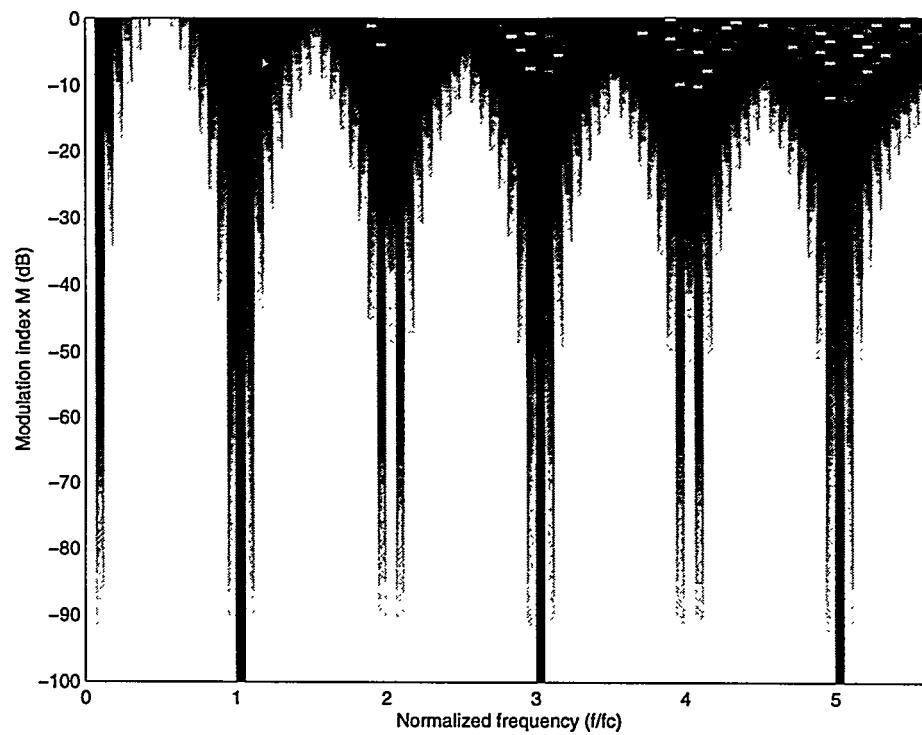

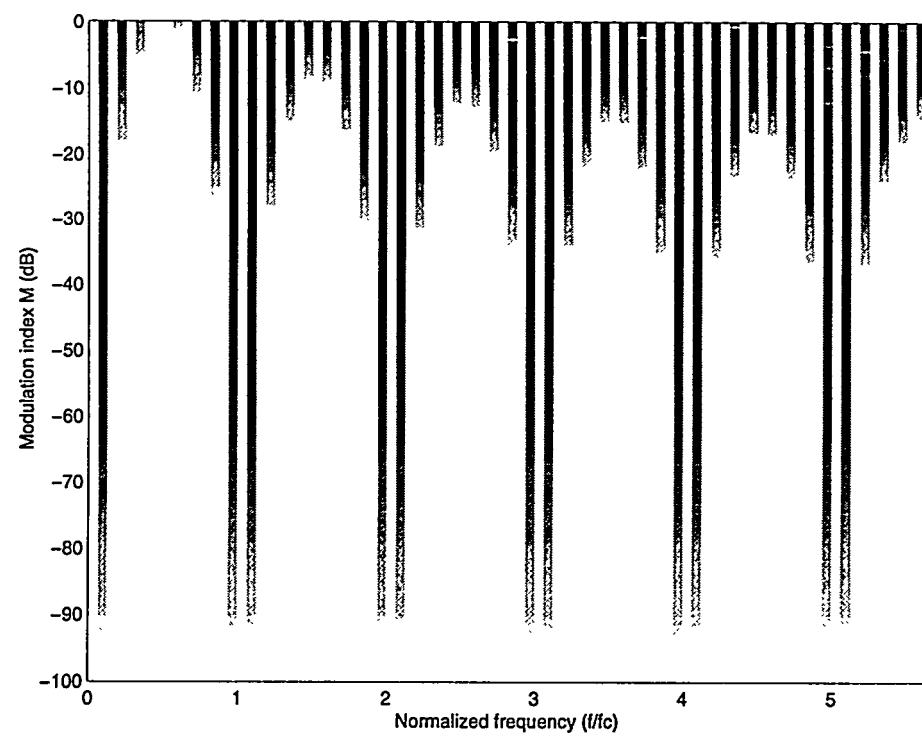

| 3.3 UPWM analysis .....                                                    | 70  |

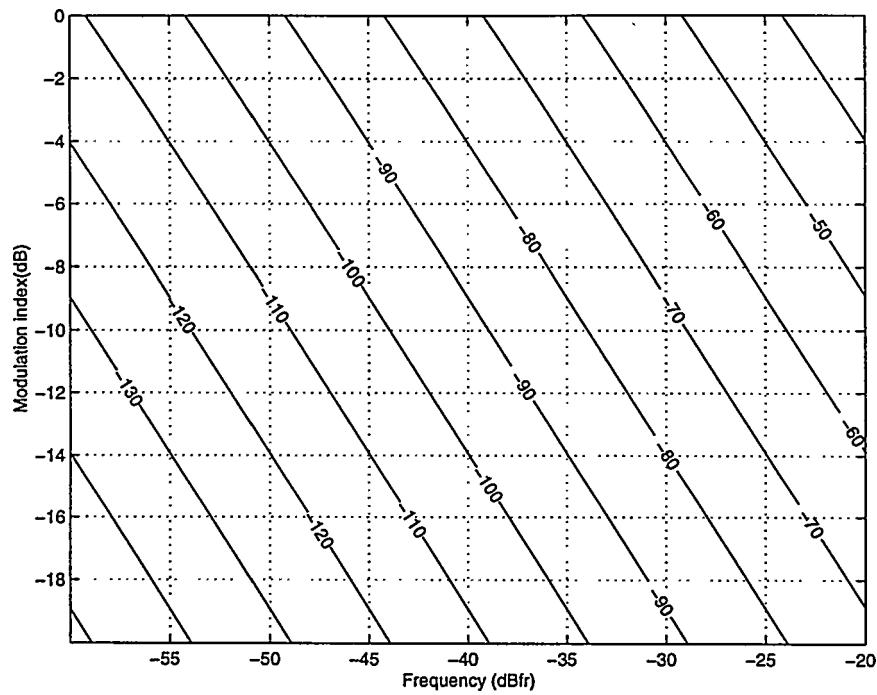

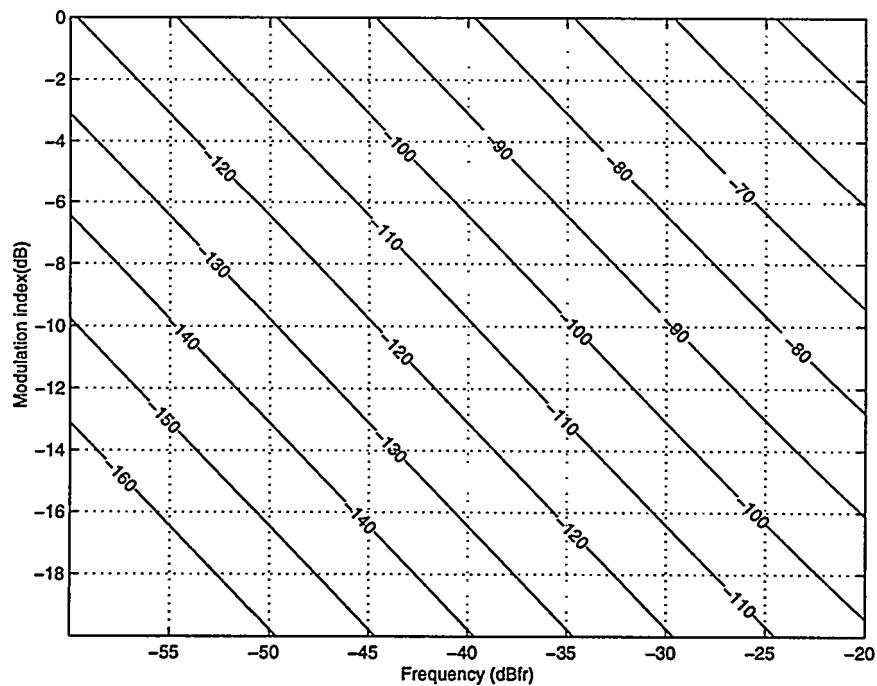

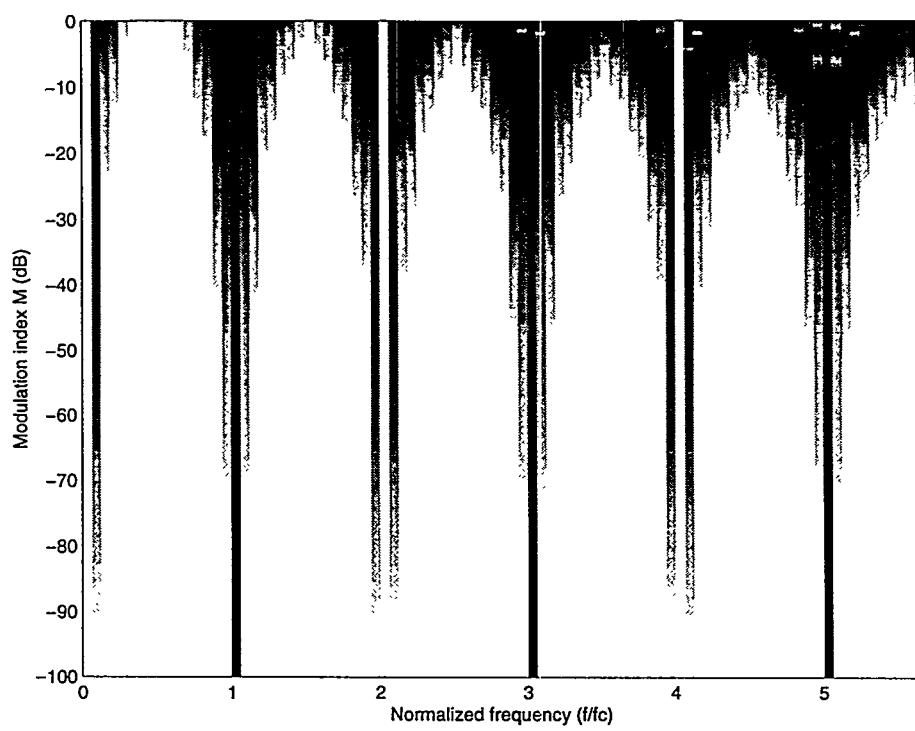

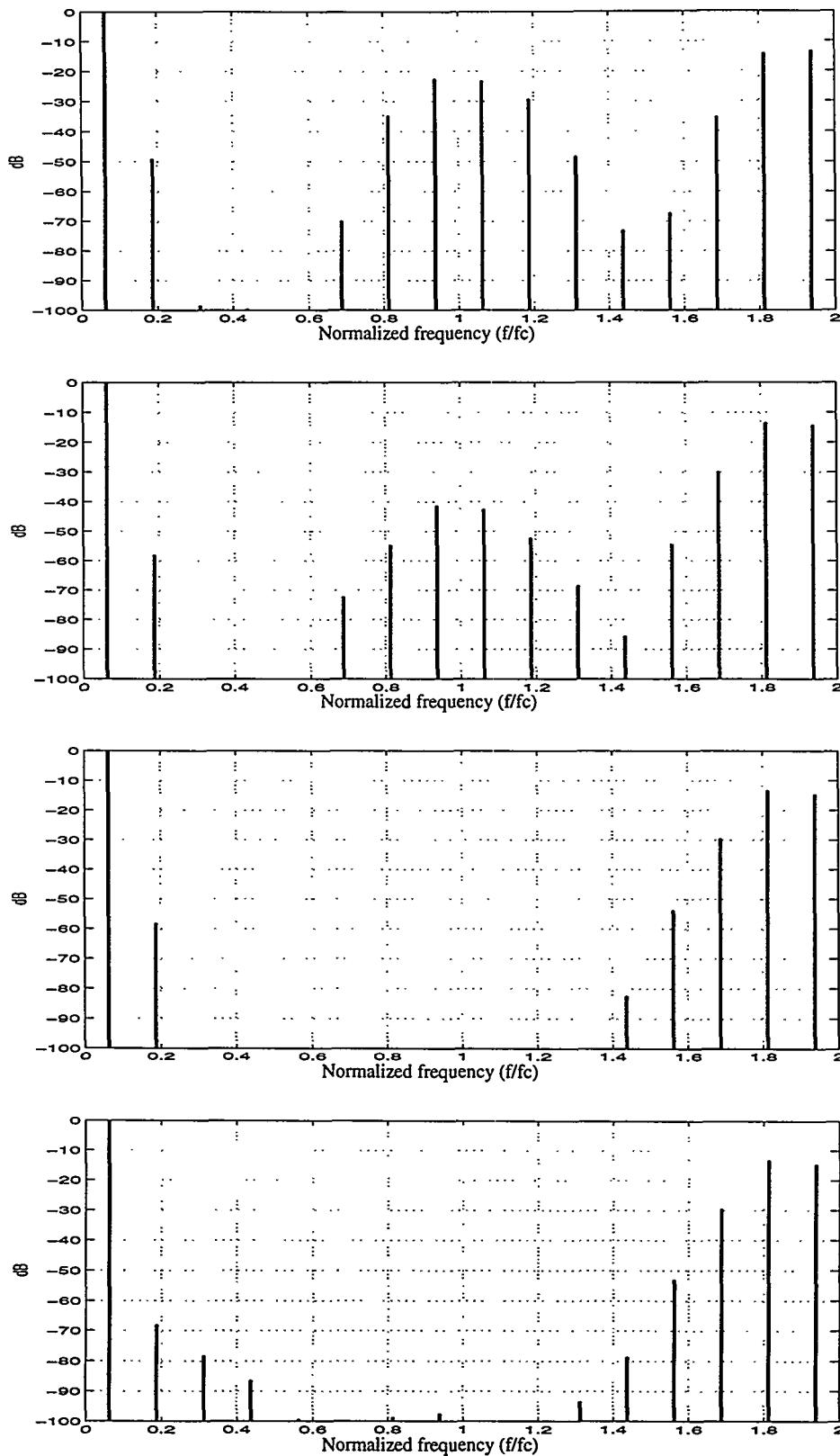

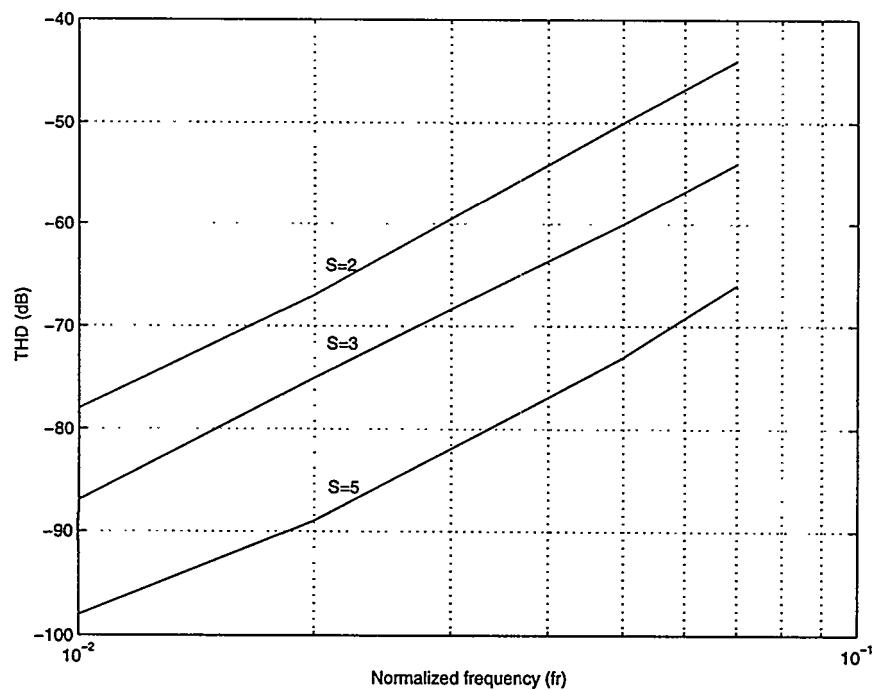

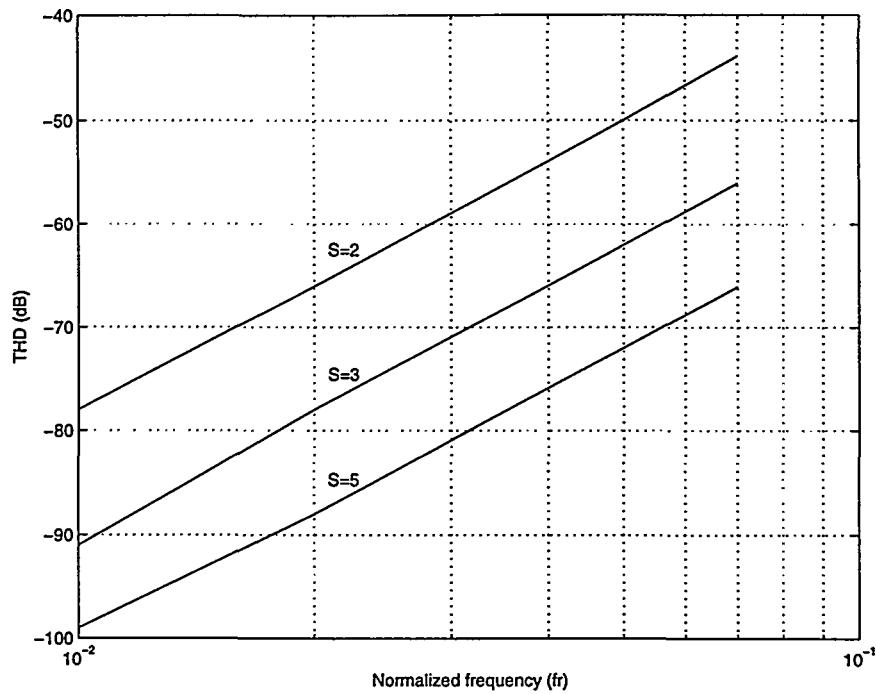

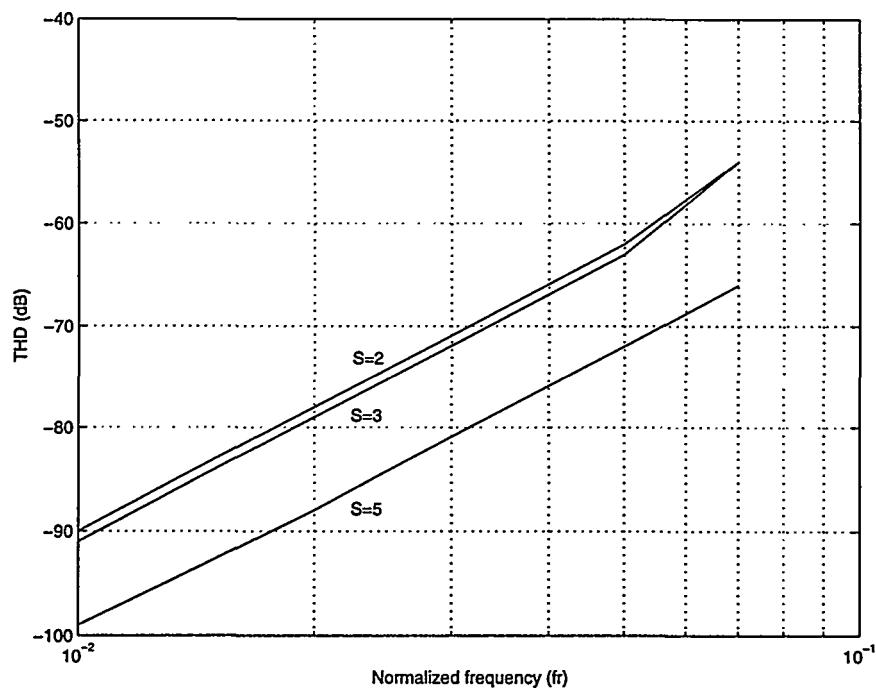

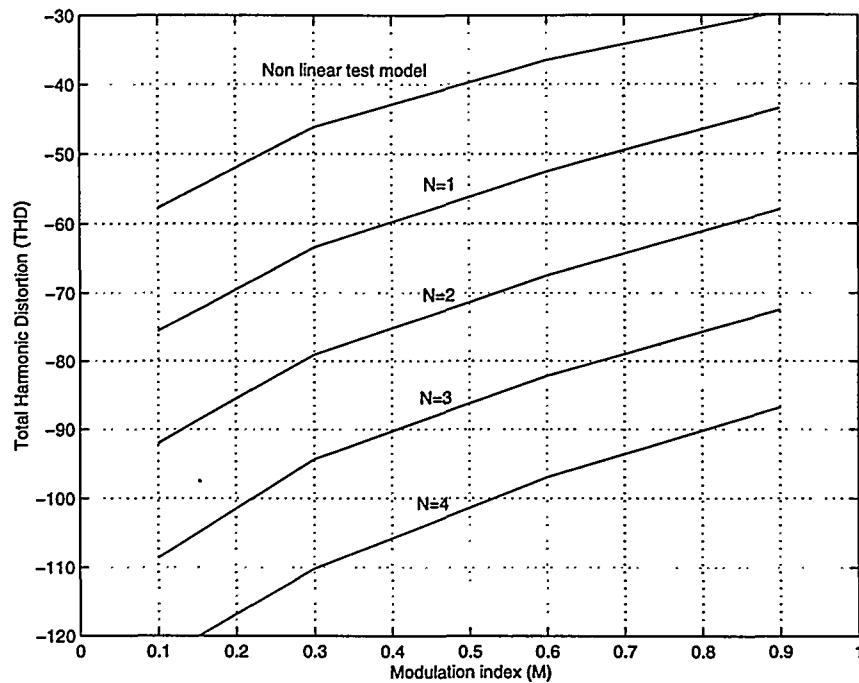

| 3.3.1 UPWM harmonic distortion.....                                        | 73  |

| 3.3.2 UPWM HF characteristics .....                                        | 76  |

| 3.3.3 Uniformly sampled PSCPWM.....                                        | 76  |

| 3.4 Enhanced digital PWM methods .....                                     | 79  |

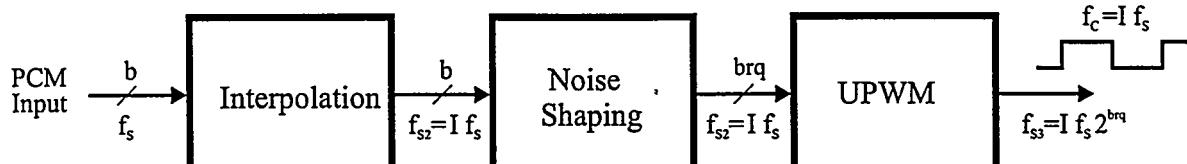

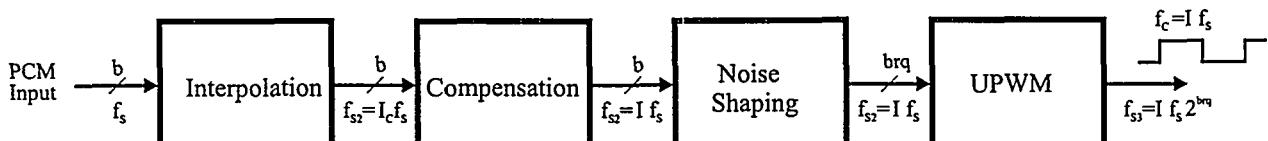

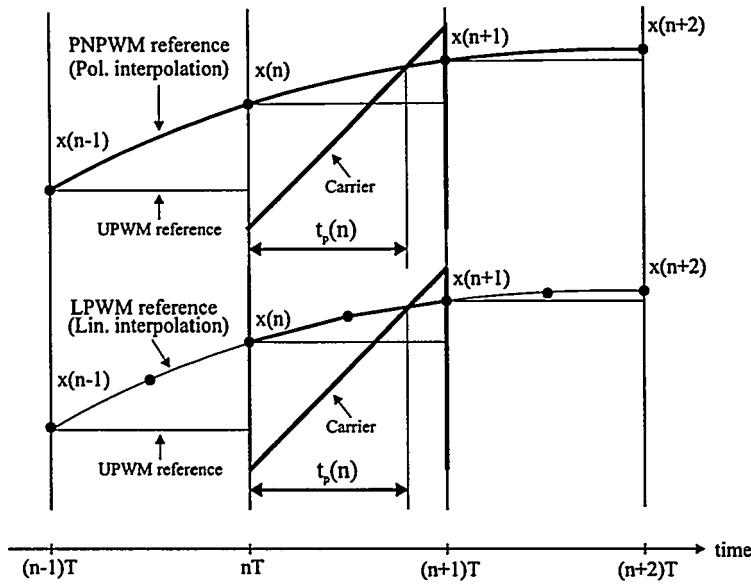

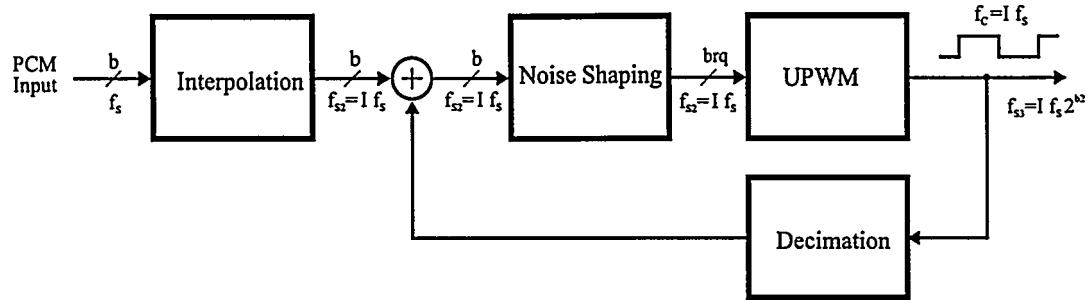

| 3.4.1 Interpolation and noise shaping (INS) topology.....                  | 79  |

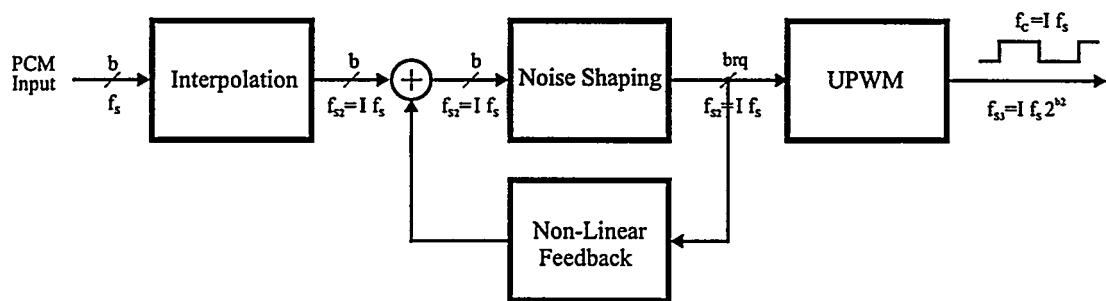

| 3.4.2 Improving modulator linearity .....                                  | 79  |

| 3.4.3 Precompensation methods .....                                        | 80  |

| 3.4.4 Direct compensation methods.....                                     | 82  |

| 3.4.5 Feedback linearization .....                                         | 83  |

| 3.4.6 Method selection.....                                                | 83  |

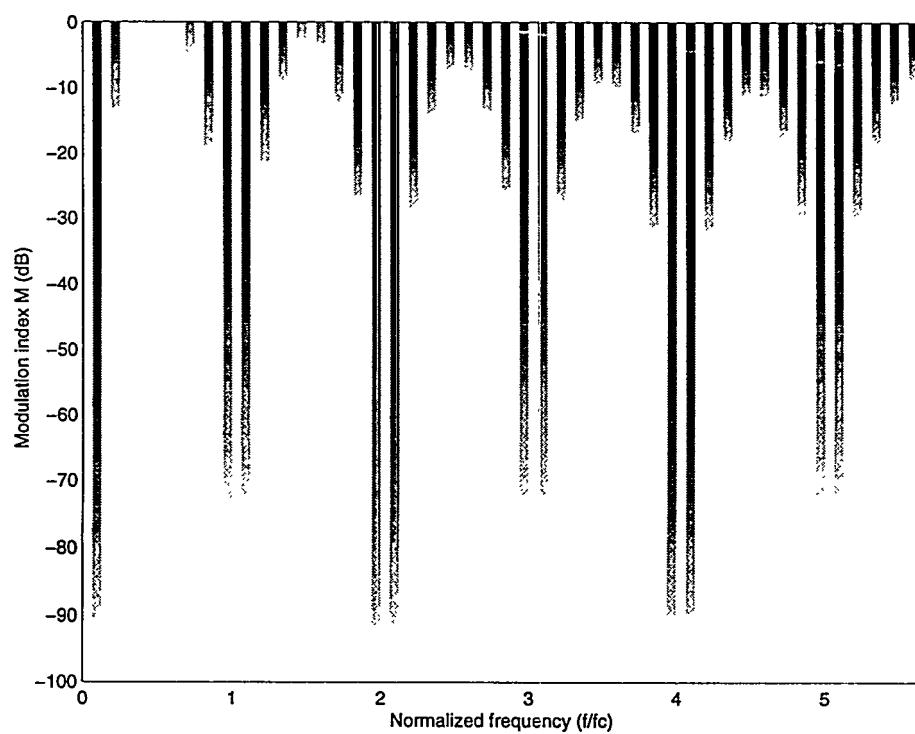

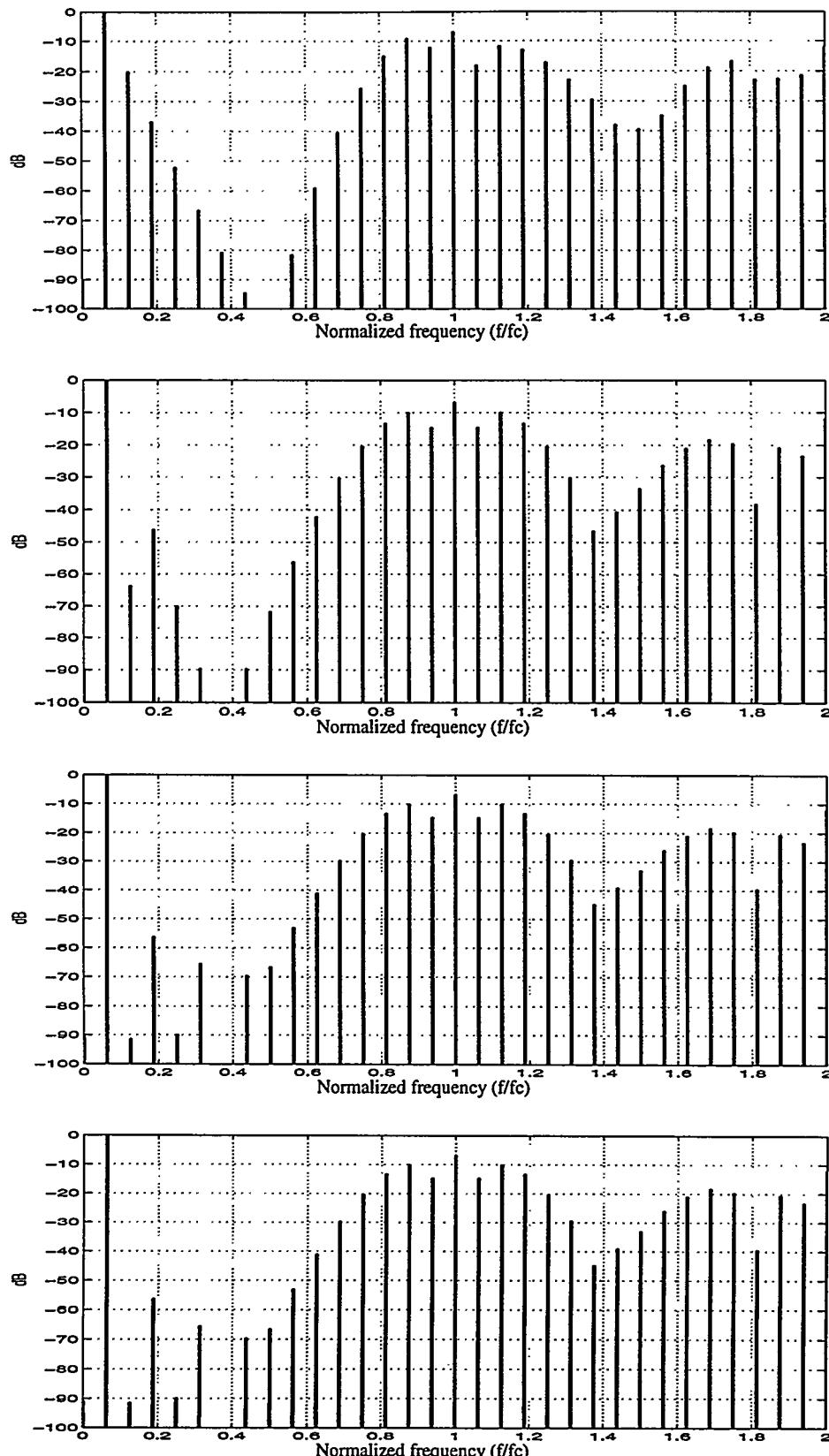

| 3.5 LPWM spectral analysis .....                                           | 84  |

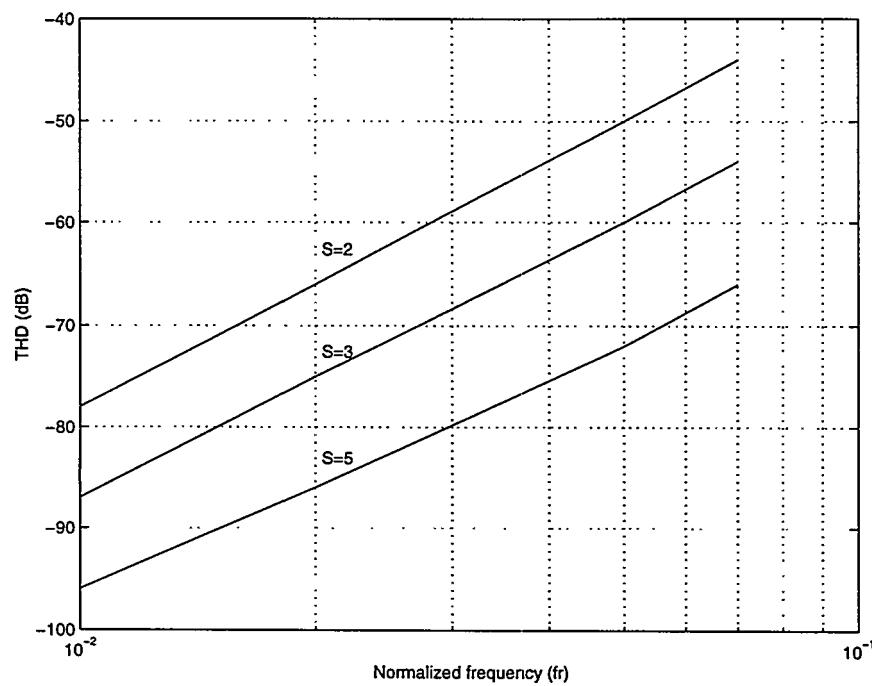

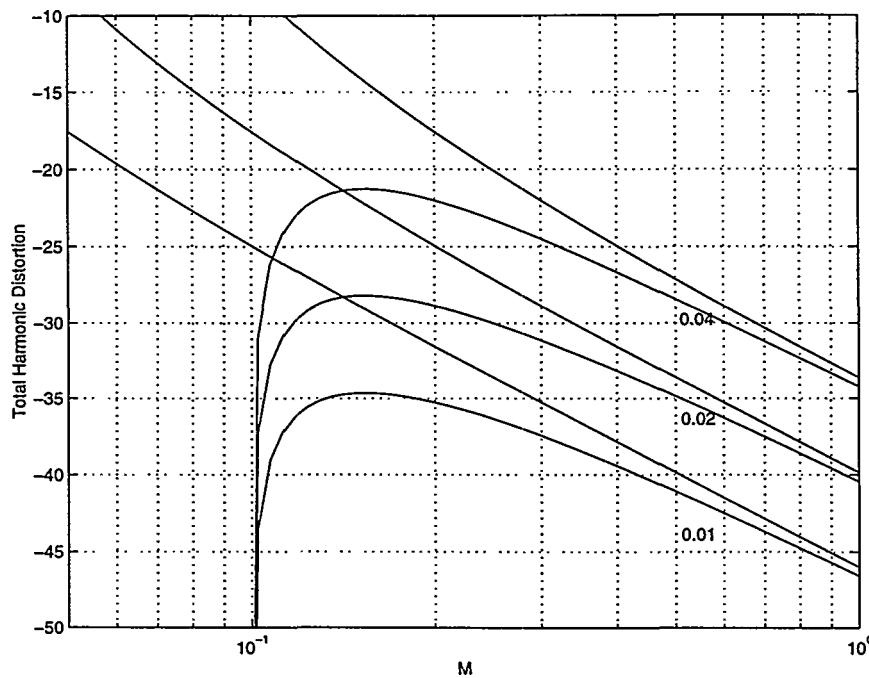

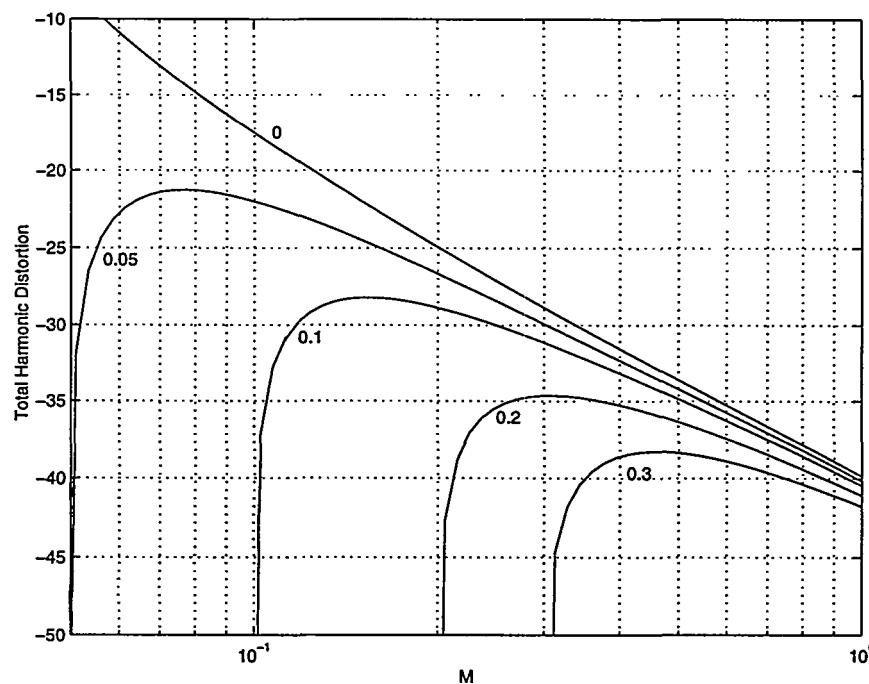

| 3.5.1 LPWM distortion .....                                                | 89  |

| 3.6 LPWM modulator synthesis .....                                         | 92  |

| 3.6.1 Interpolation .....                                                  | 92  |

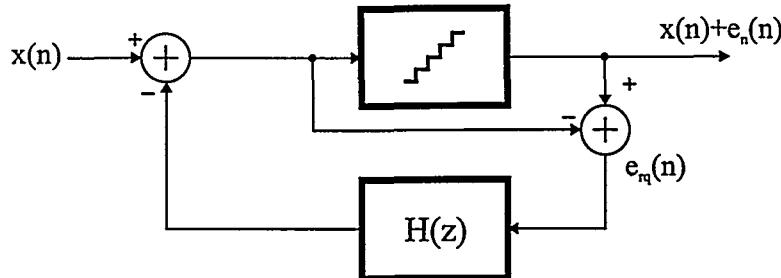

| 3.7 Noise shaping.....                                                     | 93  |

| 3.7.1 Analysis.....                                                        | 93  |

| 3.7.2 Linear modeling .....                                                | 94  |

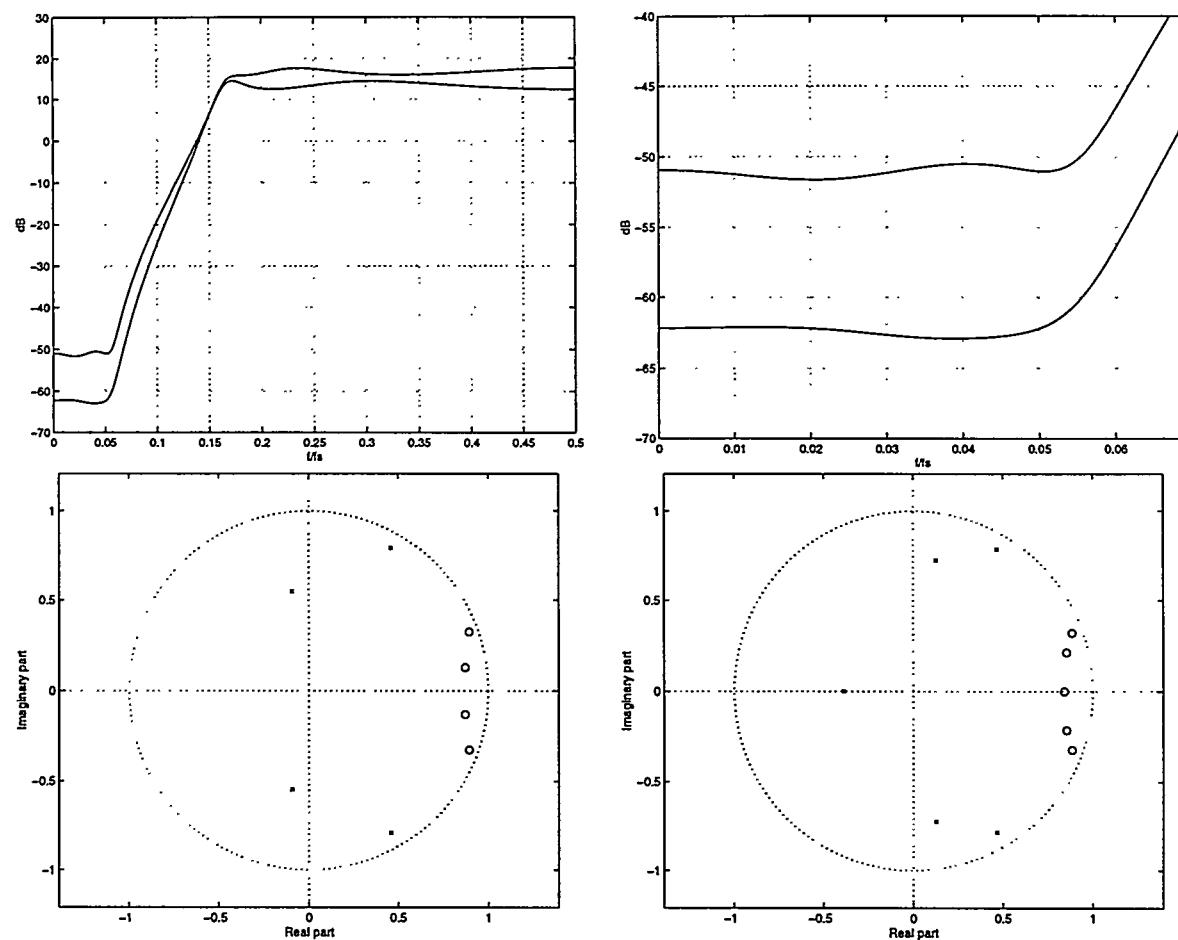

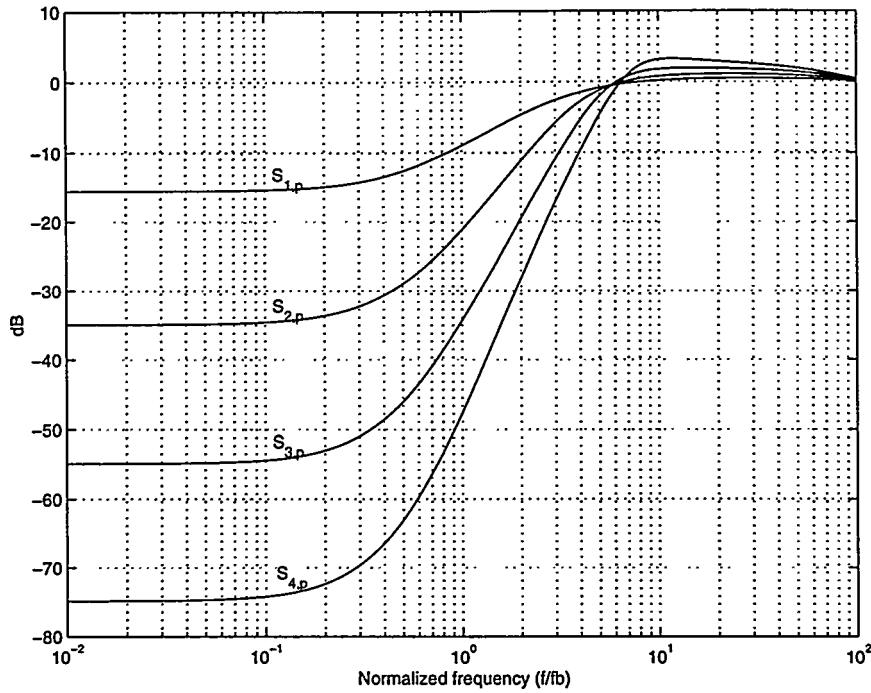

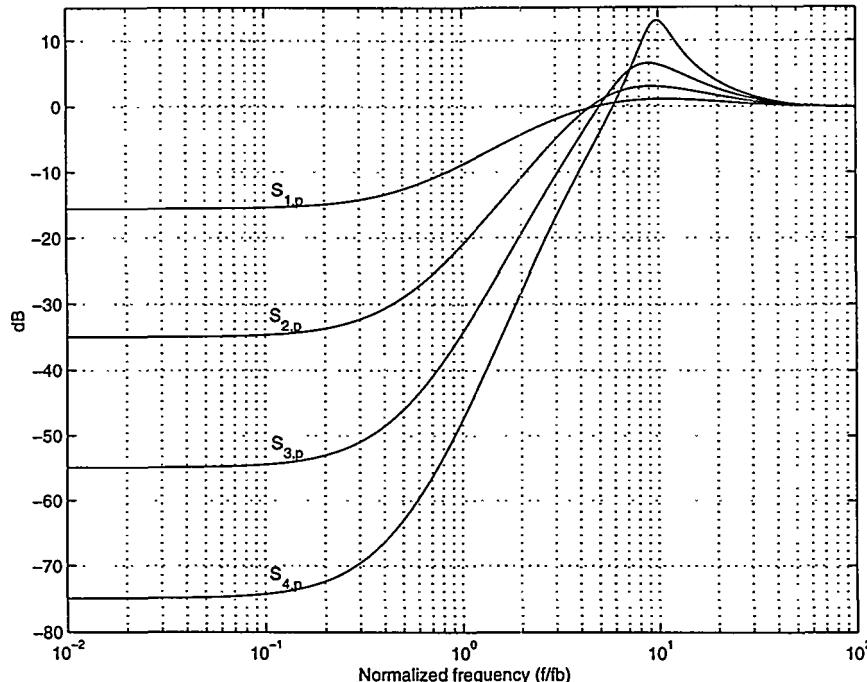

| 3.7.3 Noise Transfer function (NTF) filter synthesis for digital LPWM..... | 95  |

| 3.7.4 NTF(z) signal band requirements .....                                | 97  |

| 3.7.5 Realizing the modified NTF(z) prototype.....                         | 98  |

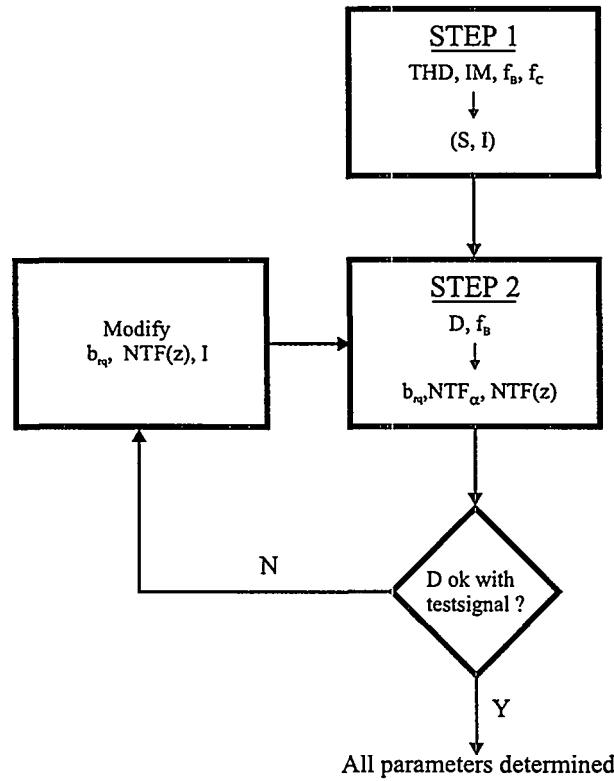

| 3.8 LPWM modulator design methodology.....                                 | 102 |

| 3.8.1 Modulator synthesis example .....                                    | 103 |

| 3.9 Summary .....                                                          | 106 |

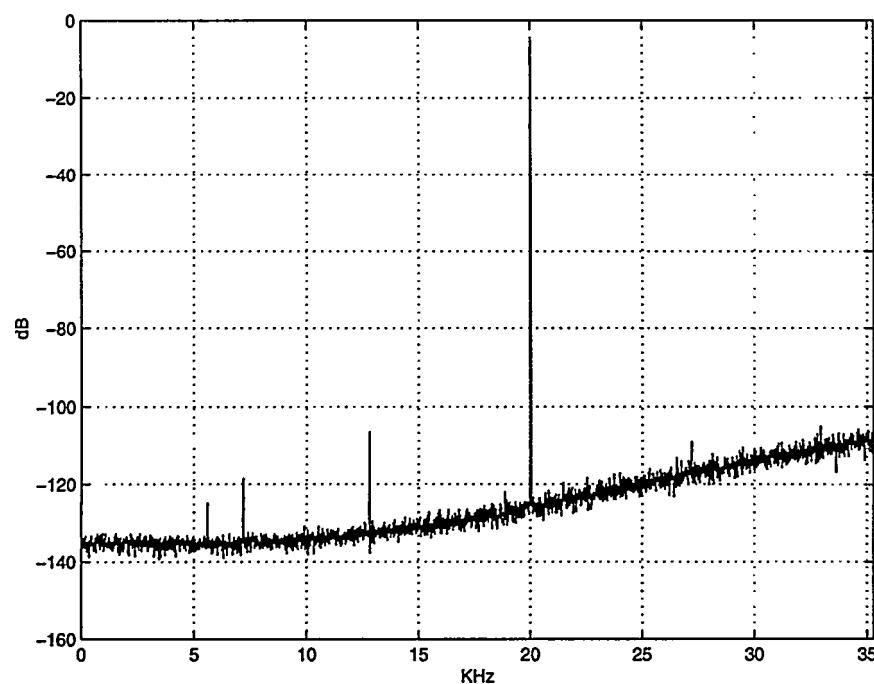

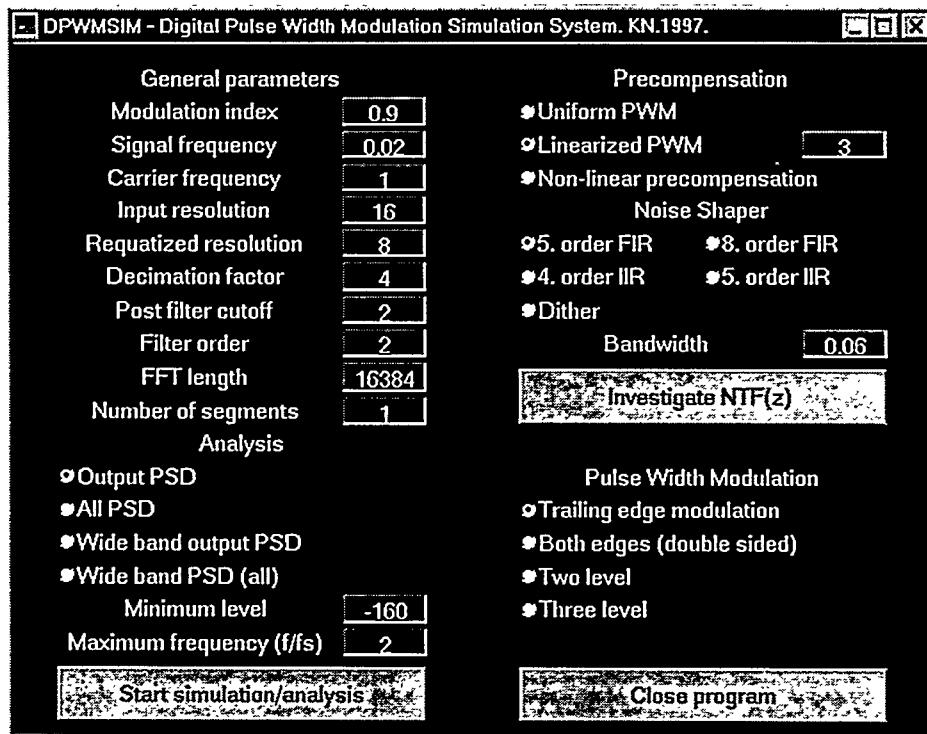

| 3.9.1 DPWMSIM–A Digital Modulator design toolbox for MATLAB .....          | 107 |

| <b>Chapter 4 - Error Sources .....</b>                                     | 109 |

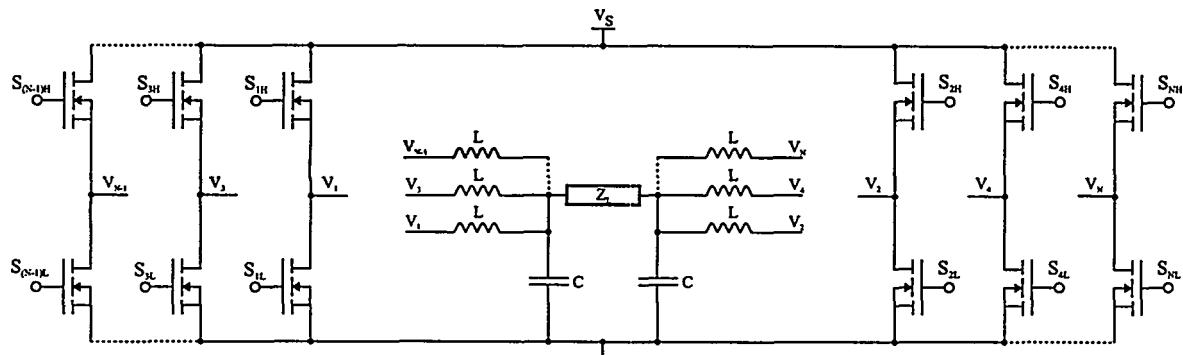

| 4.1 Power conversion.....                                                  | 110 |

| 4.2 Switching devices .....                                                | 111 |

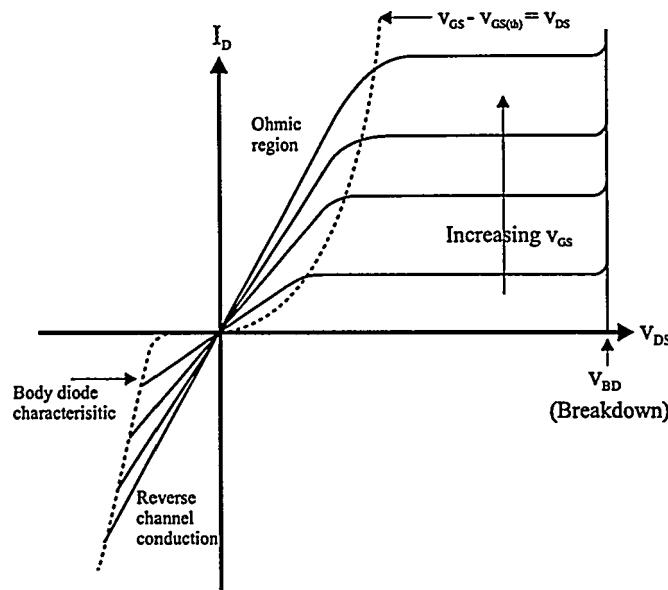

| 4.2.1 The vertical $n^+pn^-n^+$ Power MOSFET architecture.....             | 111 |

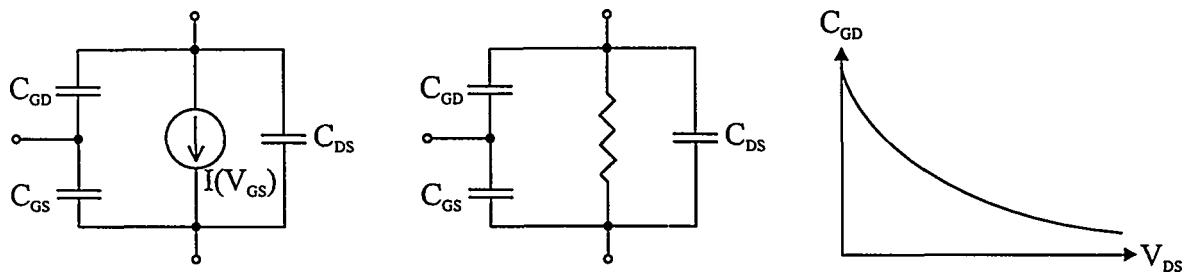

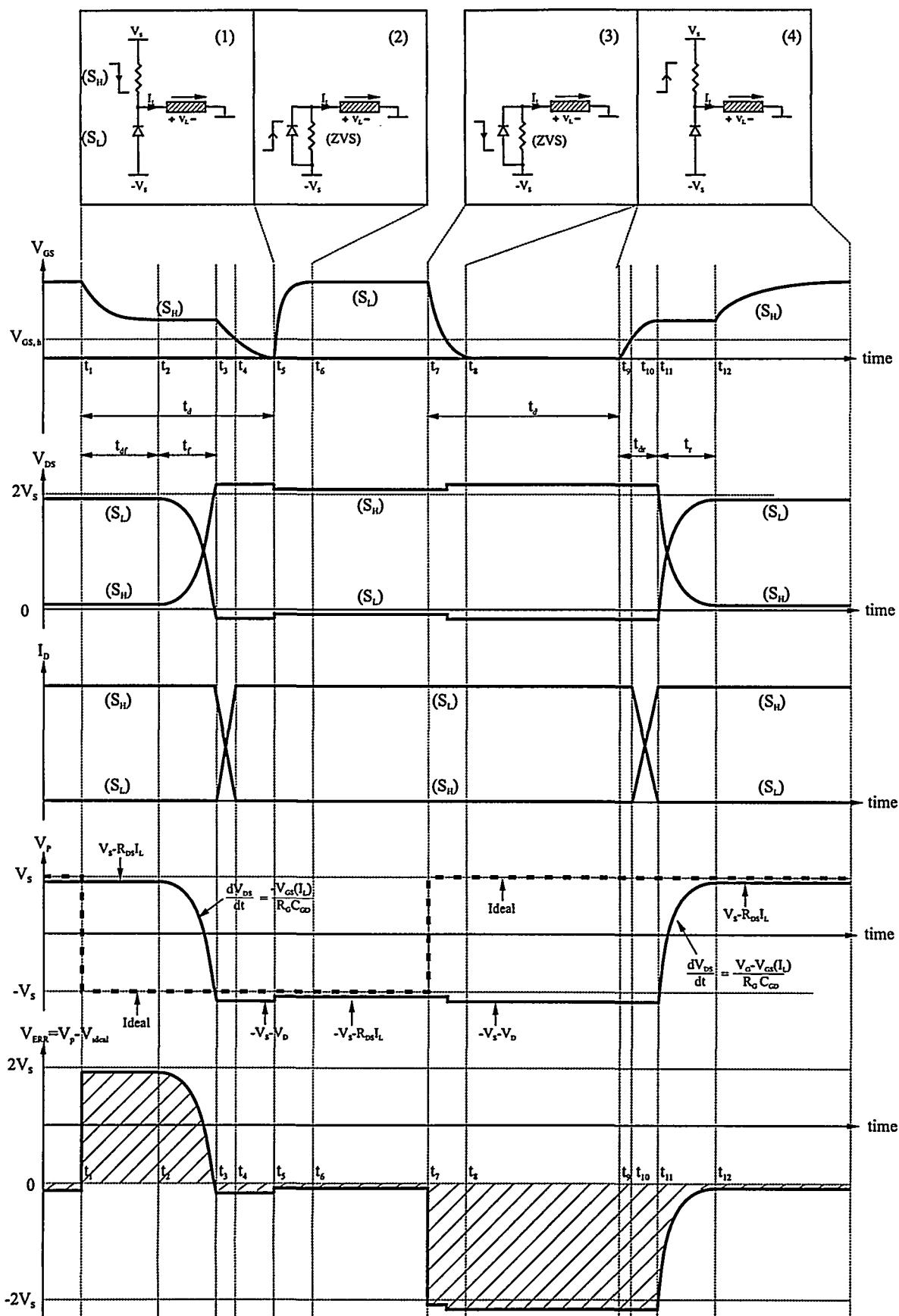

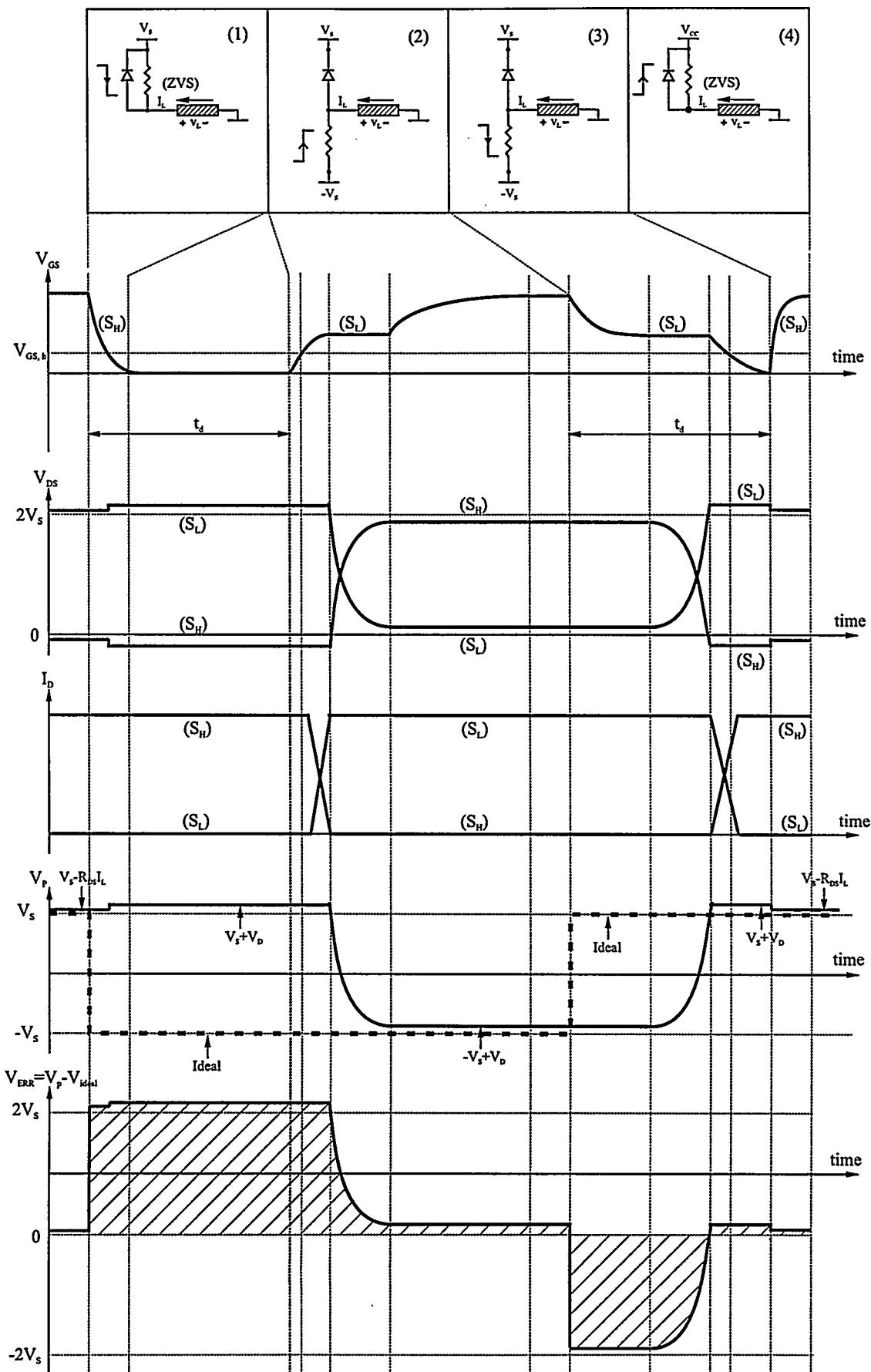

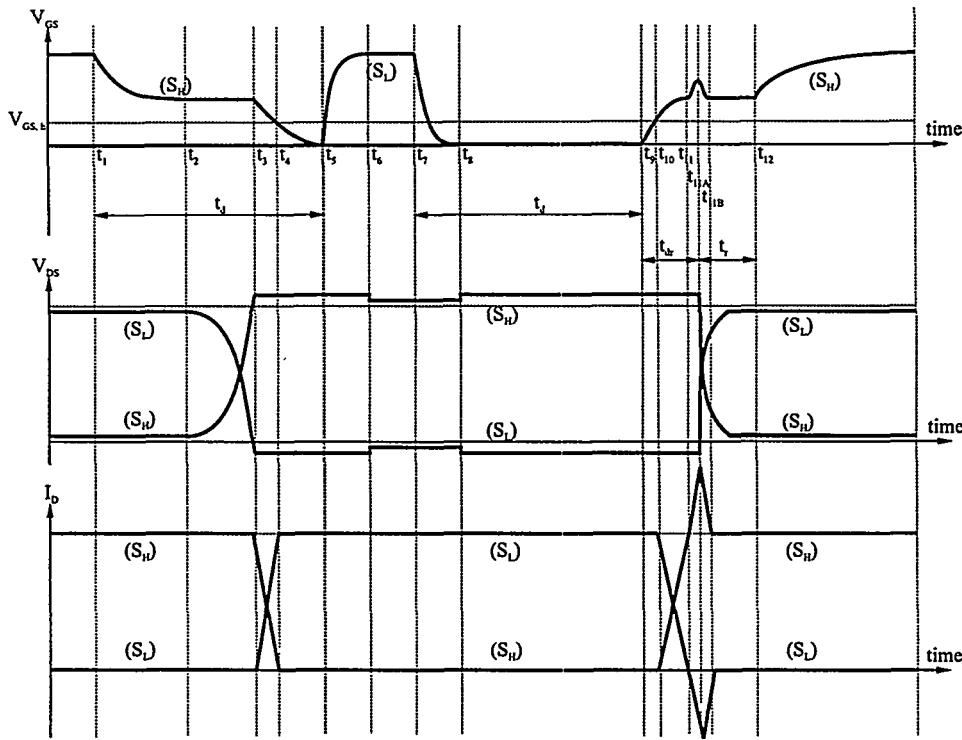

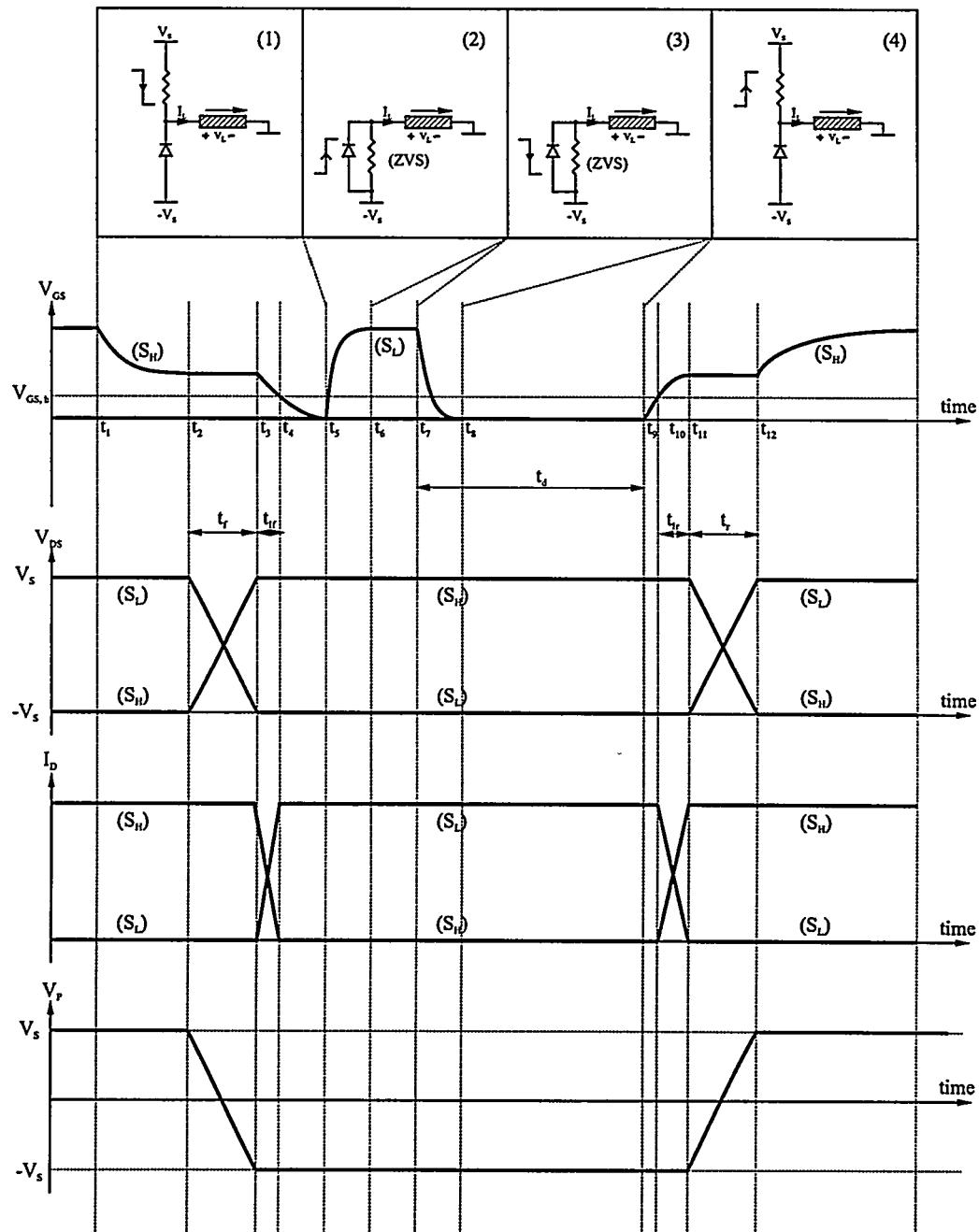

| 4.3 Switching leg characteristics.....                                     | 113 |

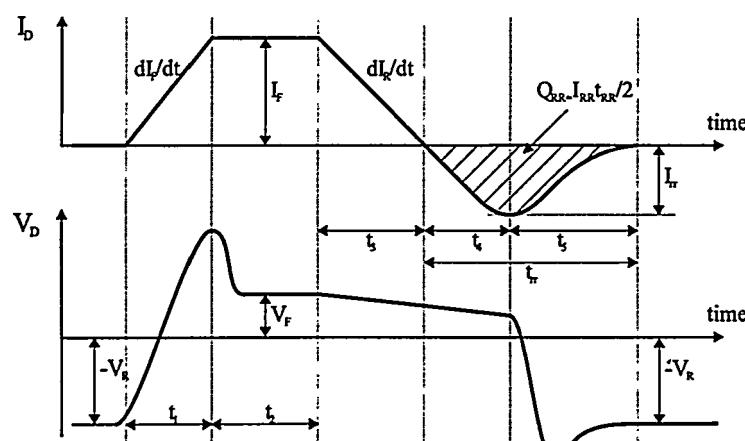

| 4.3.1 Reverse recovery effects .....                                       | 118 |

| 4.4 Categorization of error sources .....                                  | 118 |

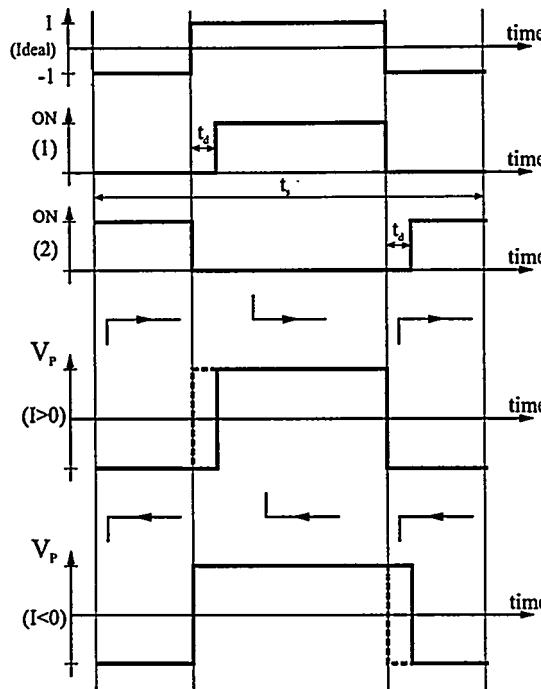

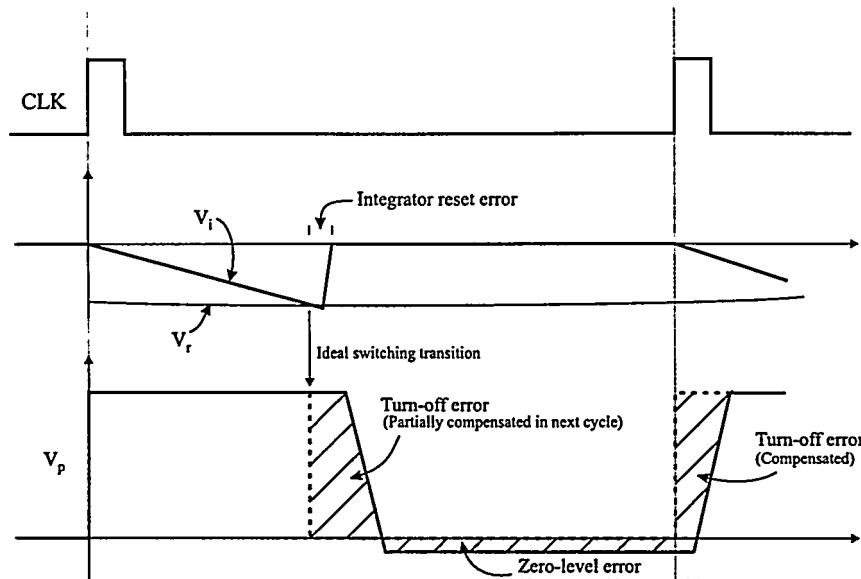

| 4.5 Pulse Timing Errors (PTE) analysis .....                               | 119 |

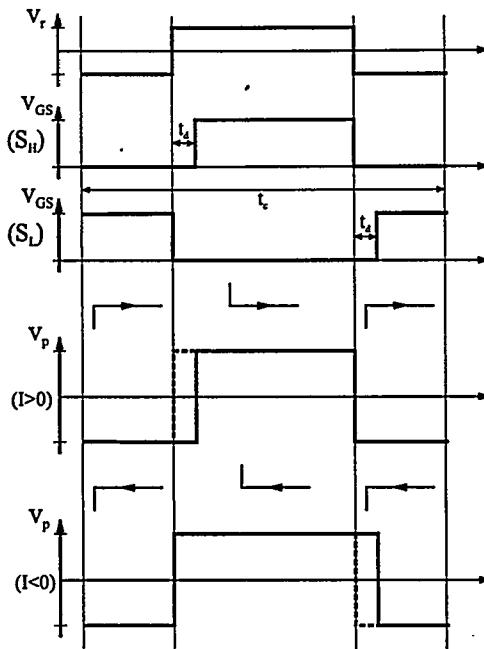

| 4.5.1 Blanking effects .....                                               | 119 |

| 4.5.2 Other PAE error sources .....                                        | 123 |

| 4.6 Pulse Amplitude Error (PAE) analysis .....                             | 126 |

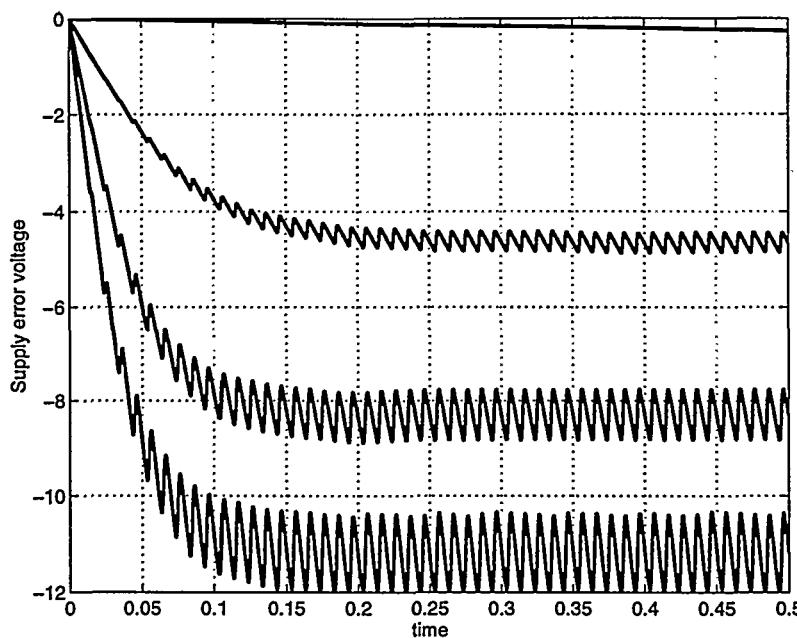

| 4.6.1 Power supply perturbations.....                                      | 126 |

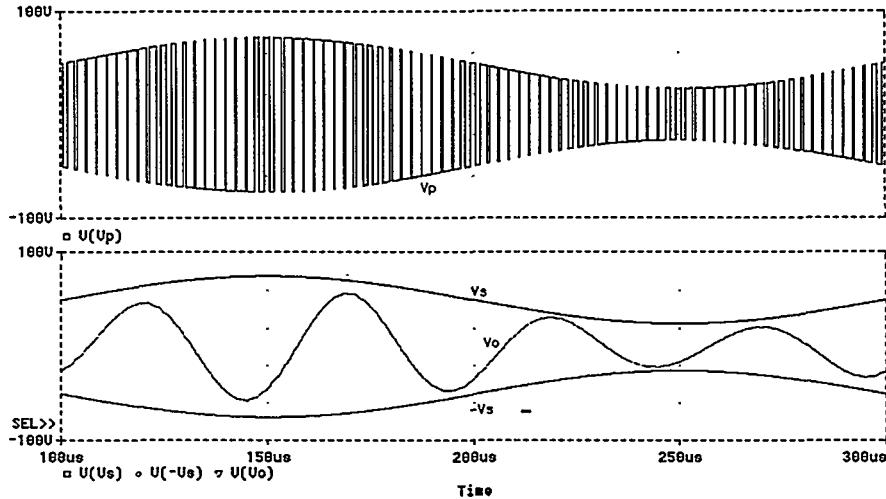

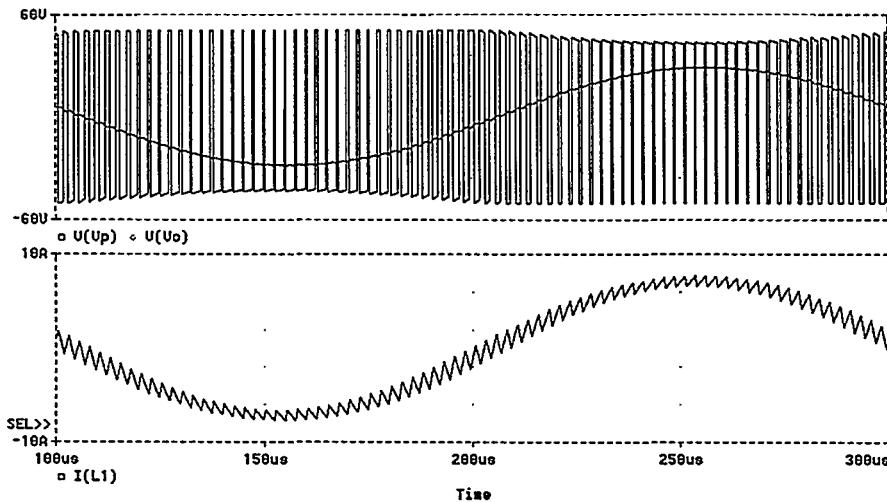

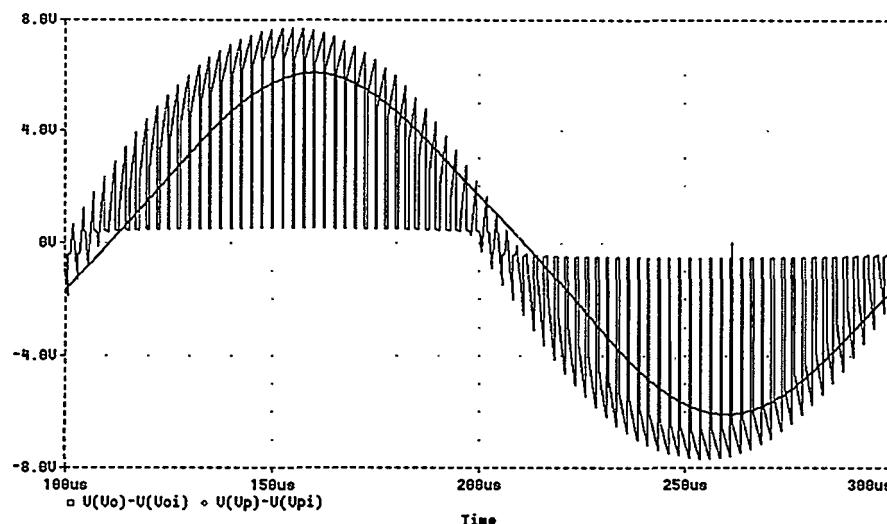

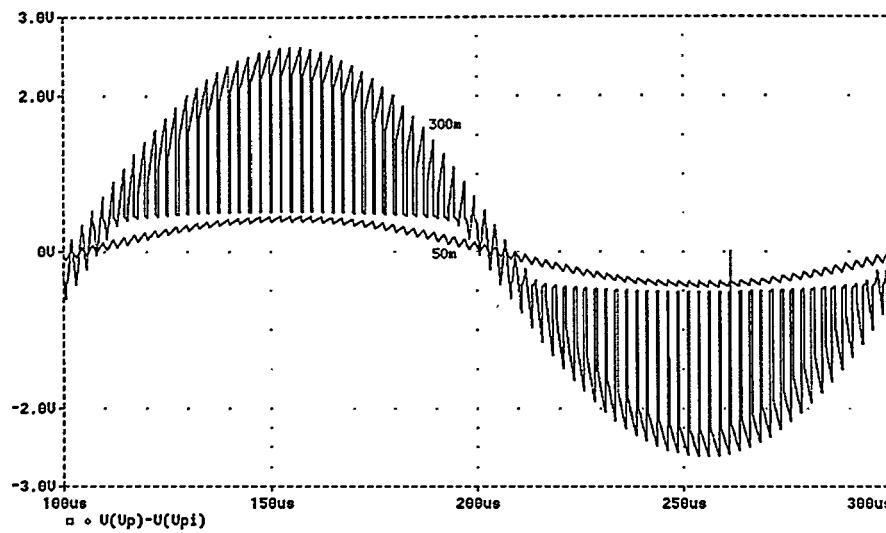

| 4.6.2 PAE case example : Non-stabilized supply .....                       | 128 |

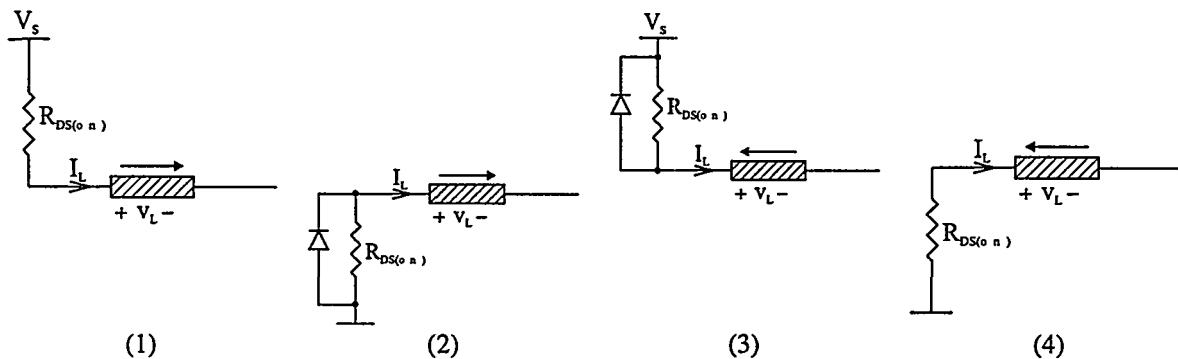

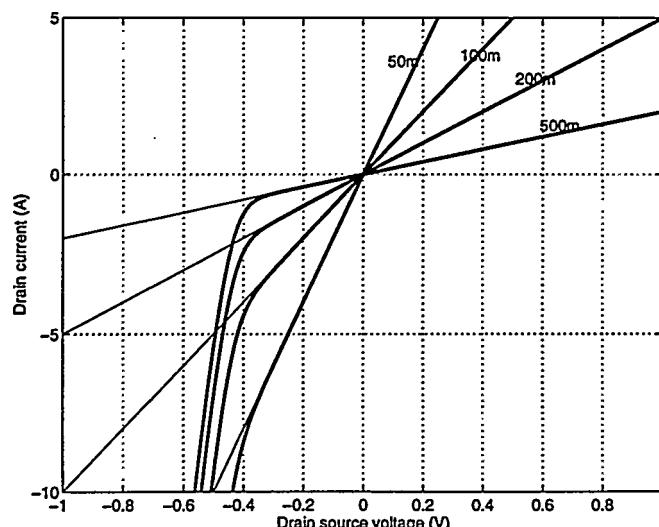

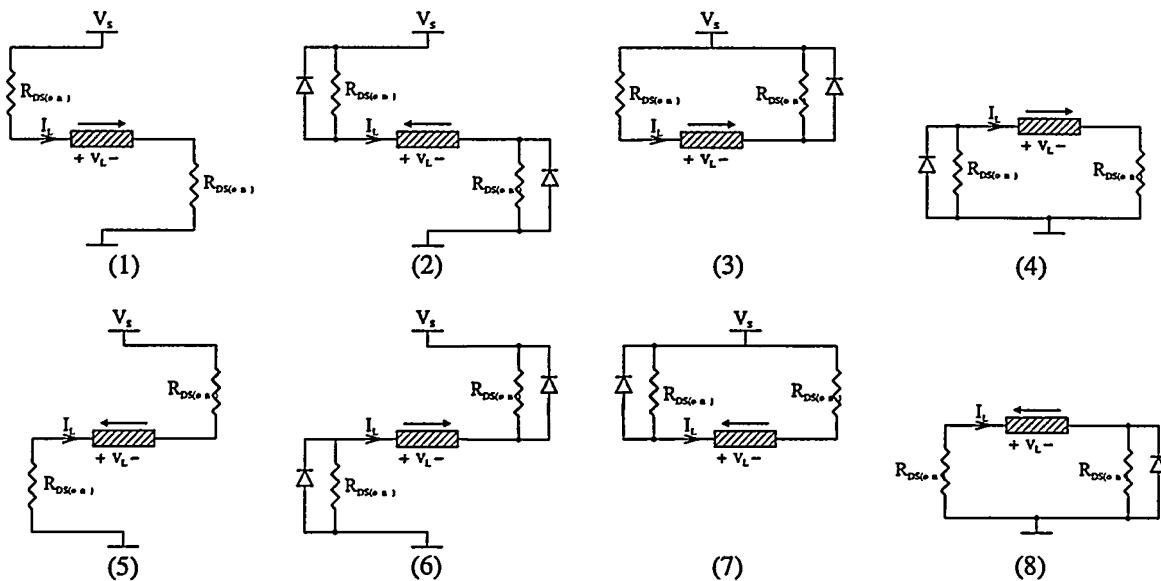

| 4.6.3 Finite switch impedance effects.....                                 | 130 |

| 4.6.4 Other contributions to PAE.....                                      | 135 |

| 4.7 Analog PMA modulator error sources .....                               | 135 |

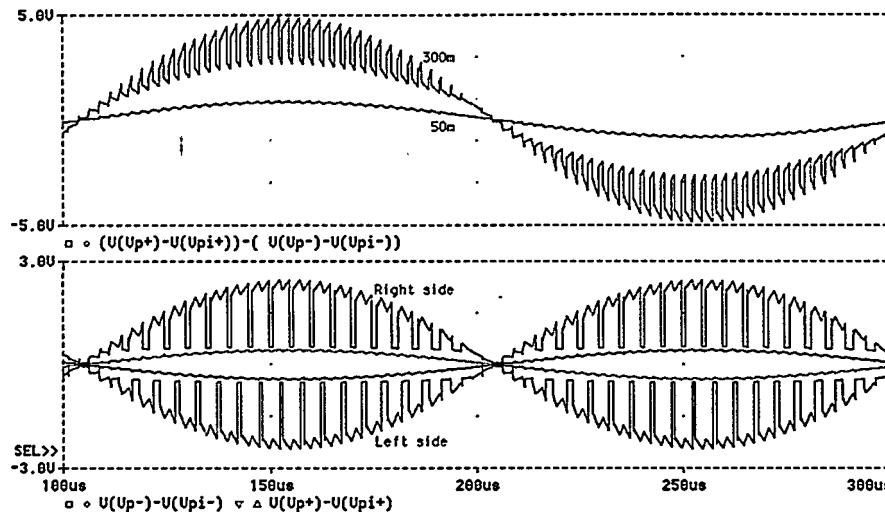

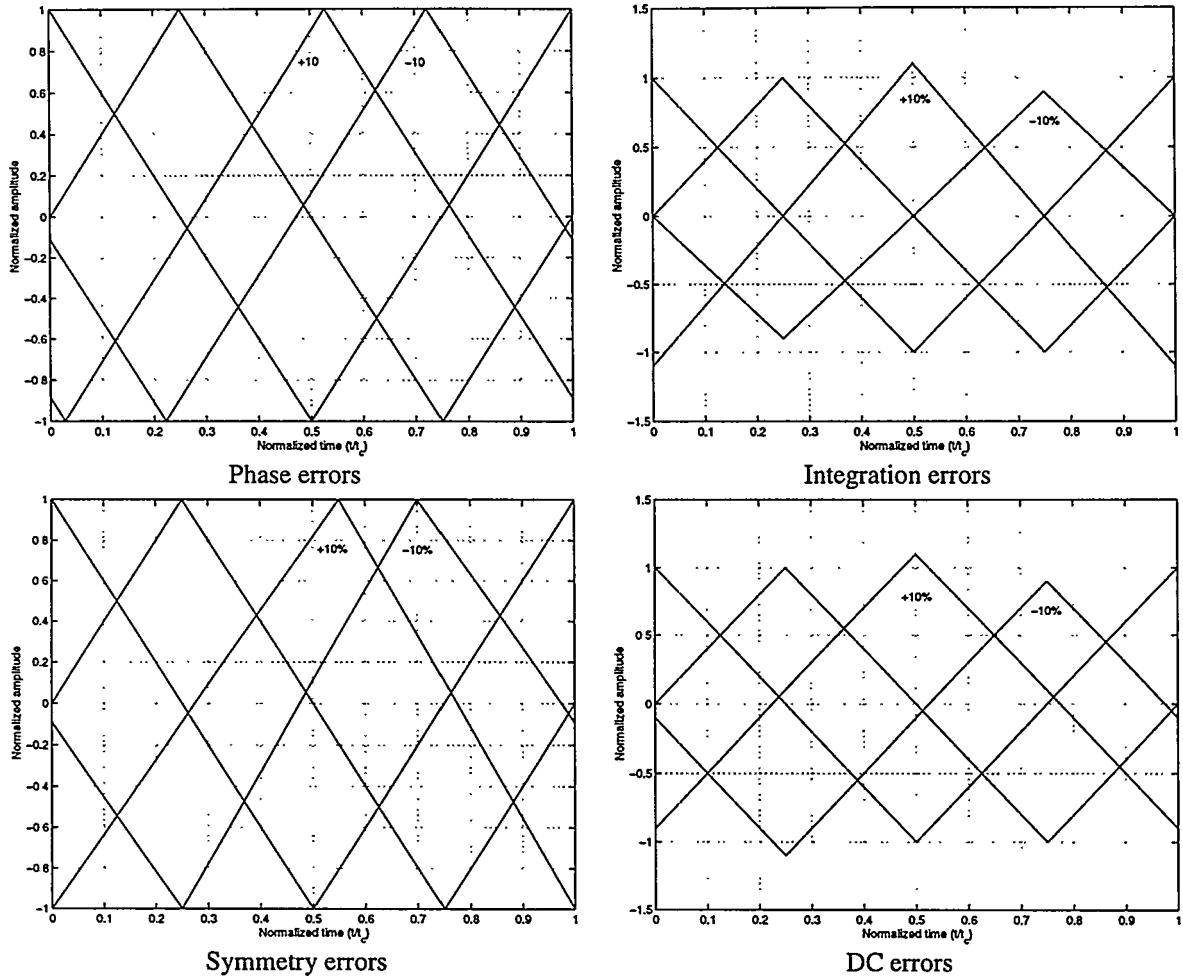

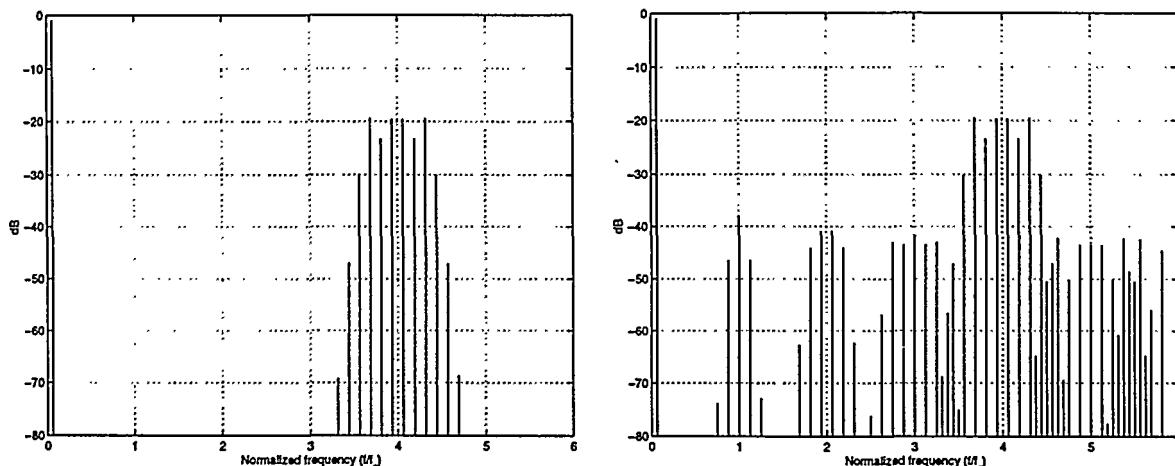

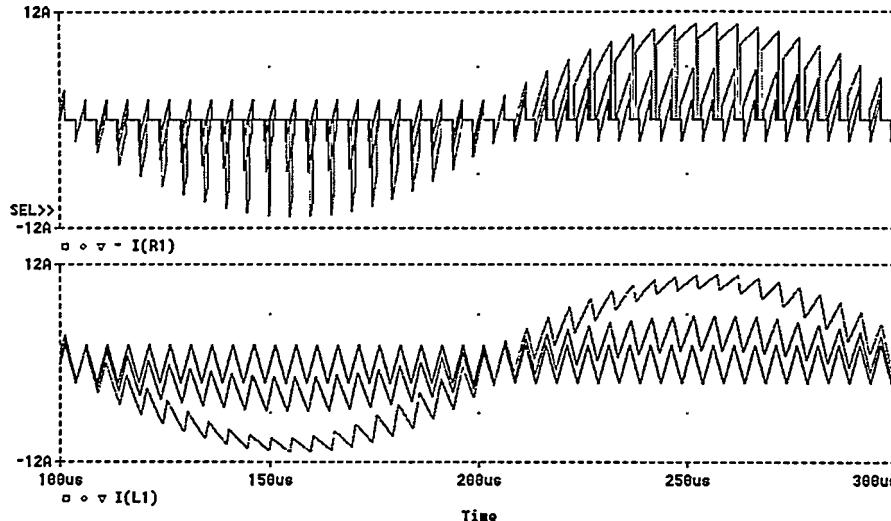

| 4.7.1 Parametric analysis of PSCPWM modulator error sources .....          | 137 |

| 4.8 Summary .....                                                          | 138 |

|                                                                 |     |

|-----------------------------------------------------------------|-----|

| <b>Chapter 5 – Efficiency Optimization.....</b>                 | 139 |

| 5.1 Efficiency in power conversion.....                         | 139 |

| 5.2 Conduction losses.....                                      | 140 |

| 5.3 Switching losses .....                                      | 143 |

| 5.4 Demodulation filter losses.....                             | 146 |

| 5.4.1 Conduction losses.....                                    | 147 |

| 5.4.2 Core losses .....                                         | 147 |

| 5.5 Generalization to BPSC and PSC .....                        | 148 |

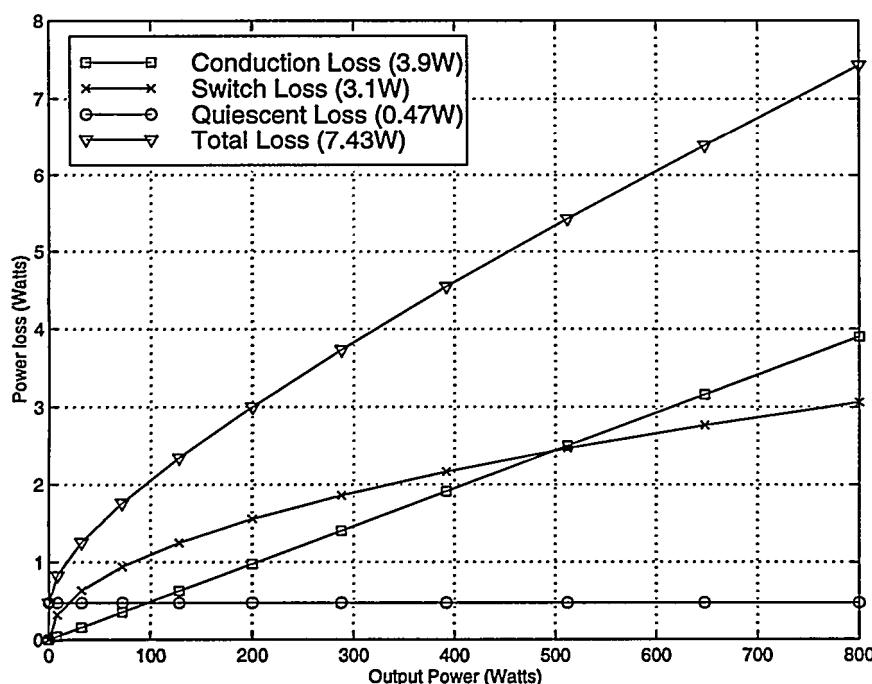

| 5.6 Case example .....                                          | 149 |

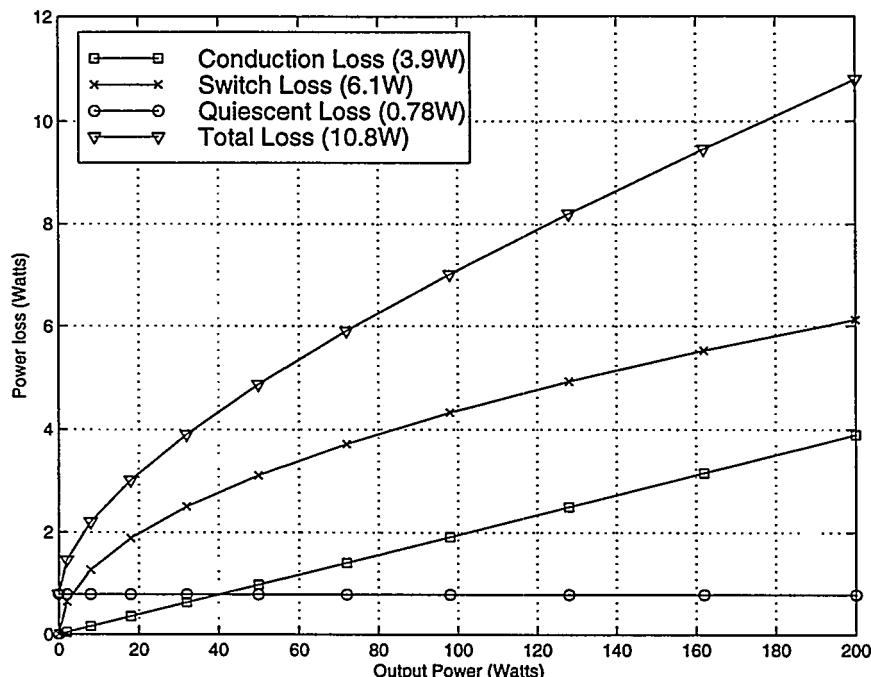

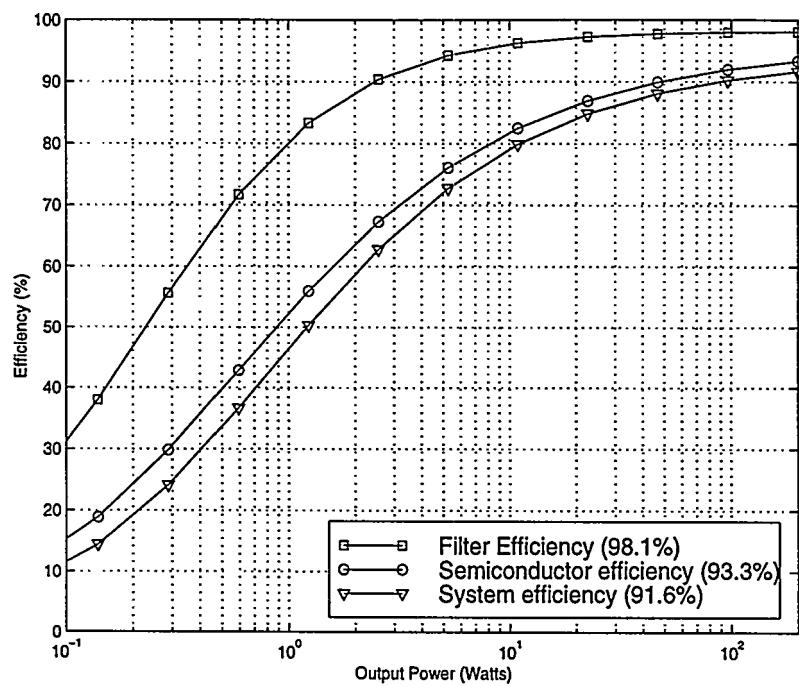

| 5.6.1 Implementation with a simple switching leg.....           | 149 |

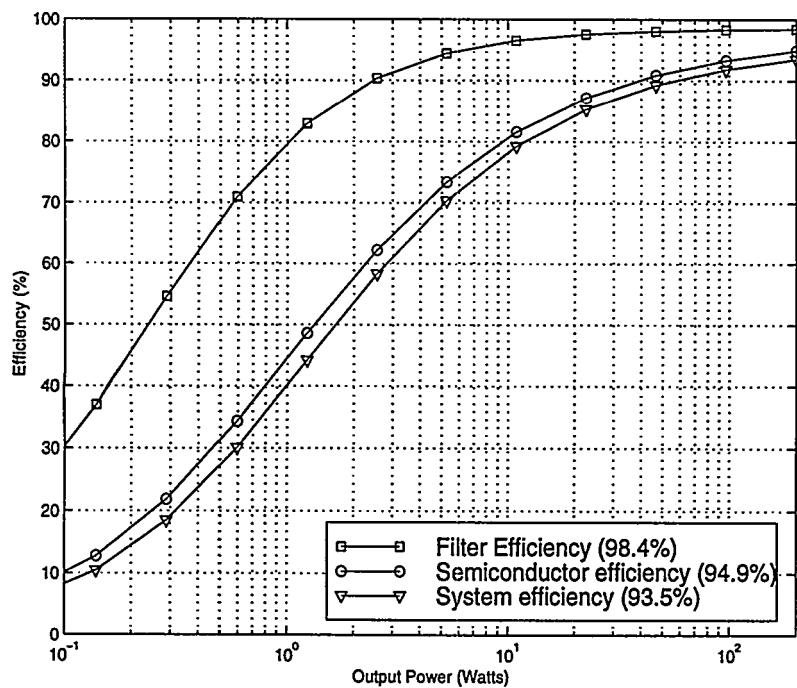

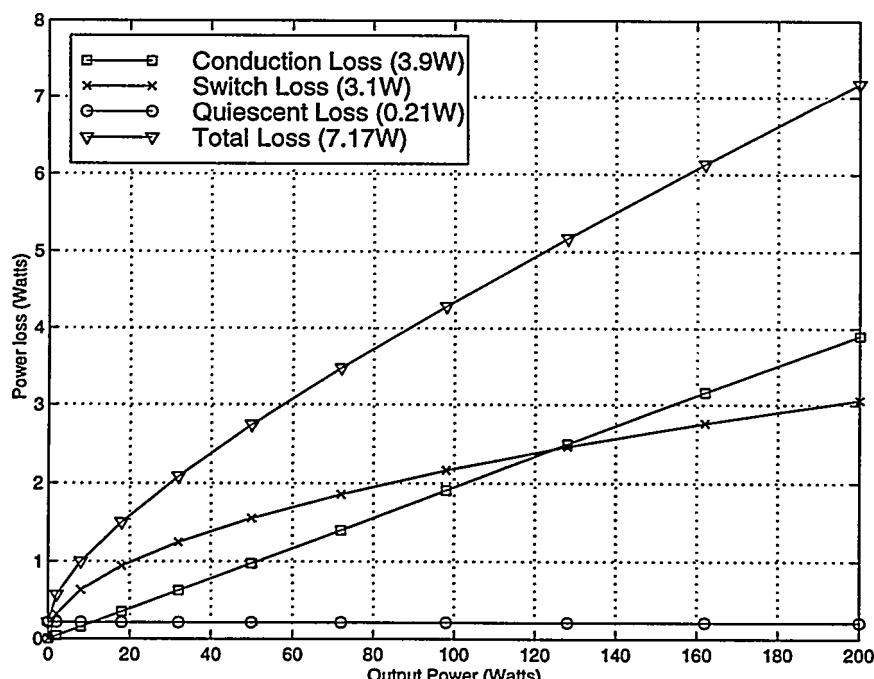

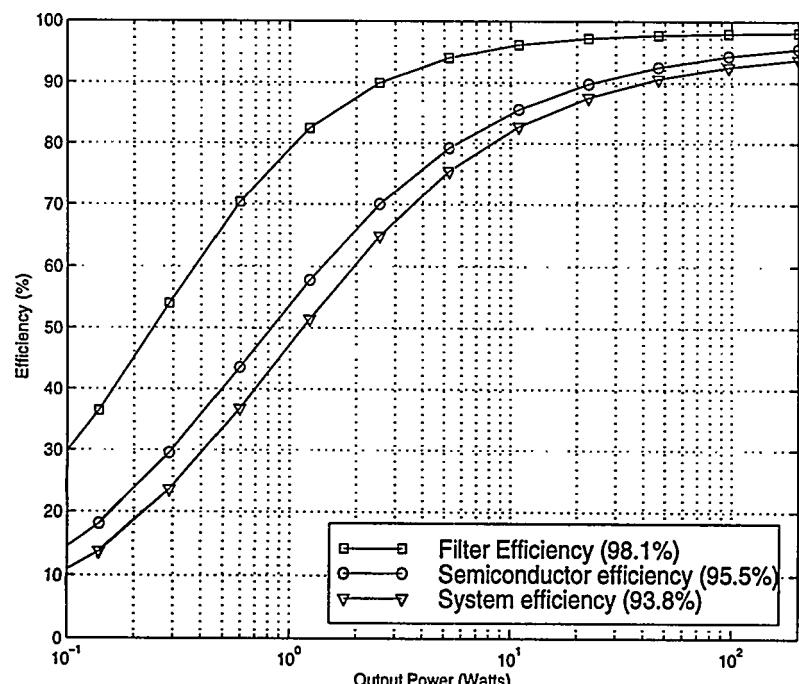

| 5.6.2 BPSC realization (N=2) .....                              | 151 |

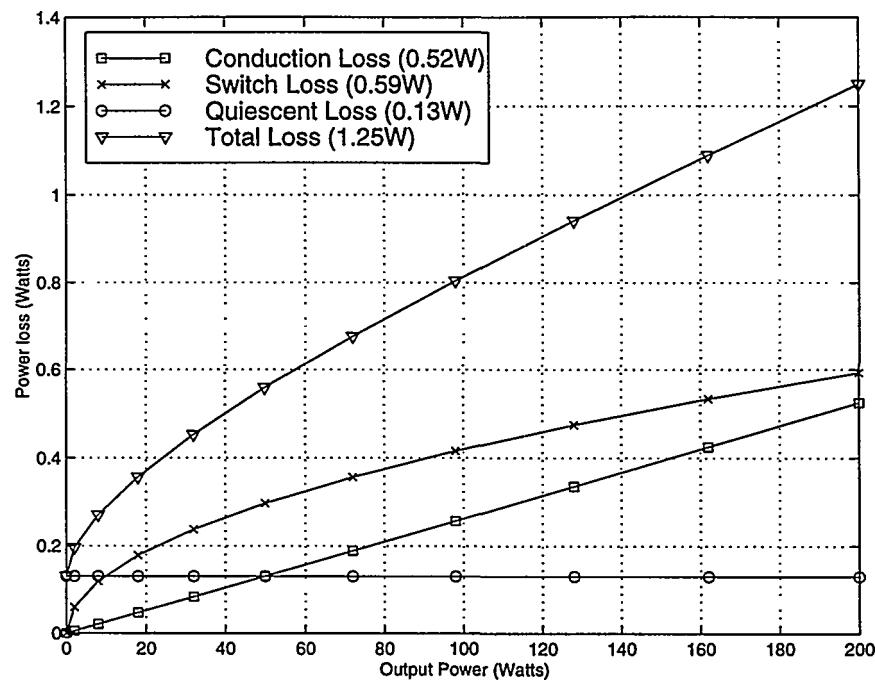

| 5.6.3 BPSC realization (N=4) .....                              | 153 |

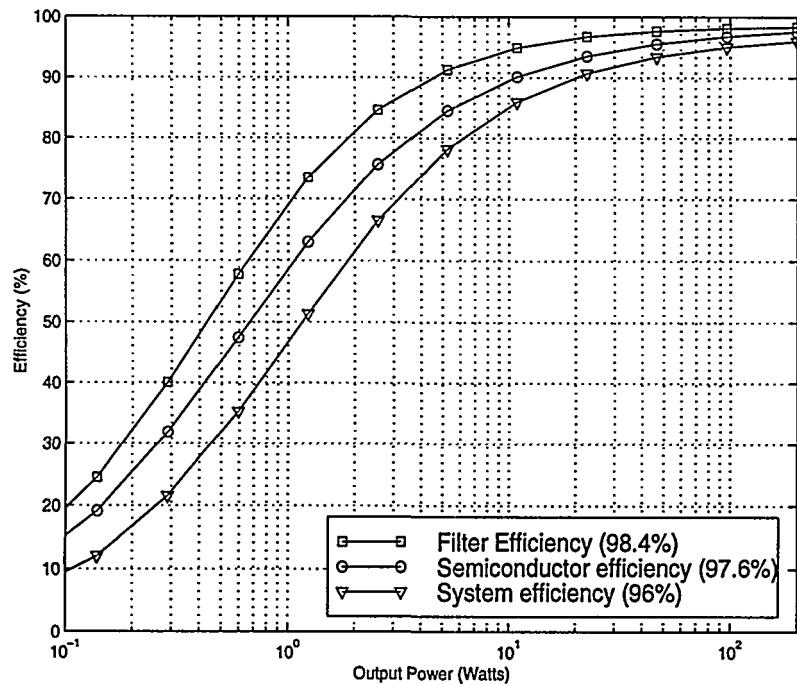

| 5.6.4 BPSC in high power realizations .....                     | 155 |

| 5.7 Summary .....                                               | 156 |

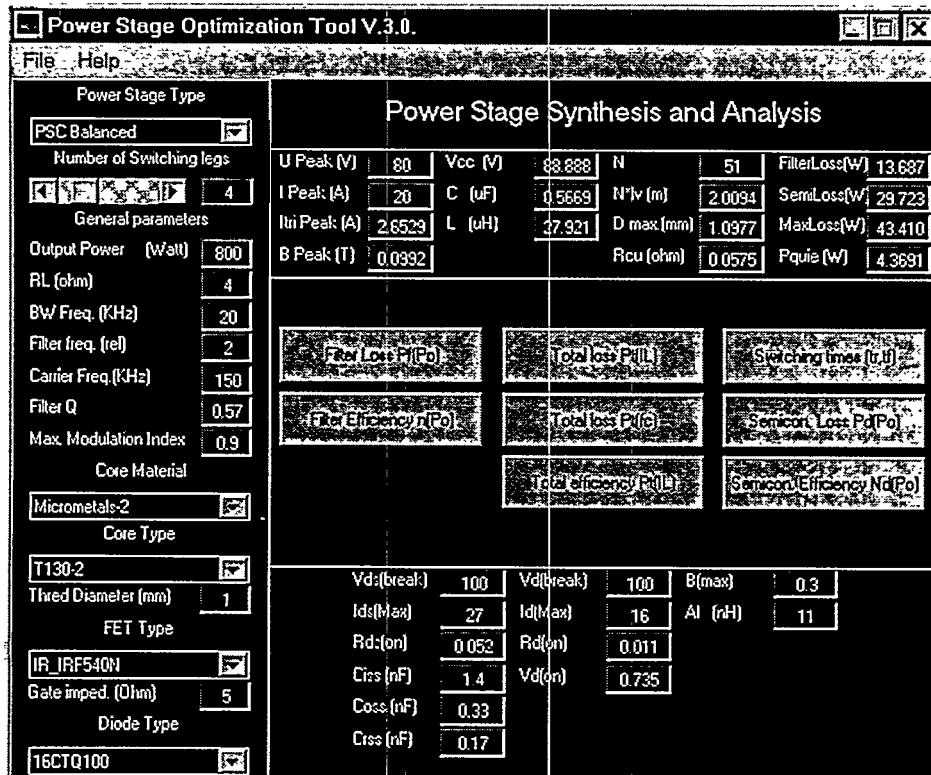

| 5.7.1 PSOT – A MATLAB toolbox for power stage optimization..... | 156 |

| <b>Chapter 6 – Robust Linear Control .....</b>                  | 159 |

| 6.1 Terminology .....                                           | 160 |

| 6.1.1 Evaluating control system performance.....                | 161 |

| 6.1.2 Control system representation and optimization.....       | 162 |

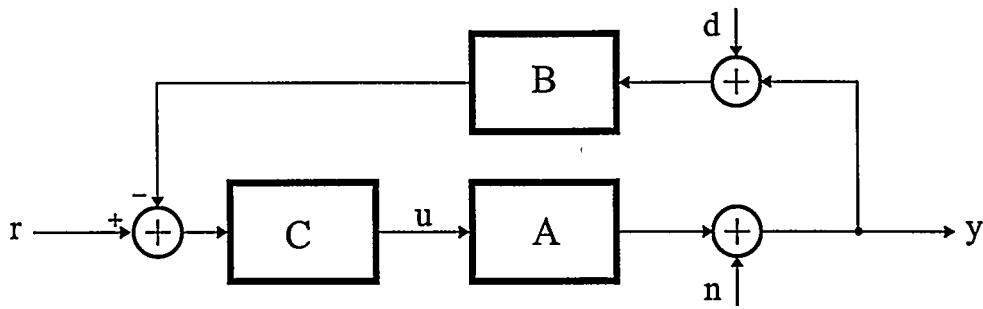

| 6.2 Robust control system design for PMAs.....                  | 163 |

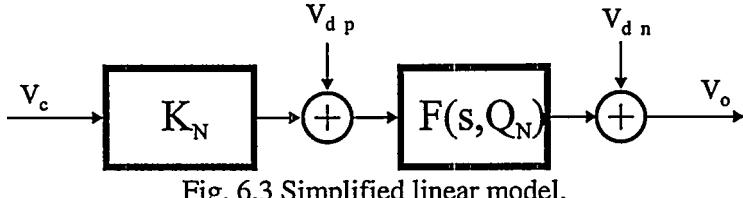

| 6.2.1 System model .....                                        | 163 |

| 6.2.2 Uncertainty and robustness .....                          | 164 |

| 6.2.3 Defining the Uncertainty Set ( <i>US</i> ) .....          | 165 |

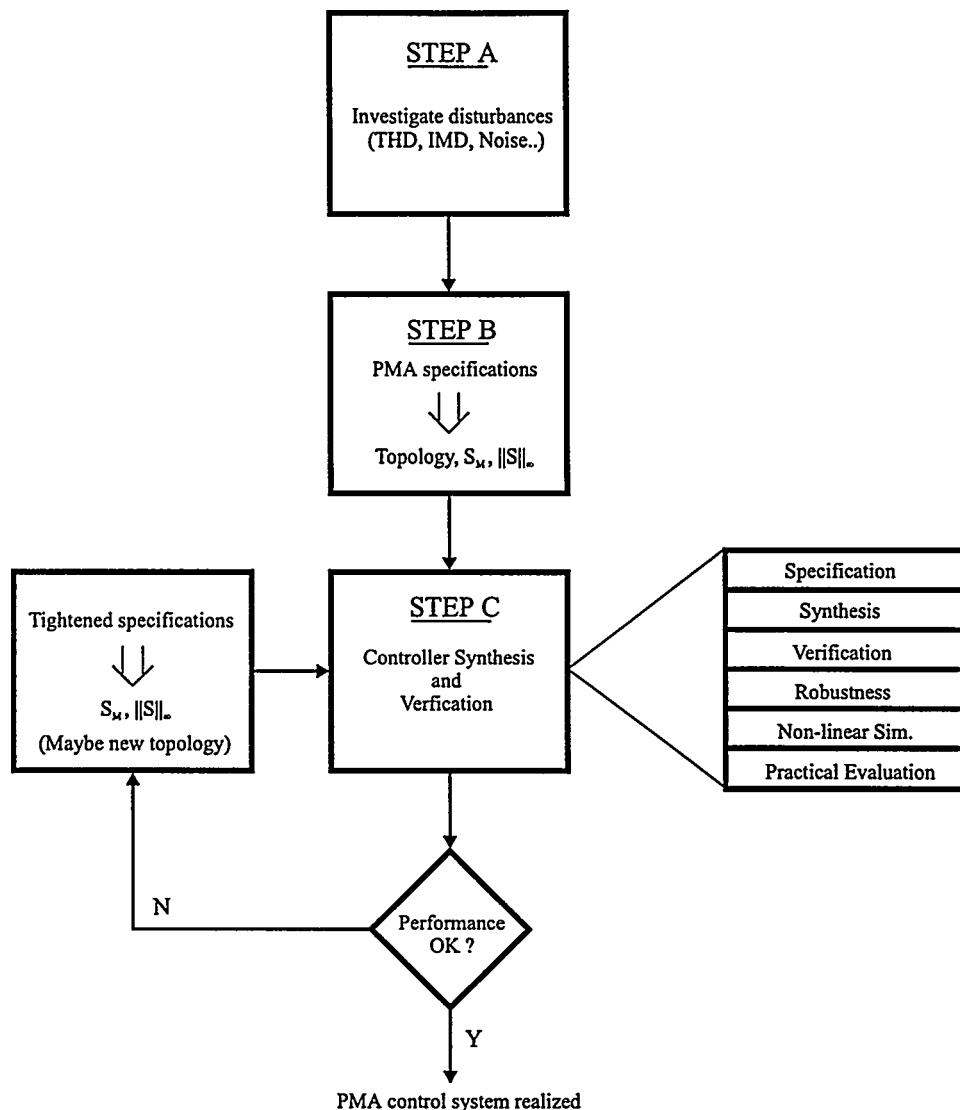

| 6.3 Control system design methodology .....                     | 166 |

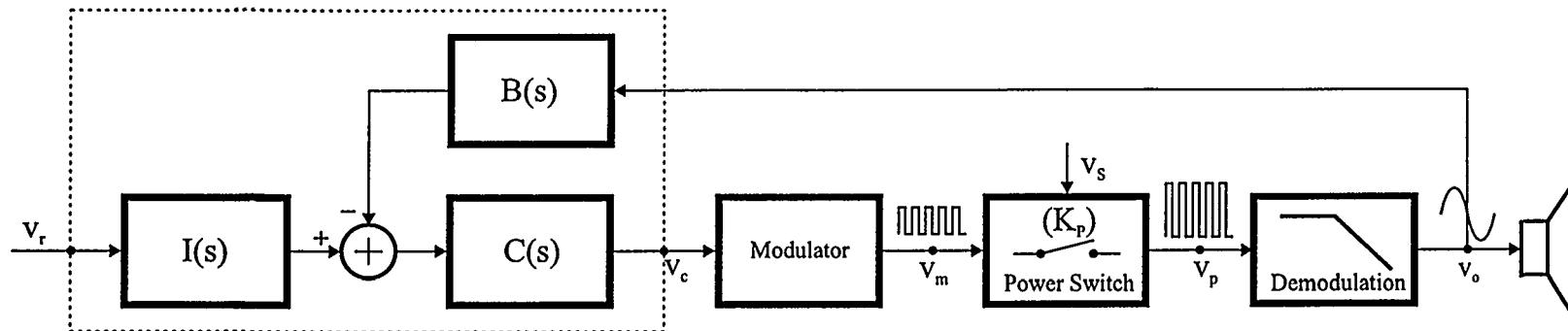

| 6.3.1 Generalized controller synthesis and verification .....   | 168 |

| 6.3.2 Generalized performance considerations .....              | 169 |

| 6.3.3 General loop shaping constraints .....                    | 169 |

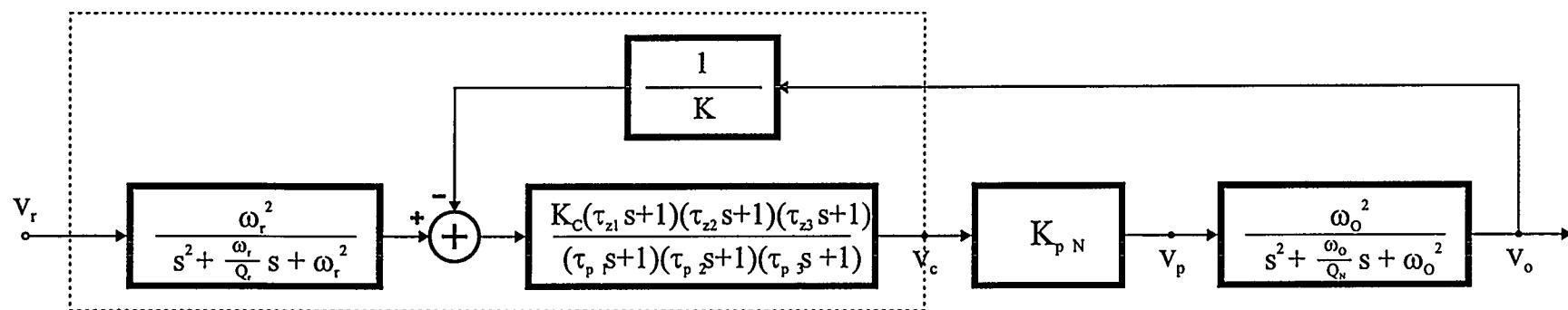

| 6.3.4 Definition of linear control structures .....             | 171 |

| 6.4 Voltage Feedback Control Topology 1 (VFC1).....             | 173 |

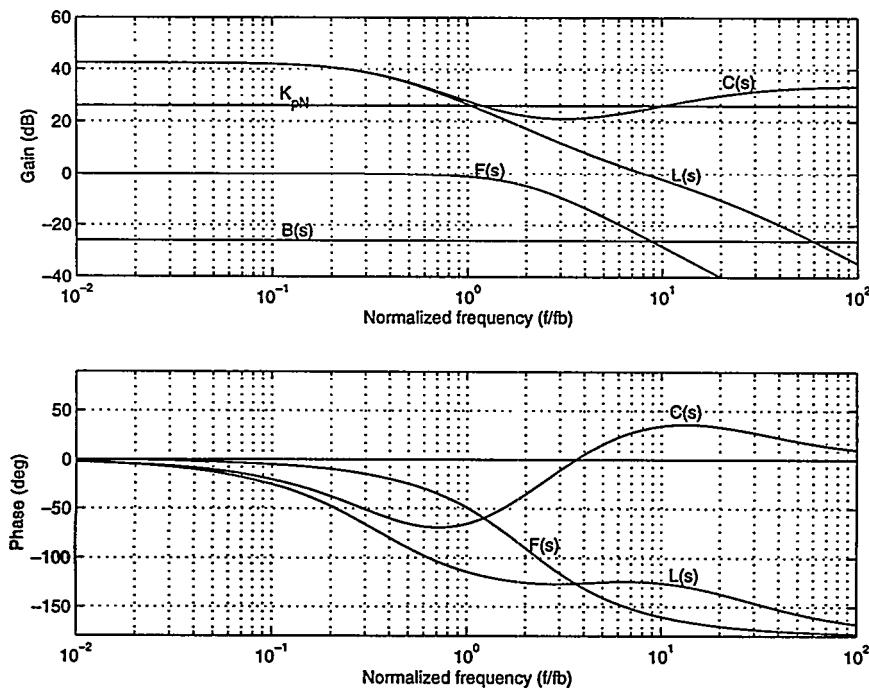

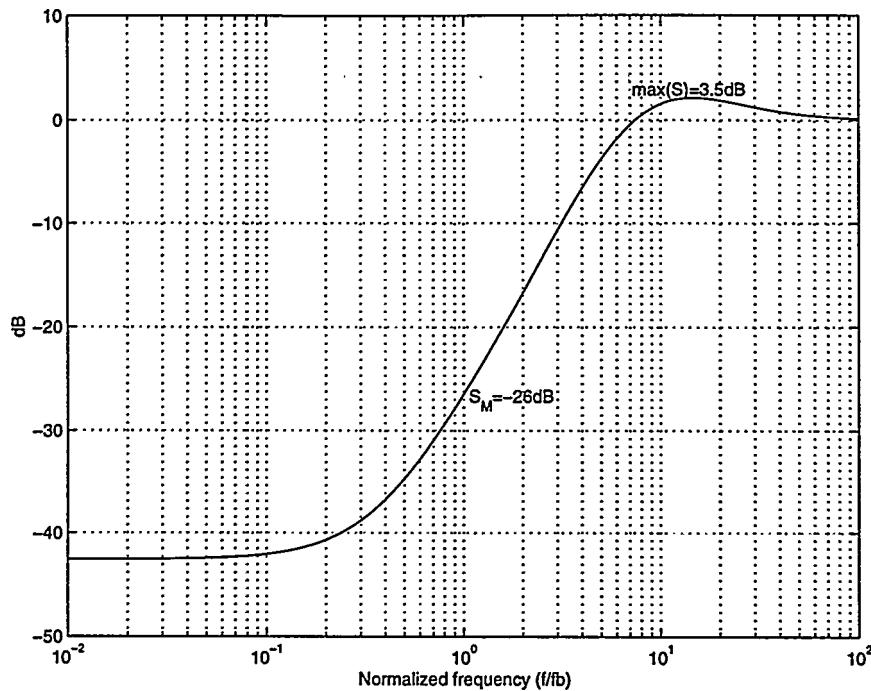

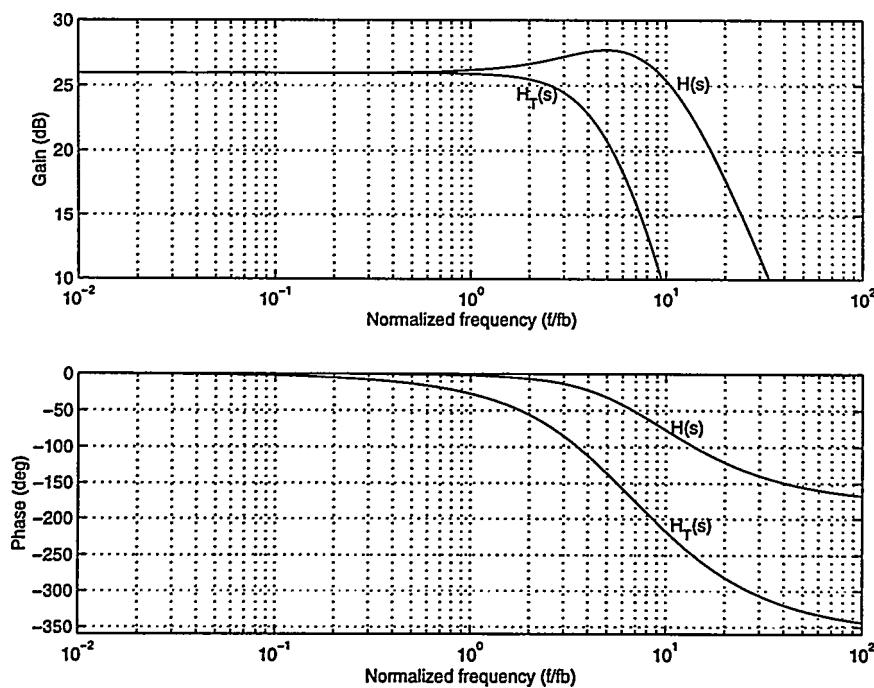

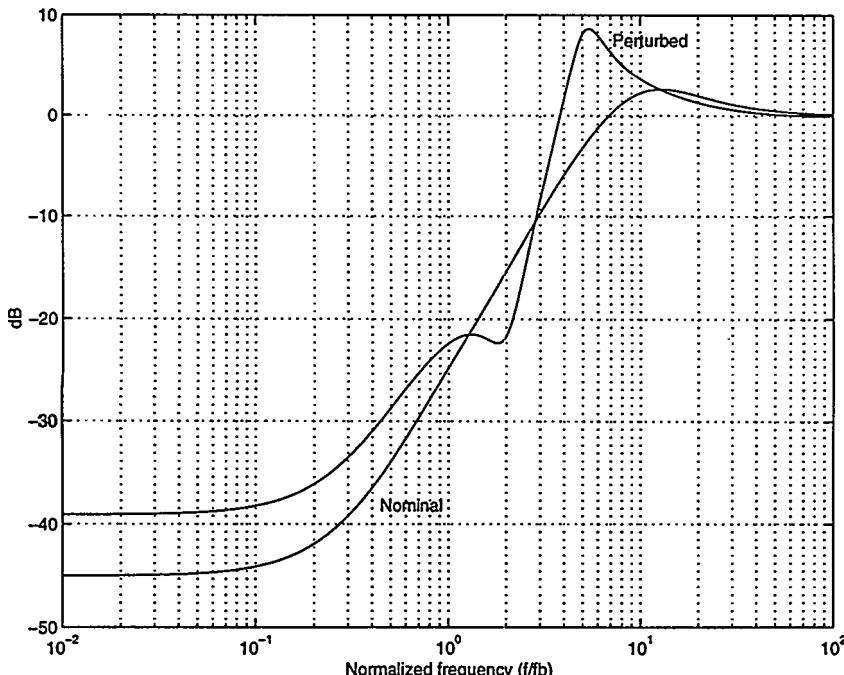

| 6.4.1 Loop shaping .....                                        | 174 |

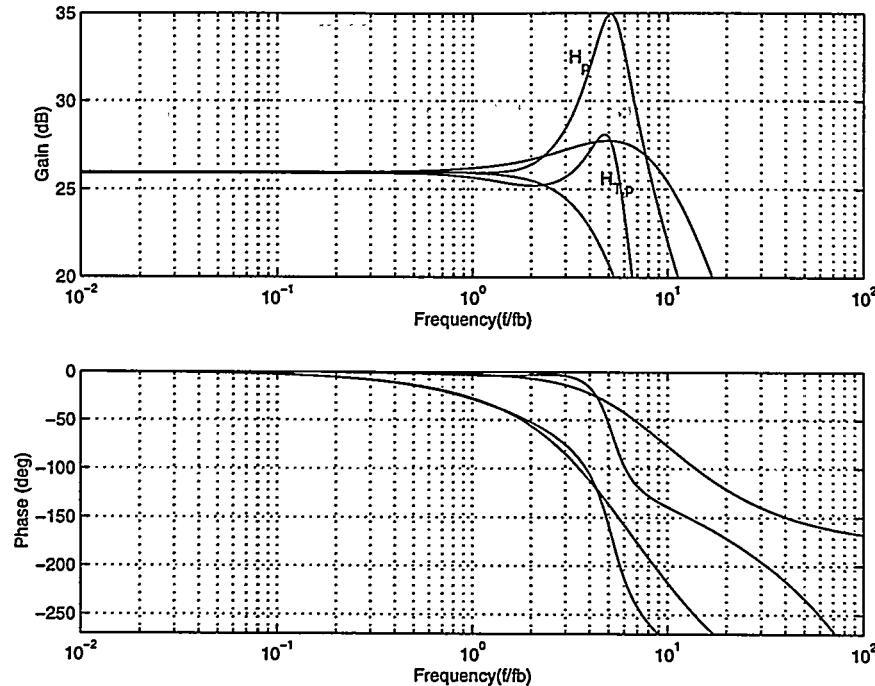

| 6.4.2 VFC1 Case example synthesis .....                         | 175 |

| 6.5 Voltage Feedback Control Topology 2 (VFC2).....             | 185 |

| 6.5.1 Loop shaping .....                                        | 185 |

| 6.5.2 VFC2 case example.....                                    | 186 |

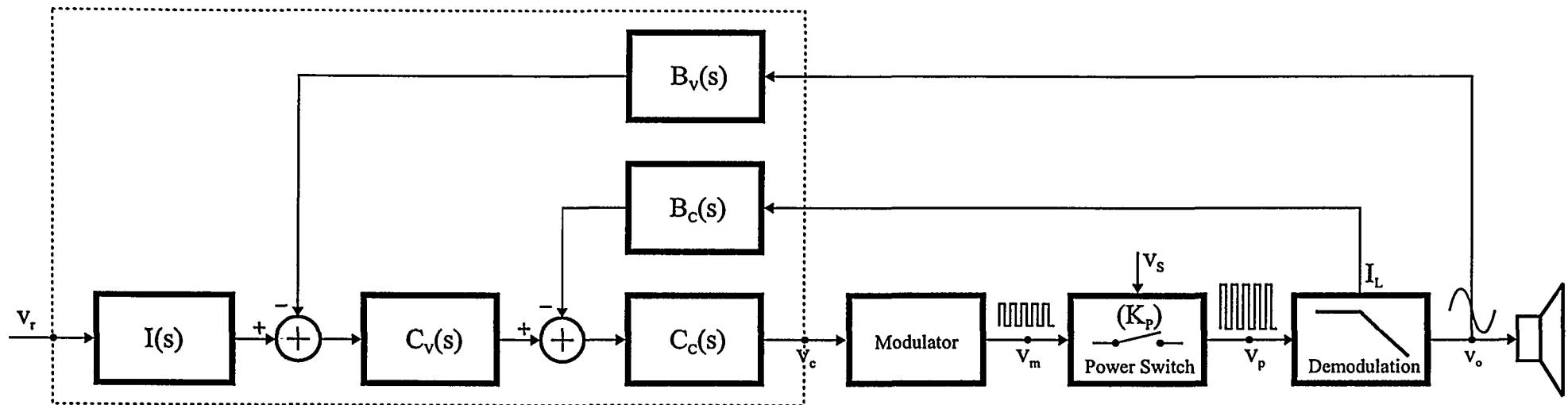

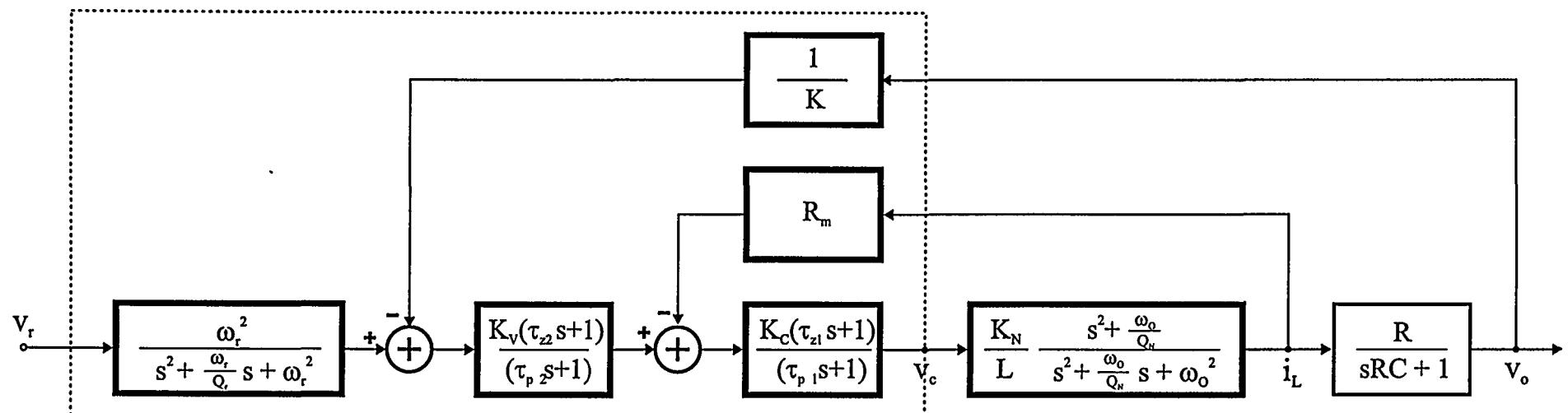

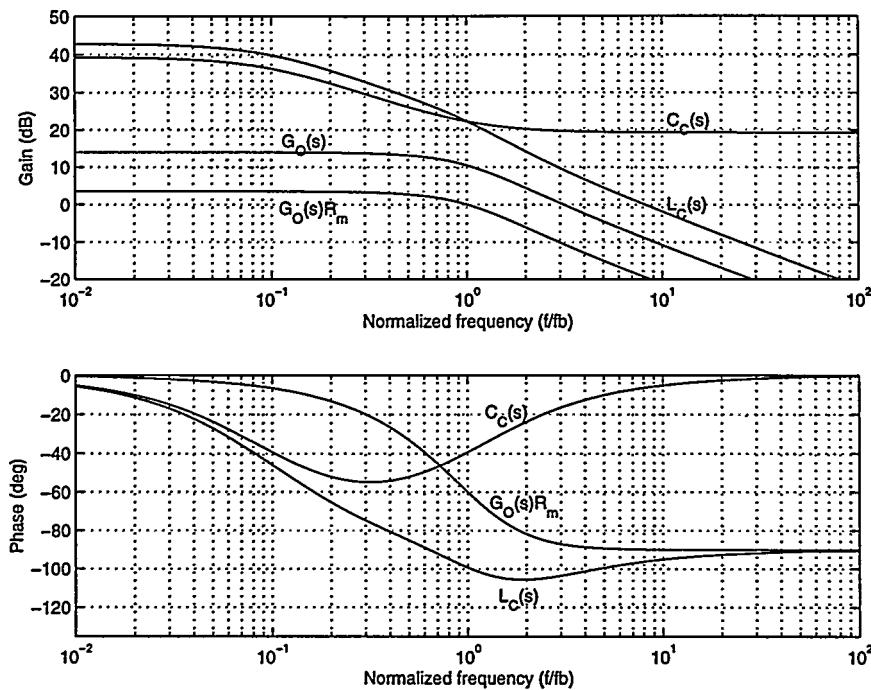

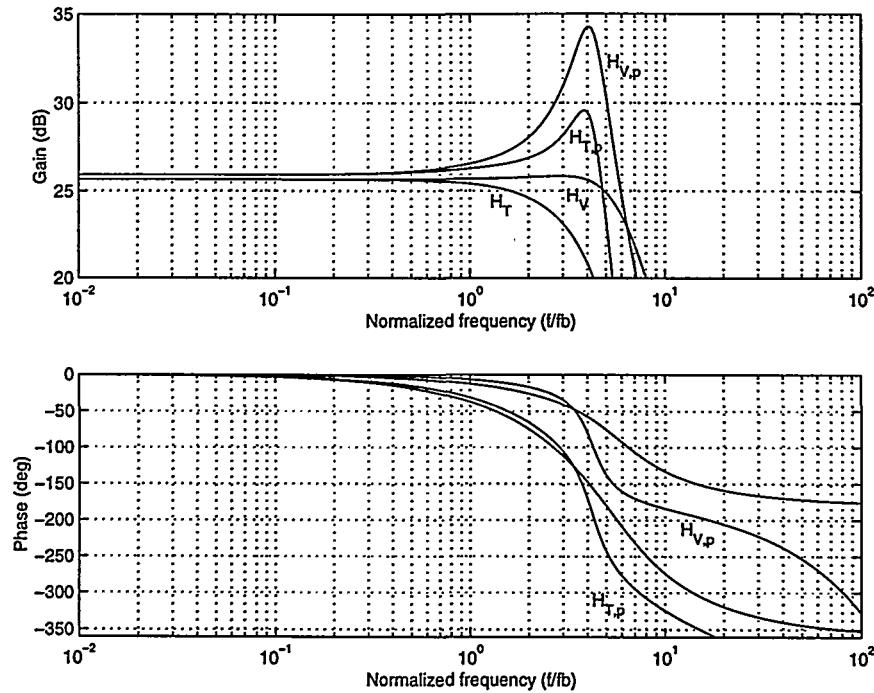

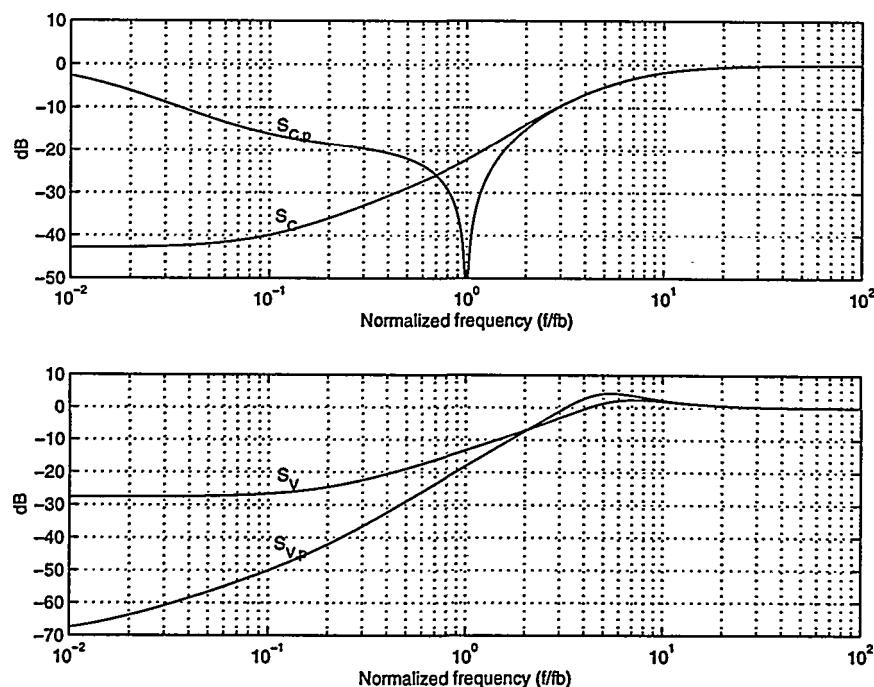

| 6.6 Current Voltage Feedback Control Topology (CVFC).....       | 192 |

| 6.6.1 Current loop analysis.....                                | 192 |

| 6.6.2 The voltage analysis .....                                | 194 |

| 6.6.3 Current and voltage loop shaping.....                     | 194 |

| 6.6.4 CVFC Case example .....                                   | 195 |

| 6.7 Summary .....                                               | 205 |

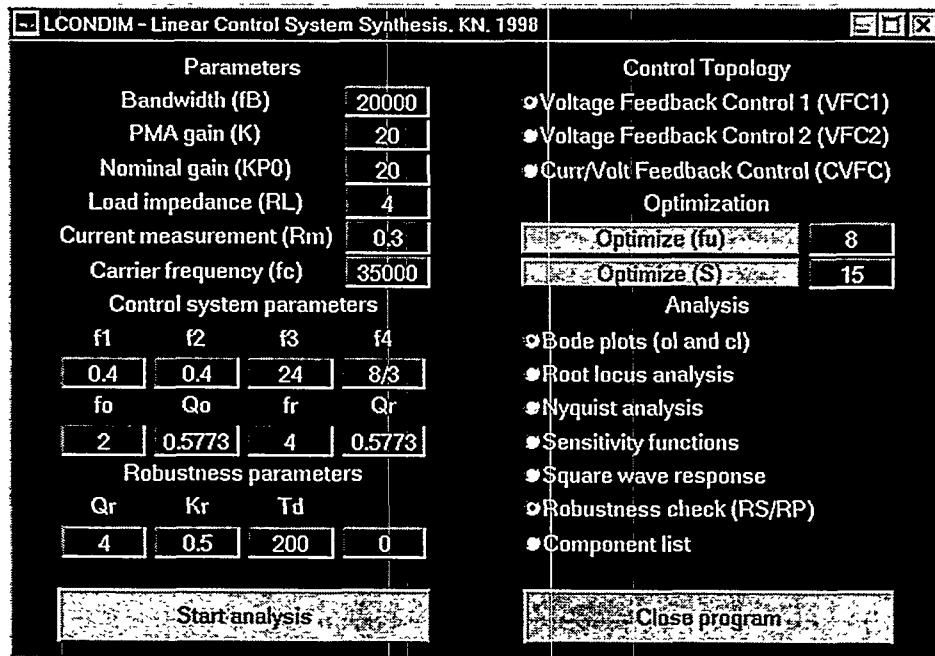

| 6.7.1 LCONDIM design toolbox for MATLAB .....                   | 206 |

| <b>Chapter 7 - Optimized Linear Control .....</b>               | 207 |

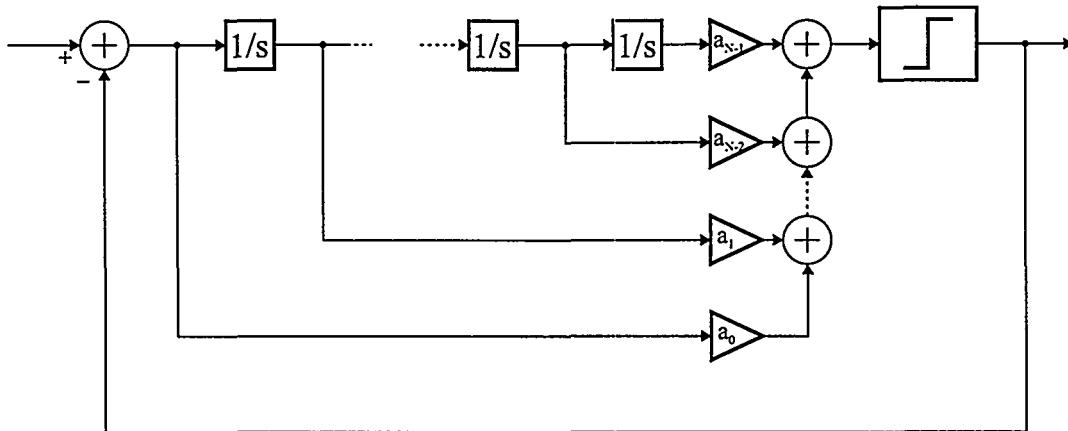

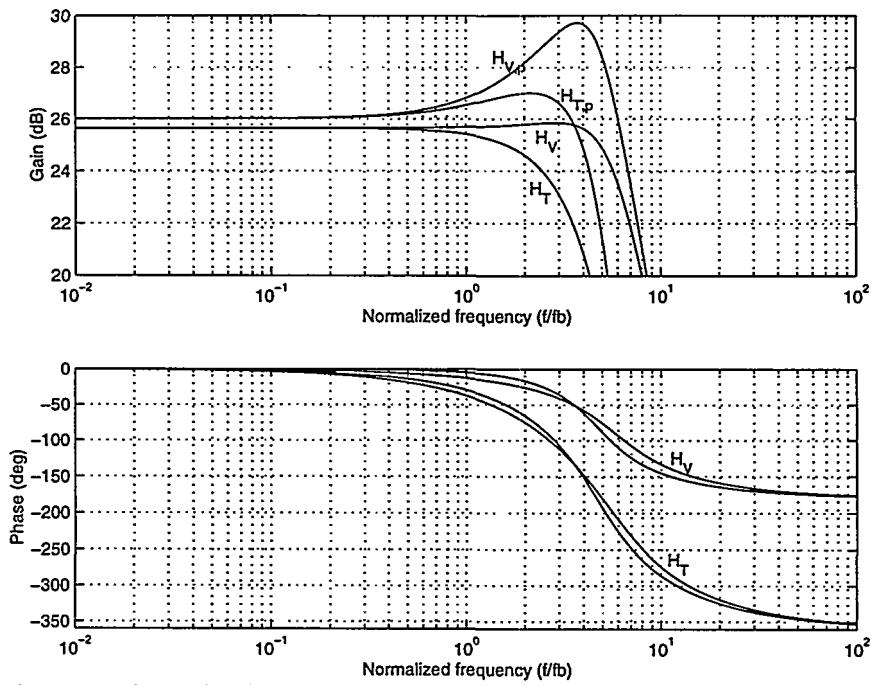

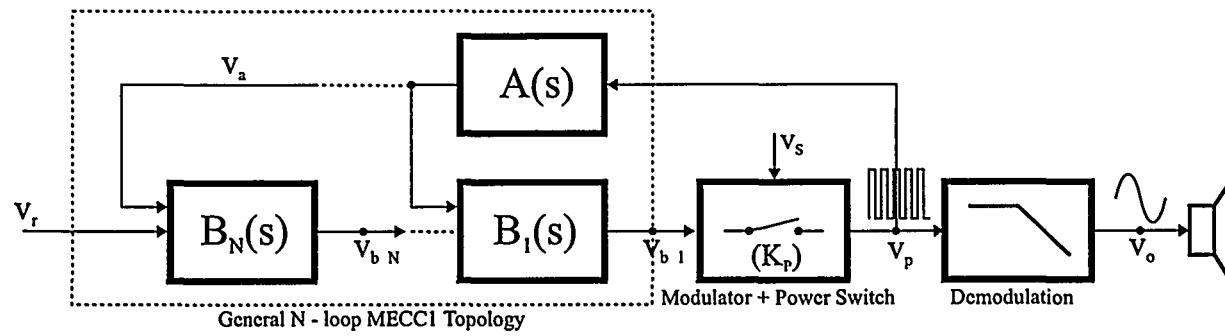

| 7.1 Multivariable Enhanced Cascade Control (MECC).....          | 207 |

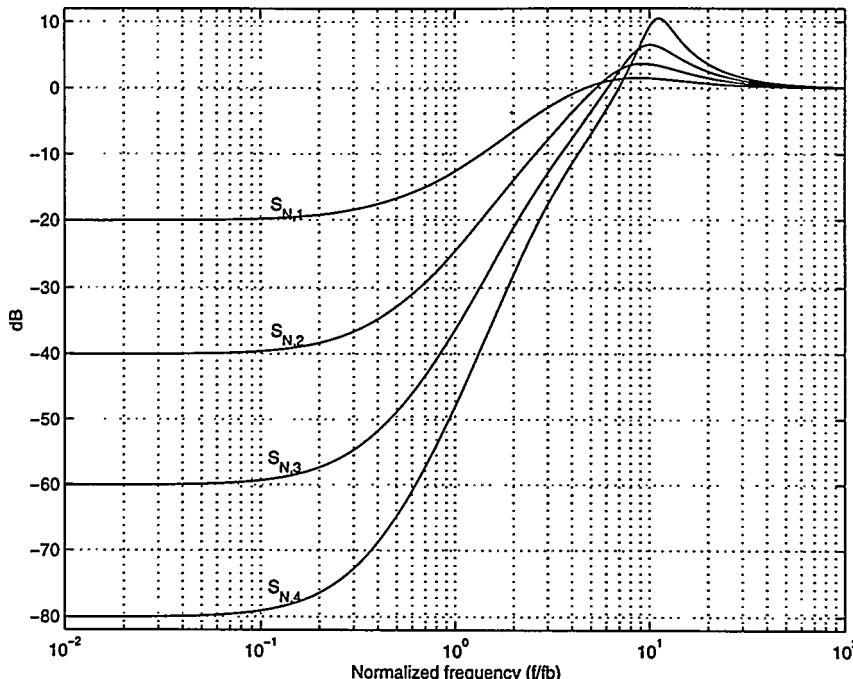

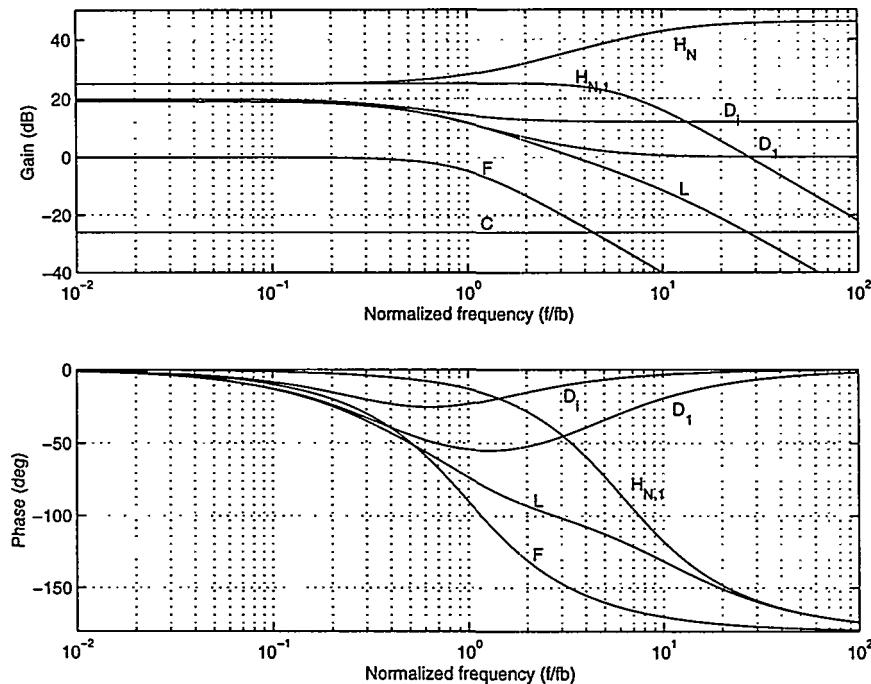

| 7.1.1 Loop prototype based MECC(N) synthesis .....              | 210 |

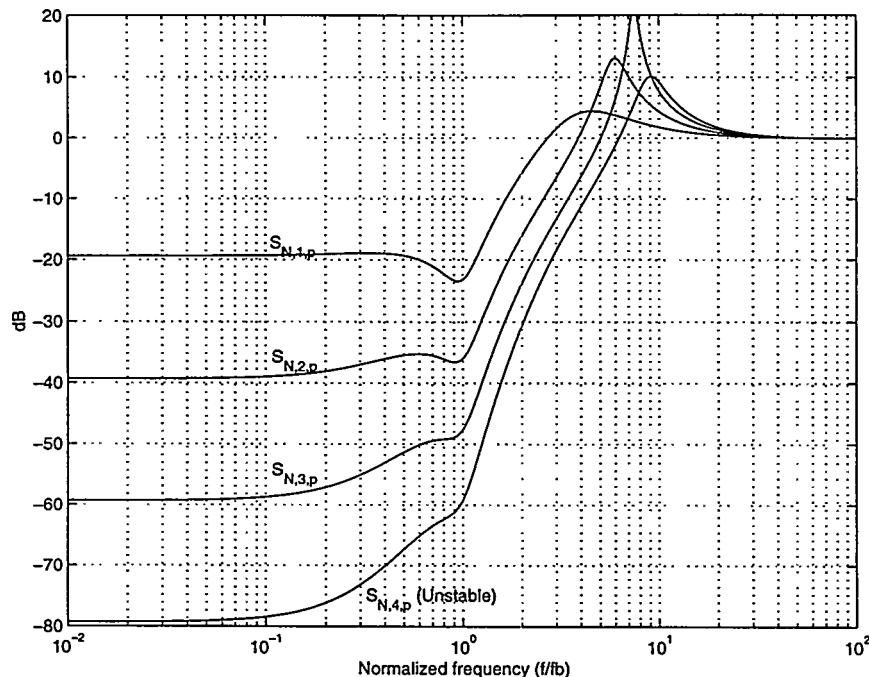

| 7.1.2 MECC(N) properties .....                                  | 211 |

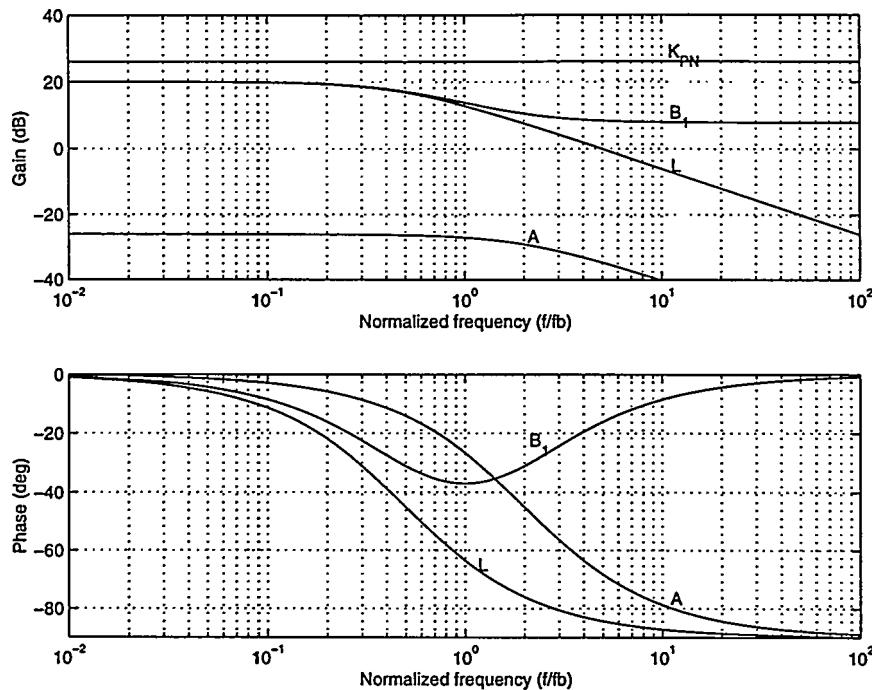

| 7.1.3 MECC(N) loop shaping .....                                | 213 |

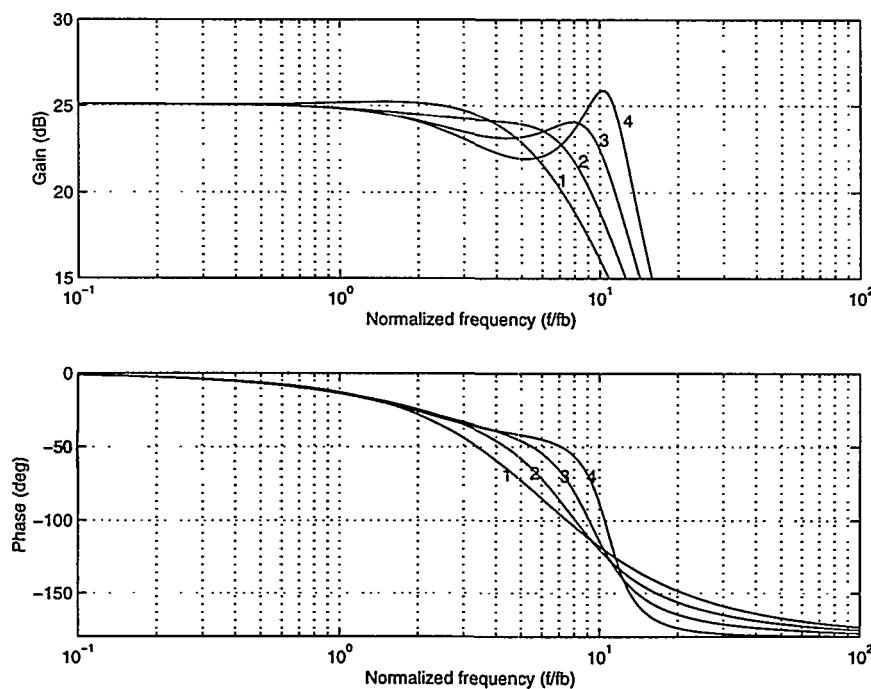

| 7.1.4 MECC(N) case example .....                                | 214 |

|                                                   |                                                           |     |

|---------------------------------------------------|-----------------------------------------------------------|-----|

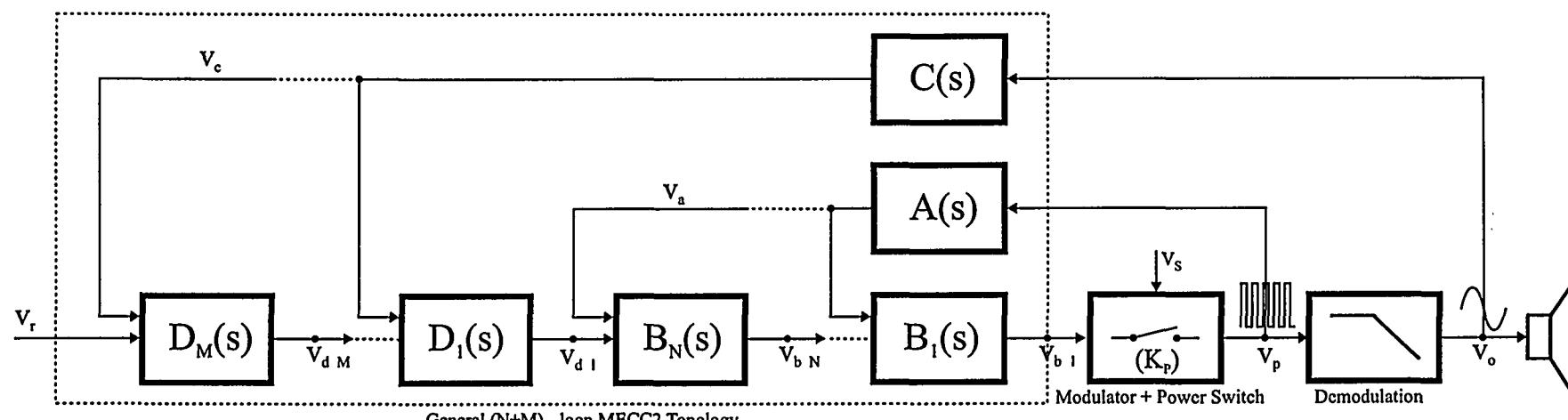

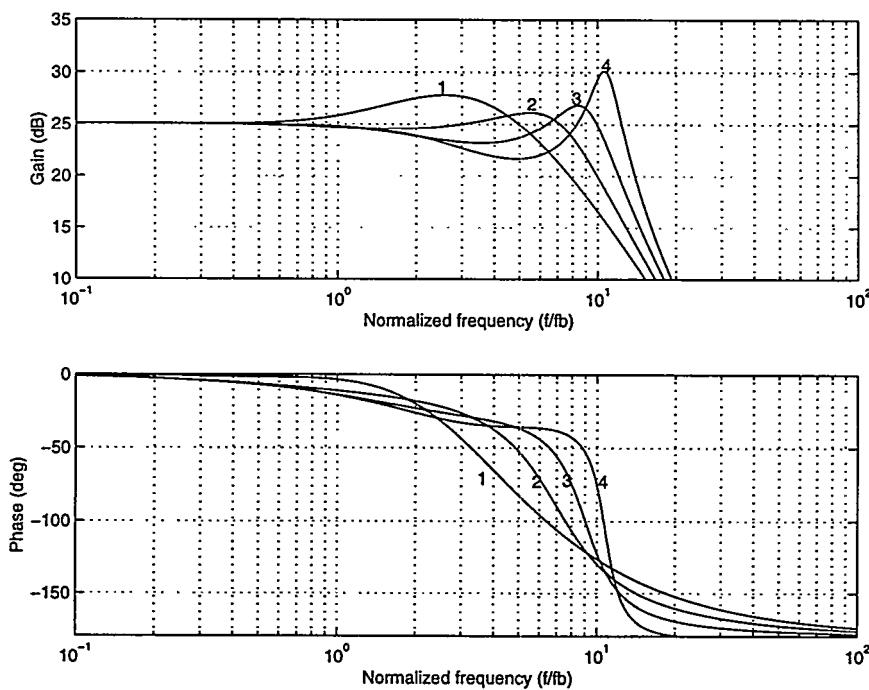

| 7.2                                               | MECC(N,M) .....                                           | 225 |

| 7.2.1                                             | Loop prototype based MECC(N,M) synthesis.....             | 225 |

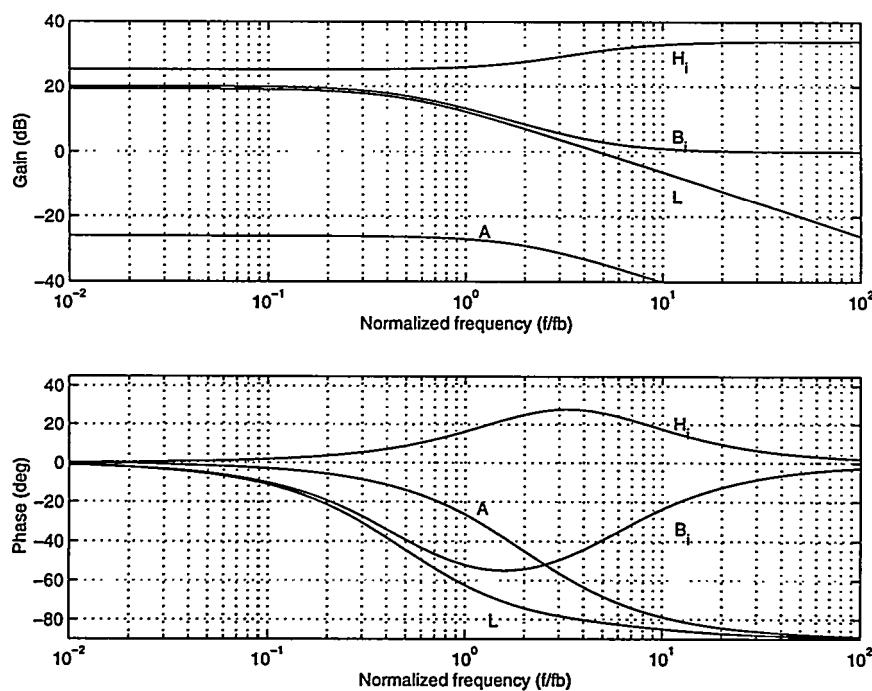

| 7.2.2                                             | MECC(N,M) properties .....                                | 226 |

| 7.2.3                                             | MECC(N,M) loop shaping.....                               | 227 |

| 7.2.4                                             | MECC(N,M) case example.....                               | 228 |

| 7.3                                               | Summary.....                                              | 234 |

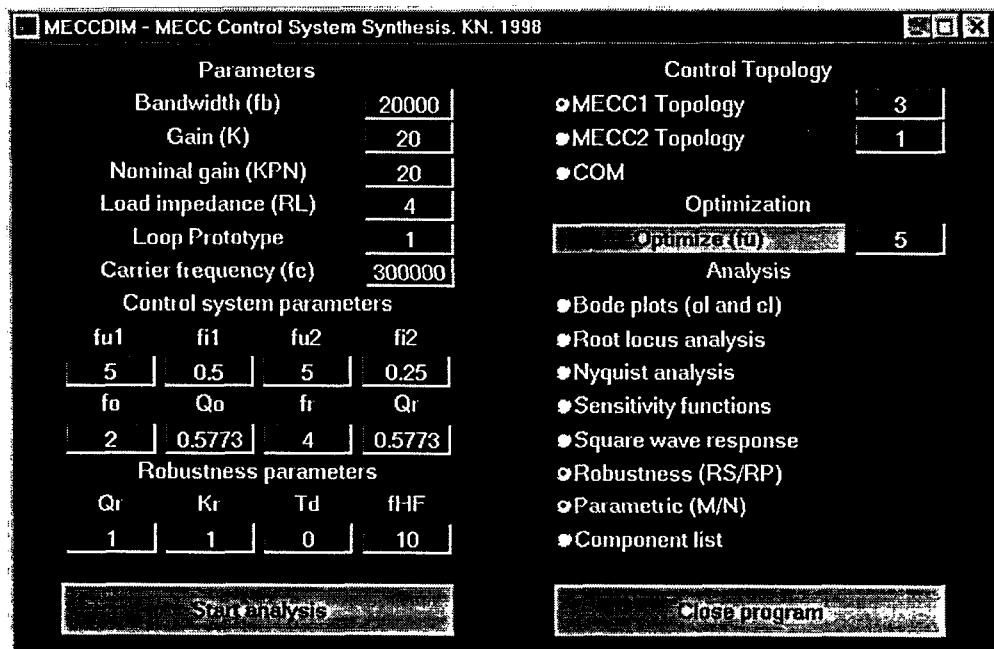

| 7.3.1                                             | MECCDIM – A GUI controlled toolbox for MATLAB .....       | 236 |

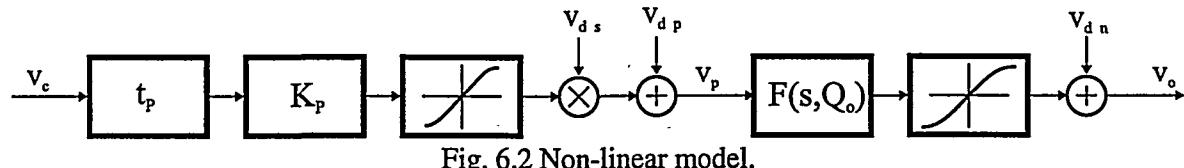

| <b>Chapter 8 – Non-Linear Control</b> .....       | 237                                                       |     |

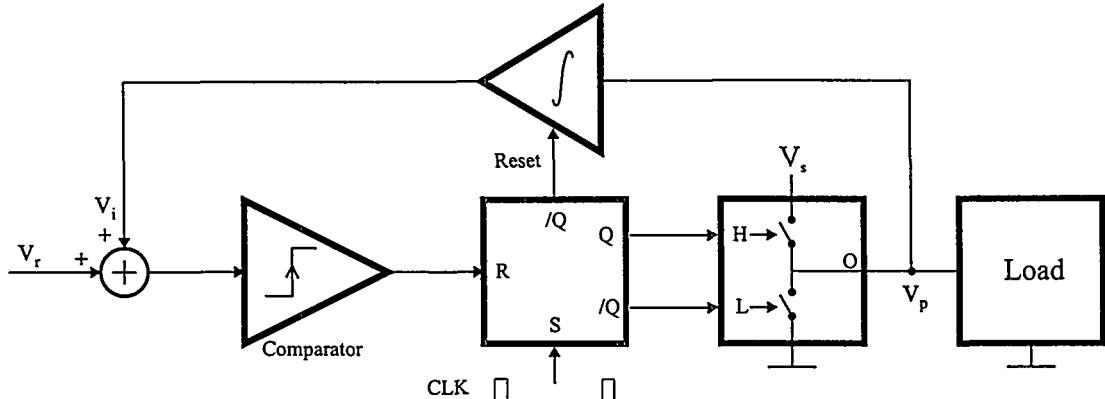

| 8.1                                               | Non-linear One Cycle Control .....                        | 238 |

| 8.1.1                                             | Fundamental limitations.....                              | 239 |

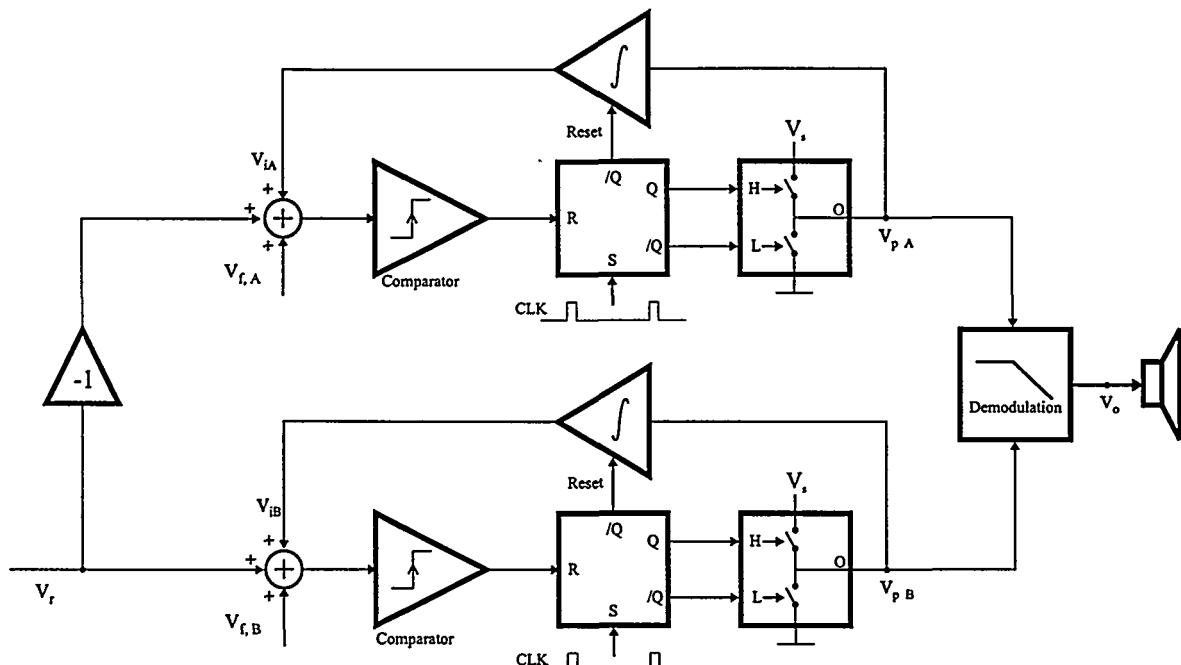

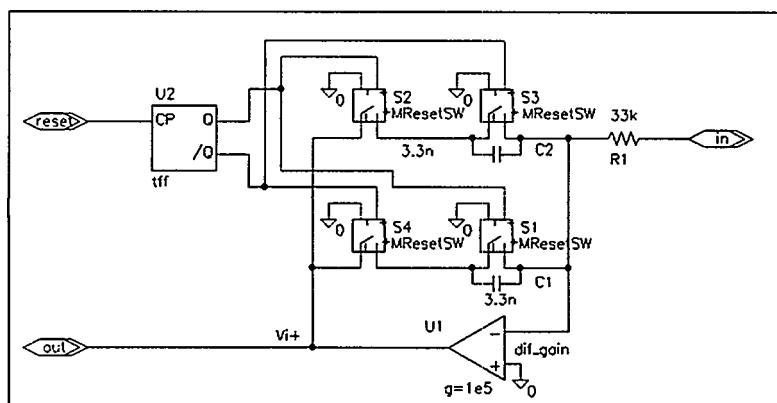

| 8.2                                               | Enhanced non-linear control .....                         | 240 |

| 8.2.1                                             | TOCC synthesis .....                                      | 241 |

| 8.2.2                                             | TOCC non-linear modeling and simulation.....              | 241 |

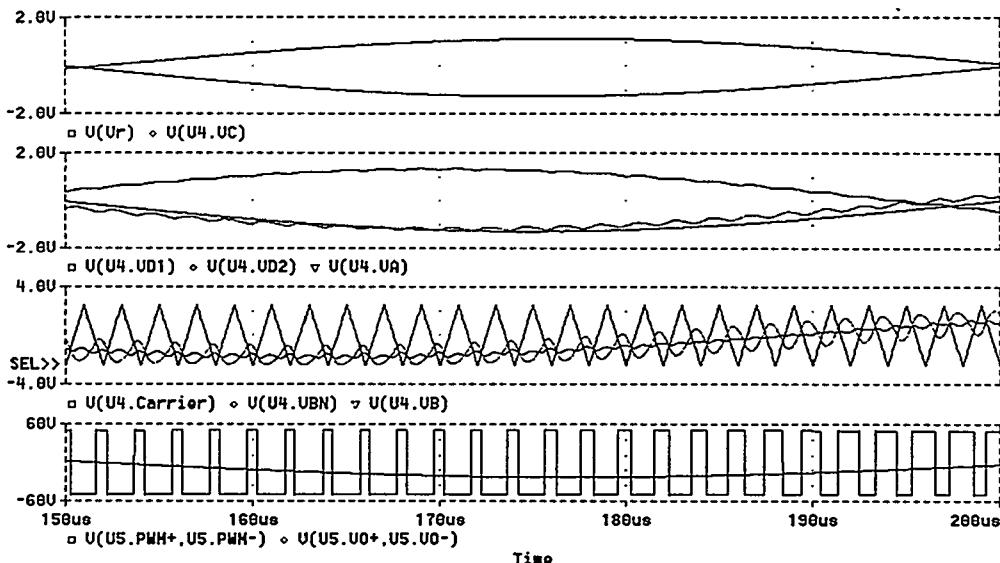

| 8.2.3                                             | TOCC case example .....                                   | 242 |

| 8.2.4                                             | TOCC extensions.....                                      | 246 |

| 8.3                                               | Summary on non-linear control .....                       | 247 |

| <b>Chapter 9 – Pulse Referenced Control</b> ..... | 249                                                       |     |

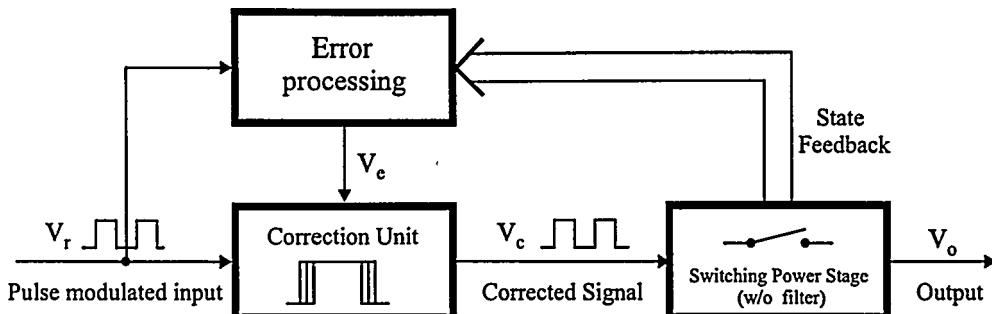

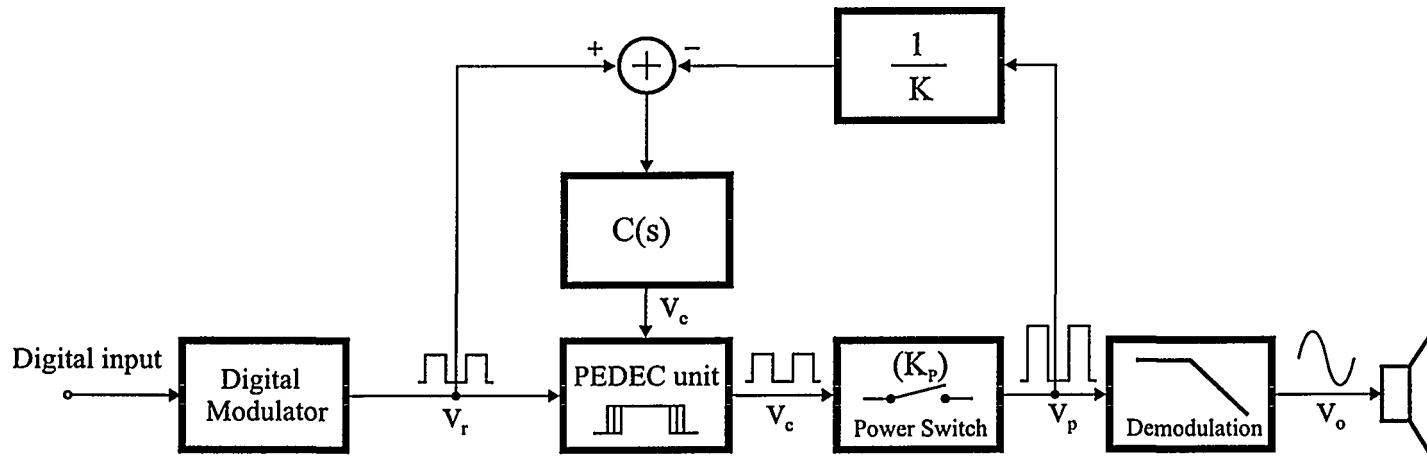

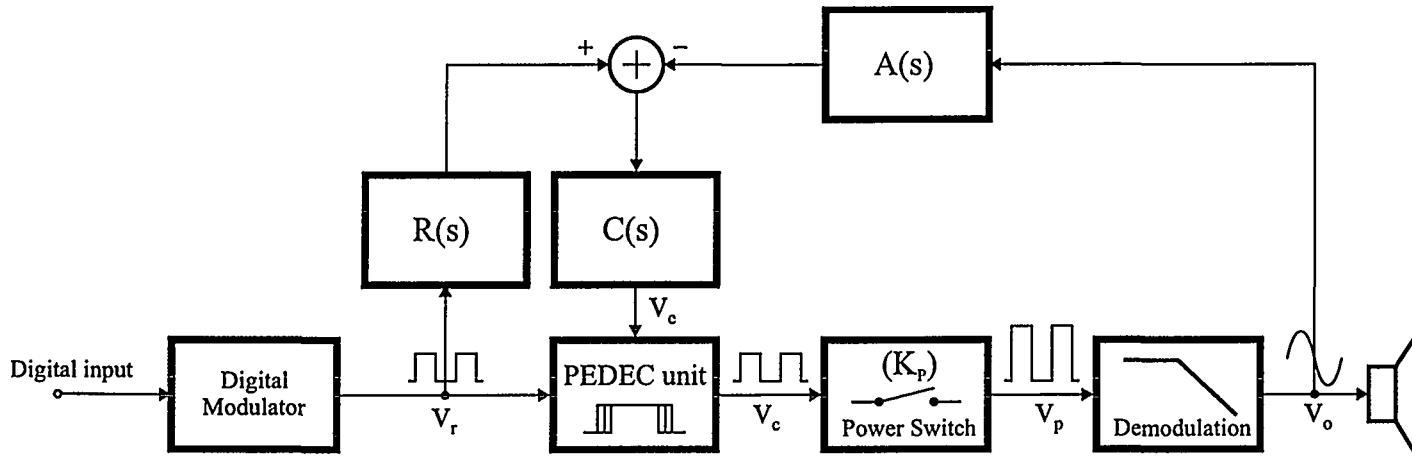

| 9.1                                               | Fundamental considerations.....                           | 250 |

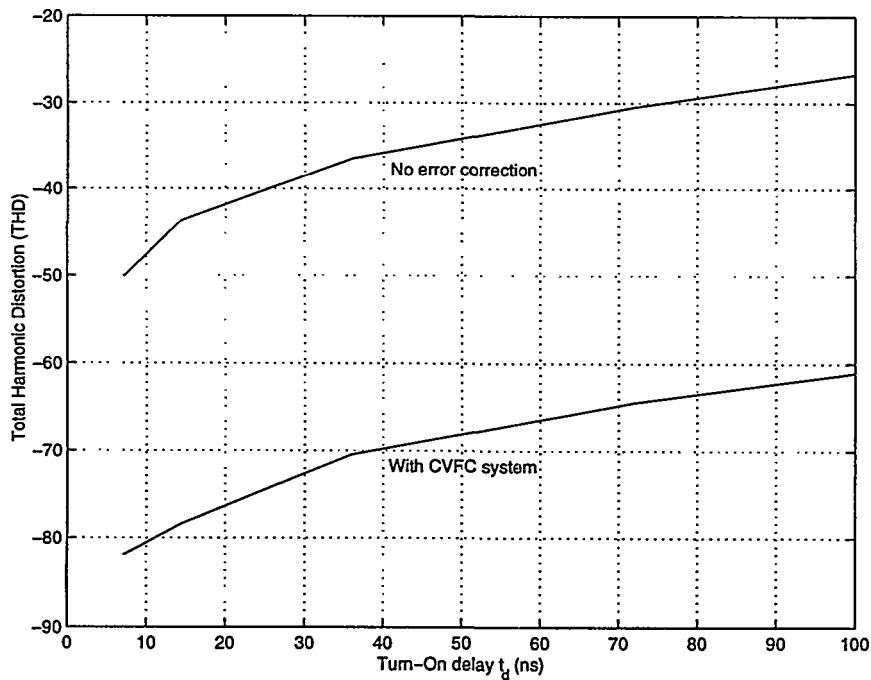

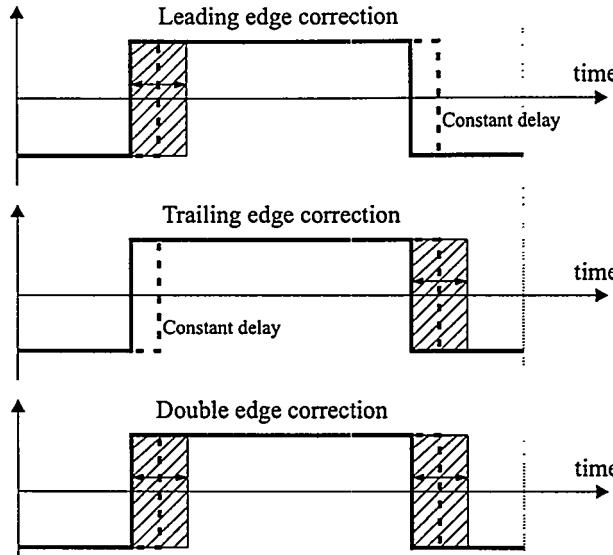

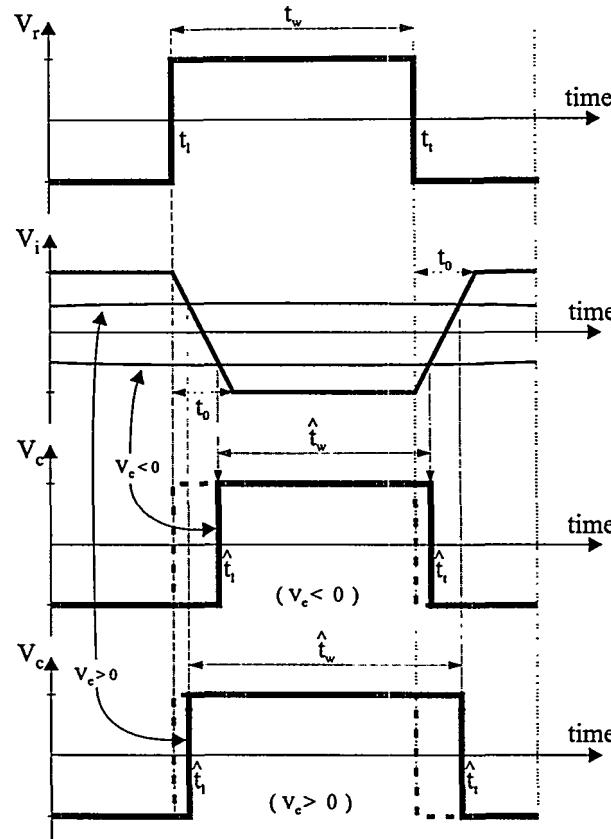

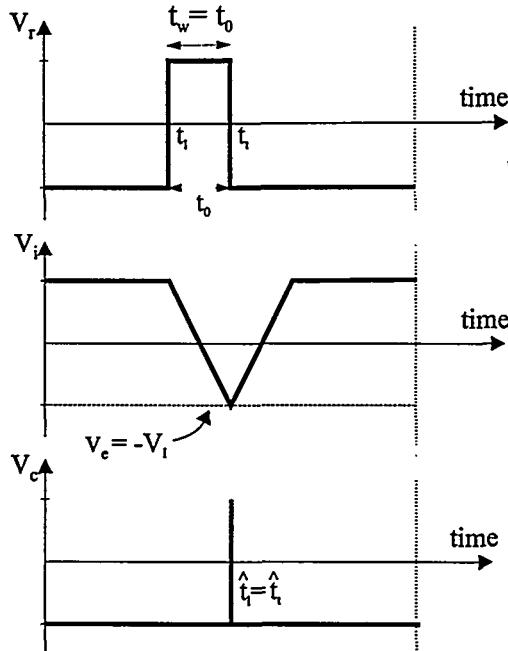

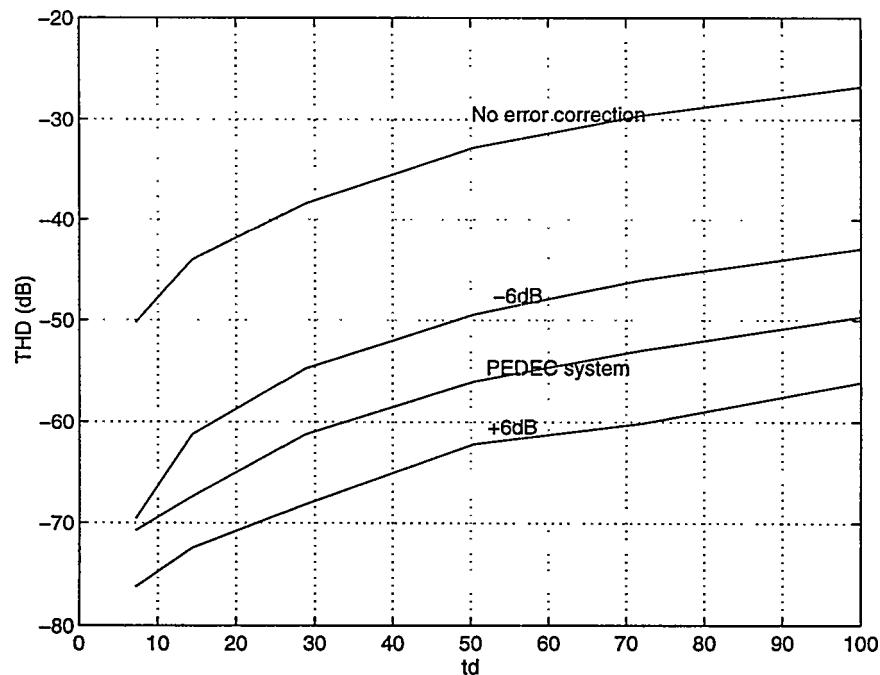

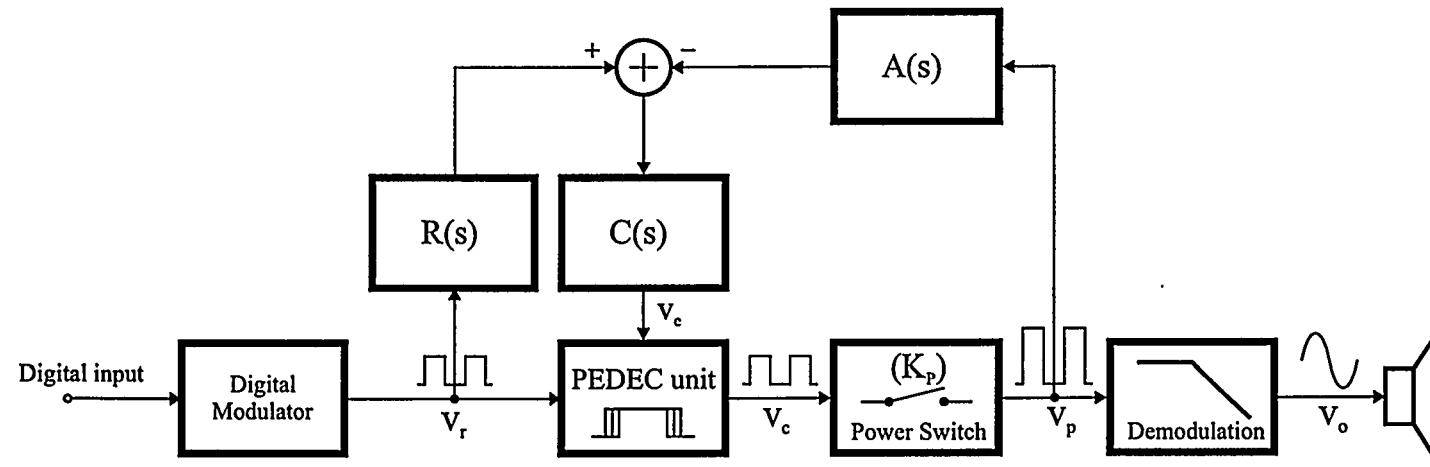

| 9.2                                               | Pulse Edge Delay Error Correction (PEDEC) .....           | 251 |

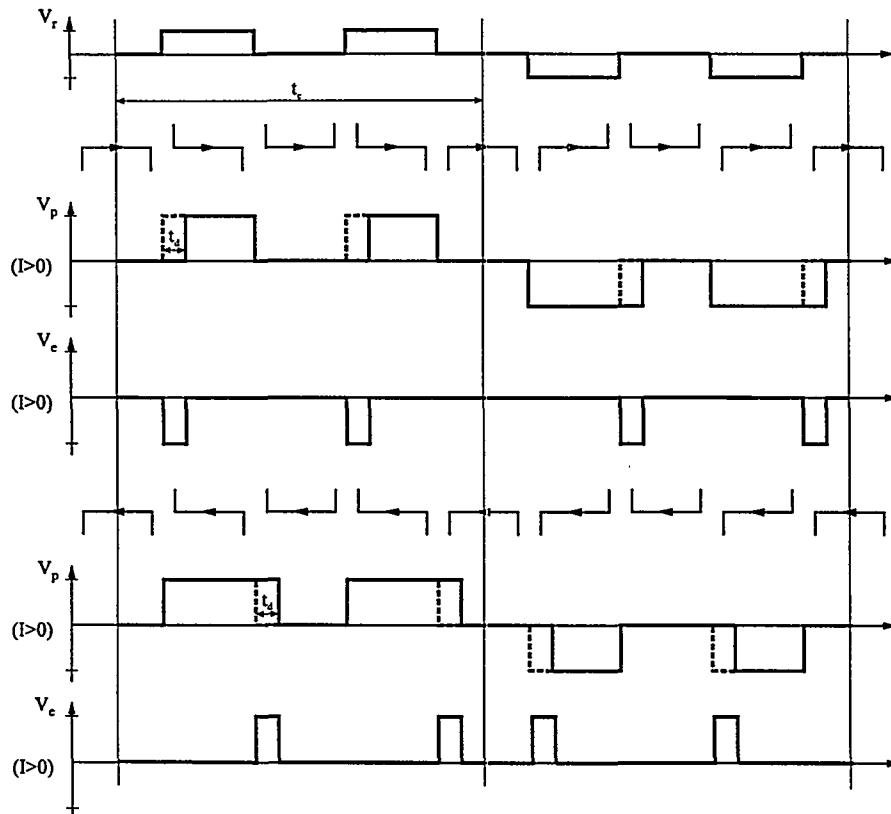

| 9.2.1                                             | Control function specification.....                       | 252 |

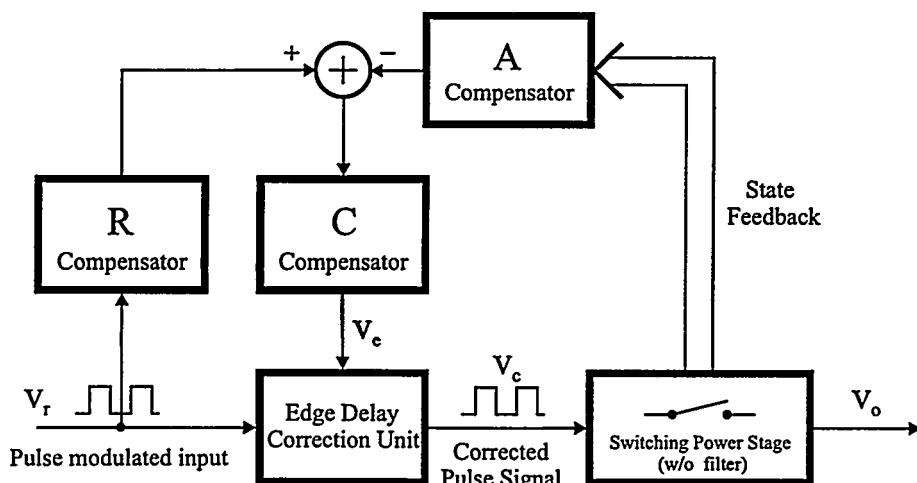

| 9.2.2                                             | Realizing the control function.....                       | 254 |

| 9.3                                               | Applying PEDEC to Digital PMA systems .....               | 256 |

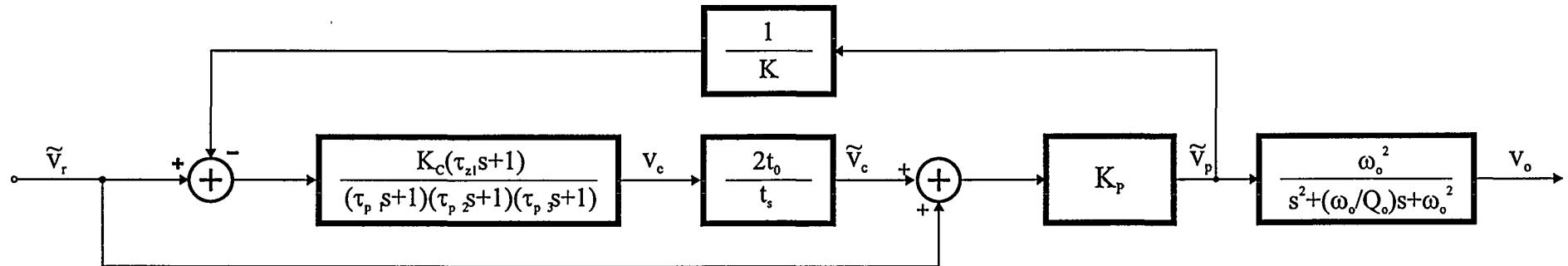

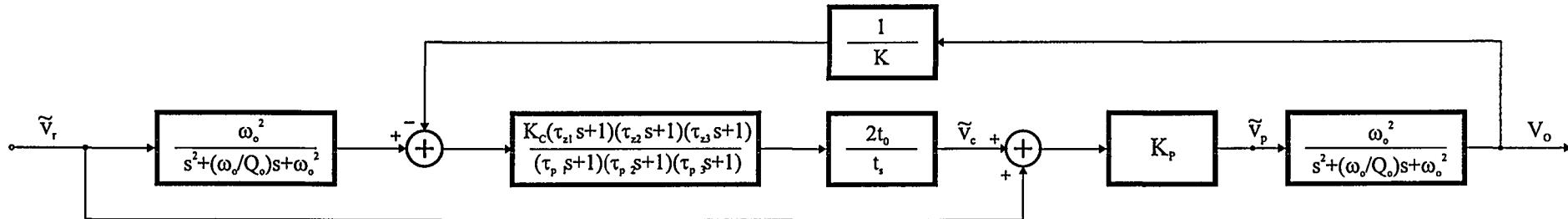

| 9.3.1                                             | Defining control structures .....                         | 256 |

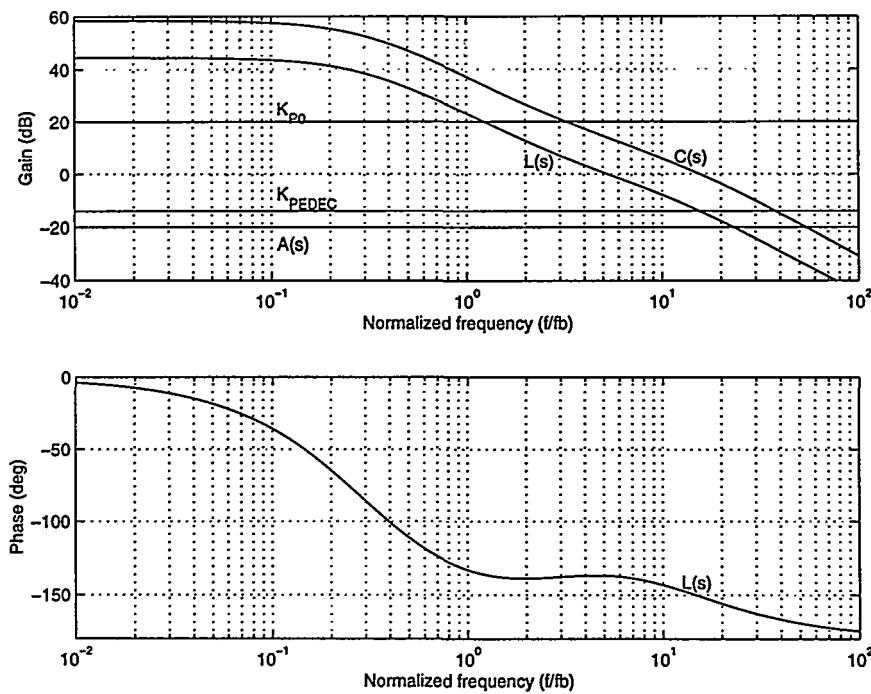

| 9.4                                               | PEDEC VFC1 .....                                          | 257 |

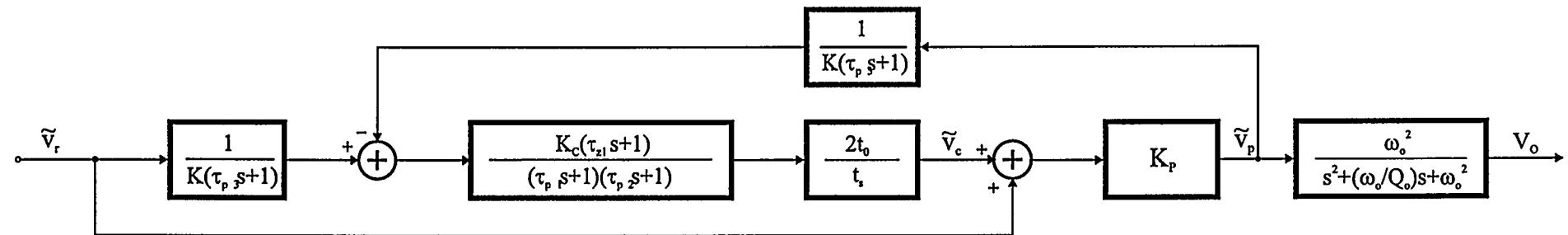

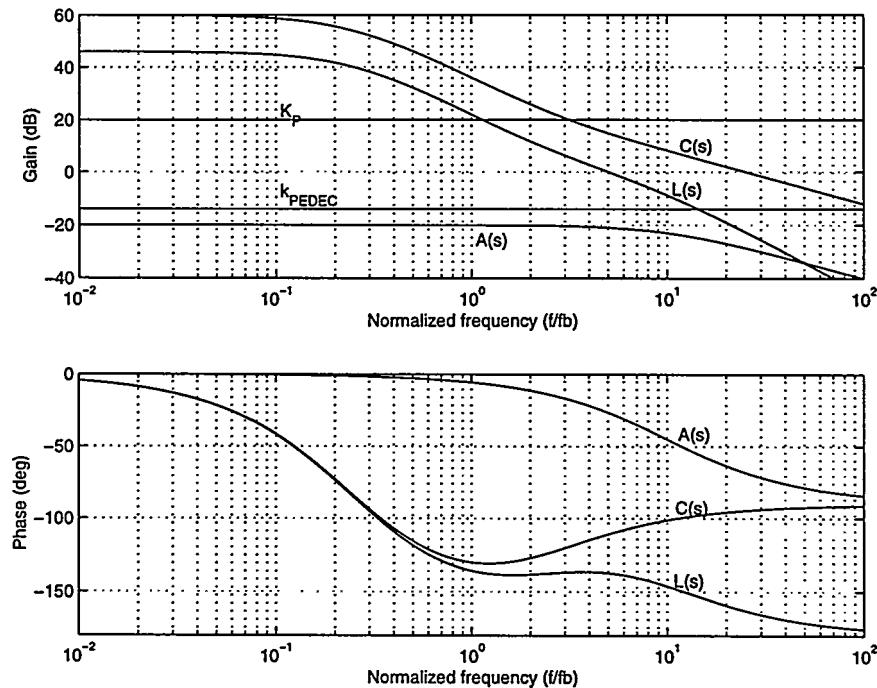

| 9.4.1                                             | Analysis.....                                             | 257 |

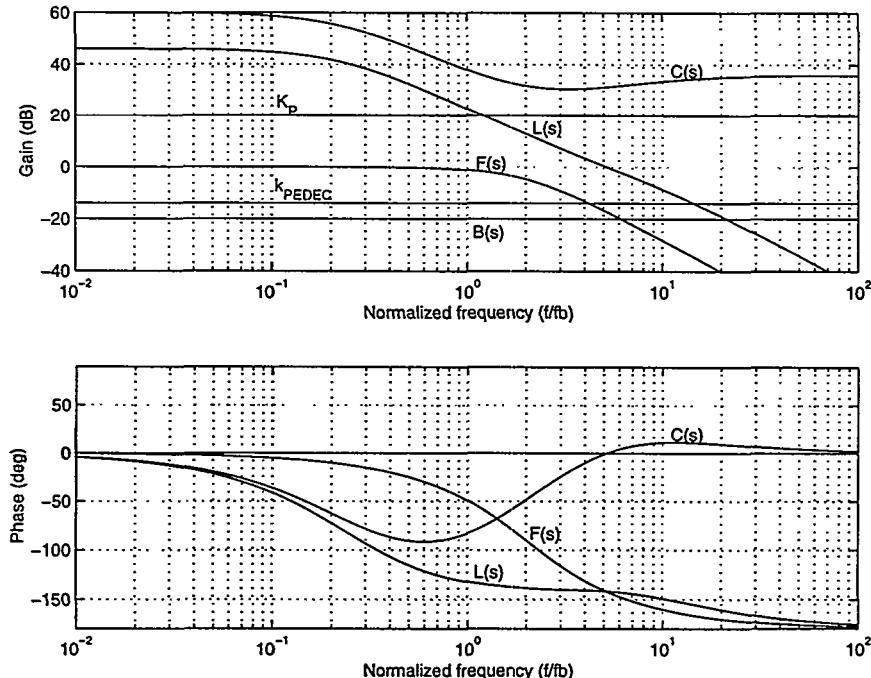

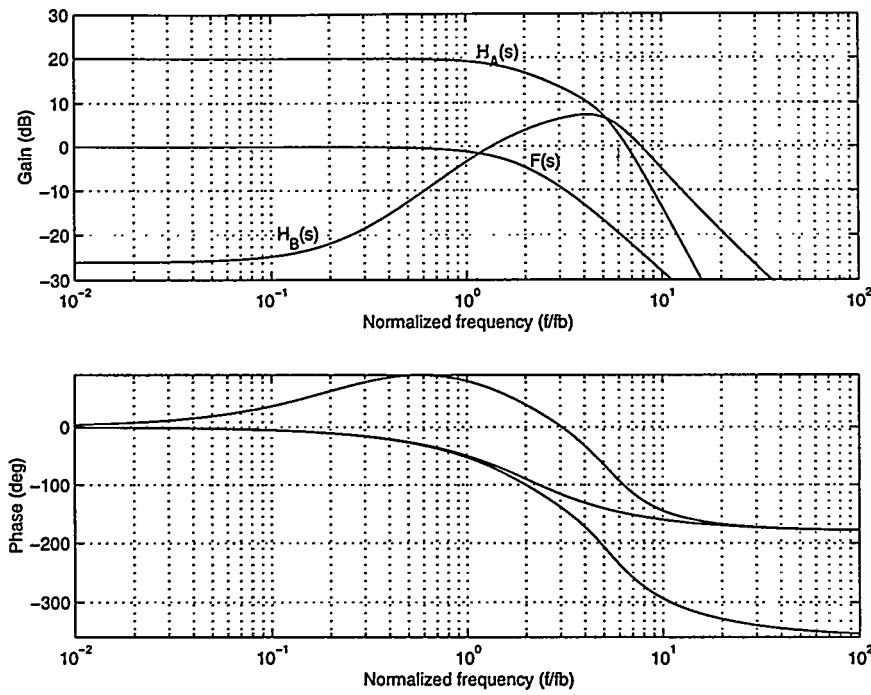

| 9.4.2                                             | PEDEC VFC1 loop shaping.....                              | 259 |

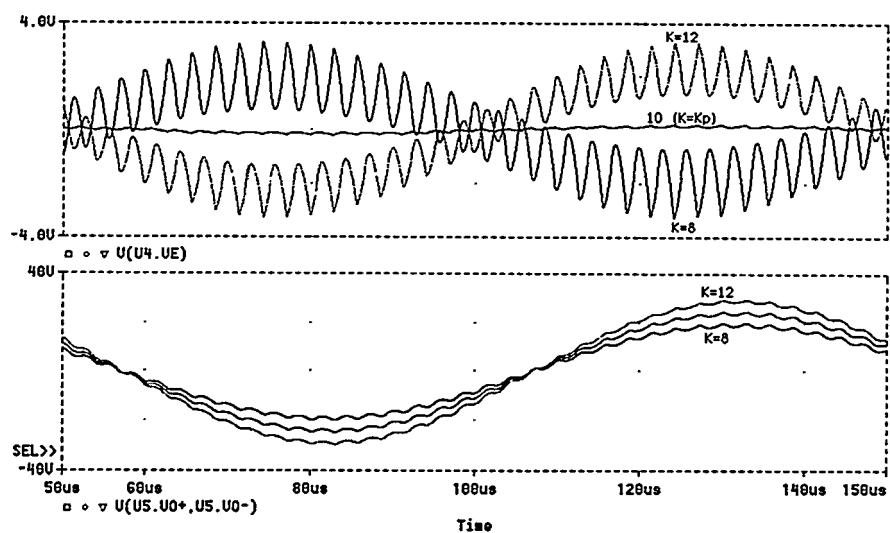

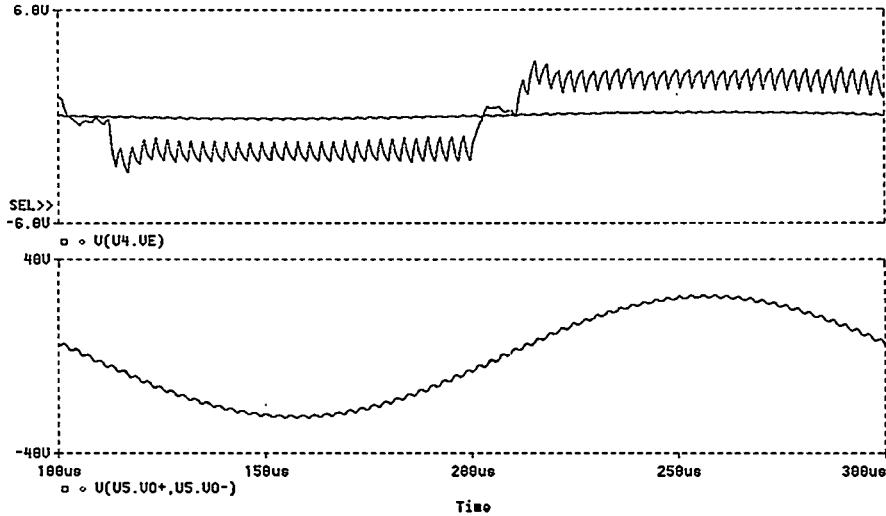

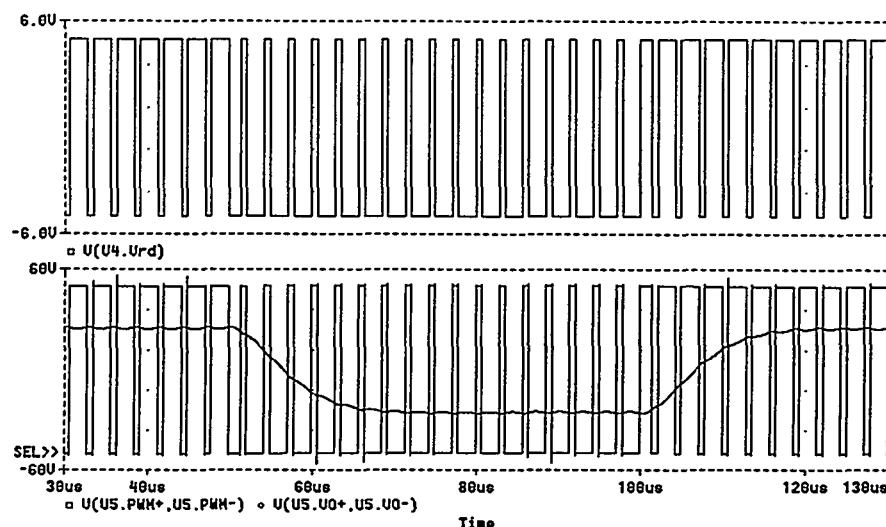

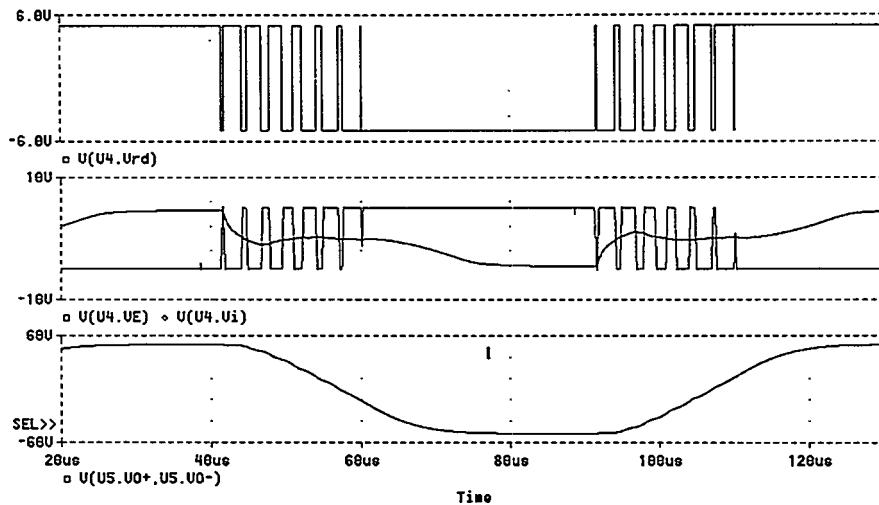

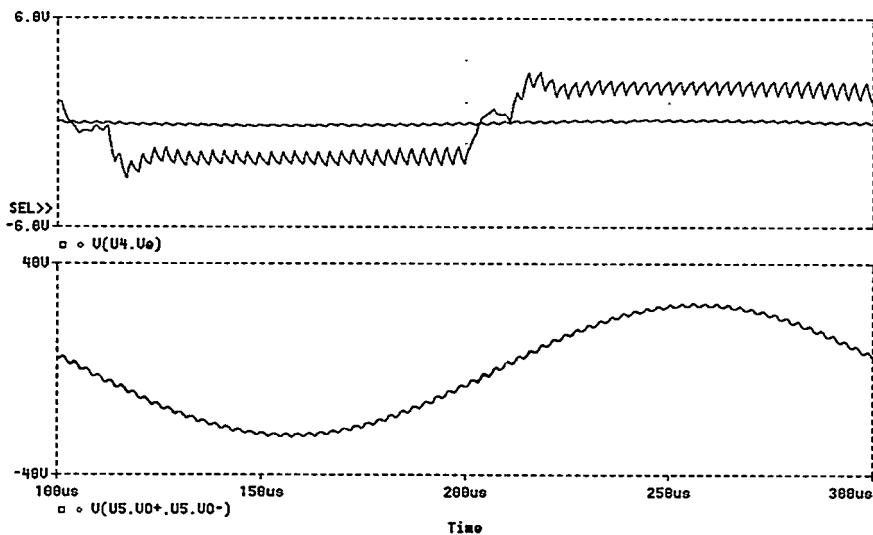

| 9.4.3                                             | Case example .....                                        | 260 |

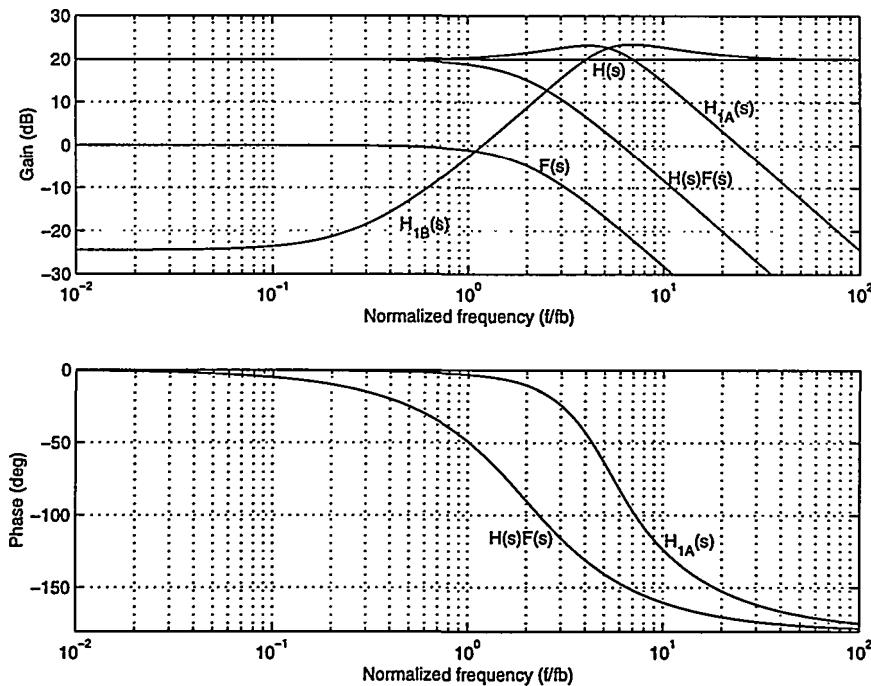

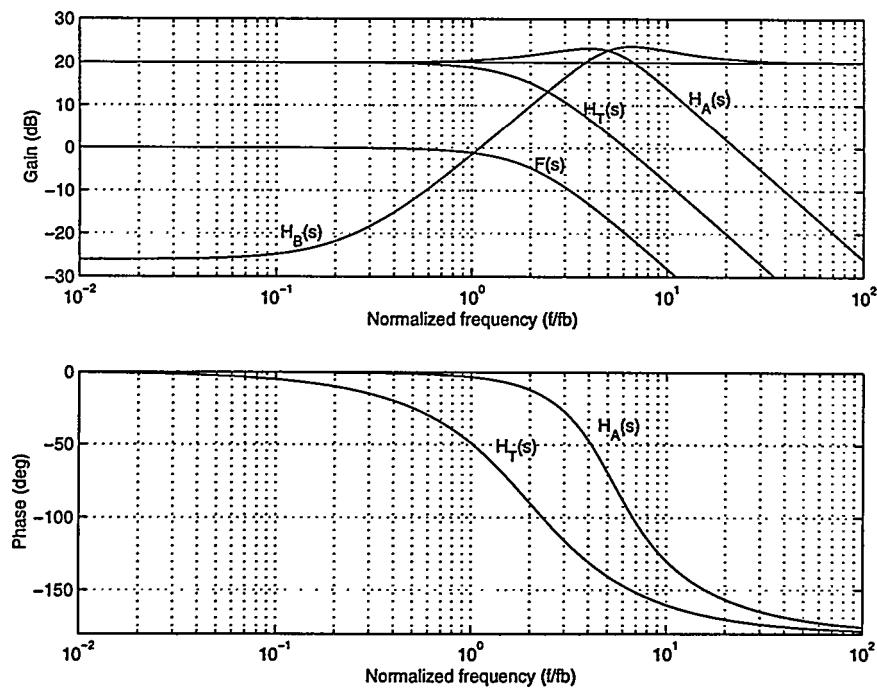

| 9.5                                               | PEDEC VFC2 .....                                          | 268 |

| 9.5.1                                             | Analysis.....                                             | 268 |

| 9.5.2                                             | PEDEC VFC2 loop shaping.....                              | 270 |

| 9.5.3                                             | Case example .....                                        | 270 |

| 9.6                                               | PEDEC VFC3 .....                                          | 273 |

| 9.6.1                                             | Analysis.....                                             | 273 |

| 9.6.2                                             | PEDEC VFC3 Loop shaping .....                             | 273 |

| 9.6.3                                             | Case example .....                                        | 274 |

| 9.7                                               | Extensions .....                                          | 275 |

| 9.8                                               | Summary .....                                             | 277 |

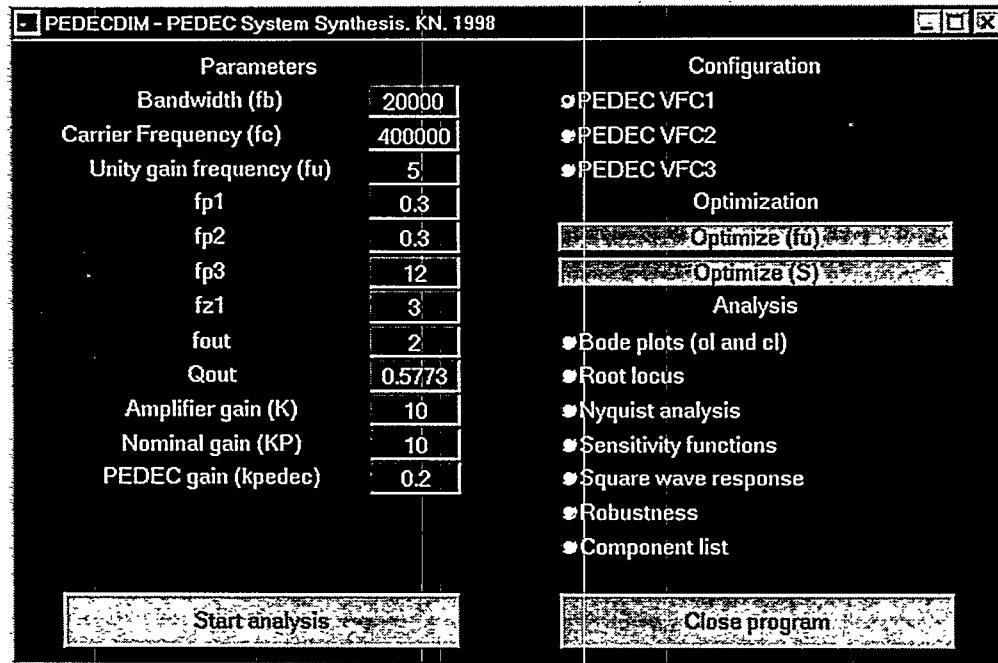

| 9.8.1                                             | PEDECIM - GUI based PEDEC design toolbox for MATLAB ..... | 278 |

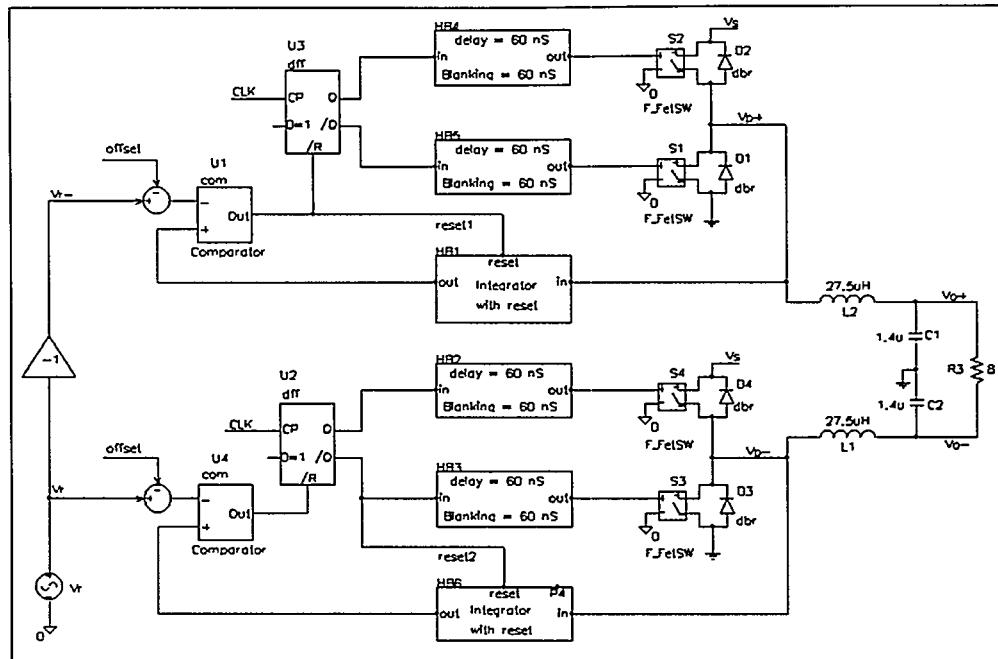

| <b>Chapter 10 – Practical Evaluation</b> .....    | 279                                                       |     |

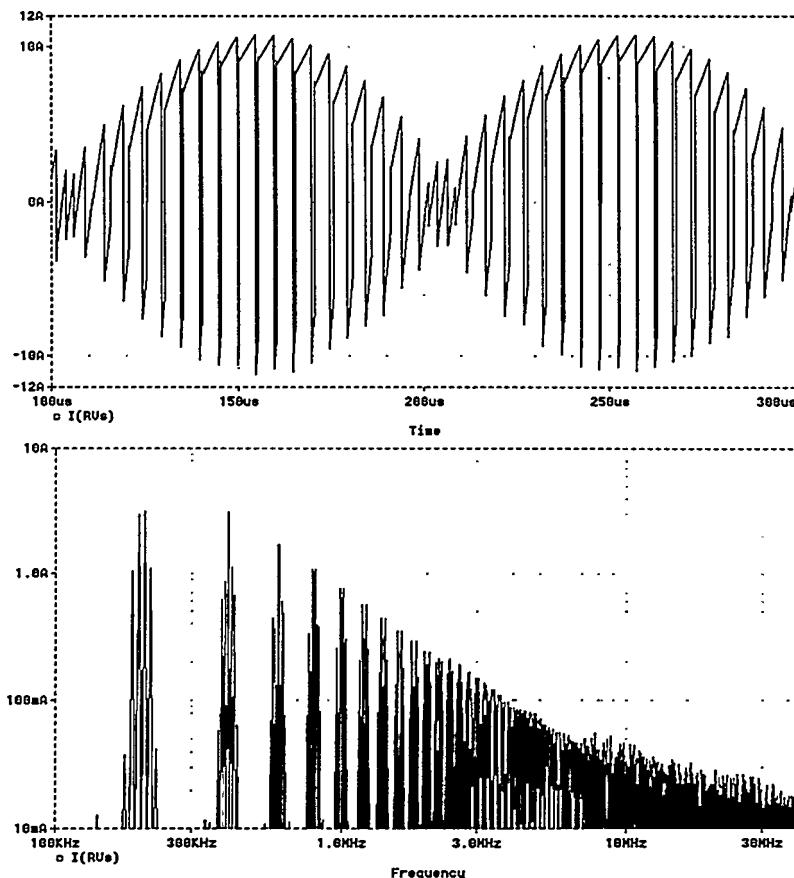

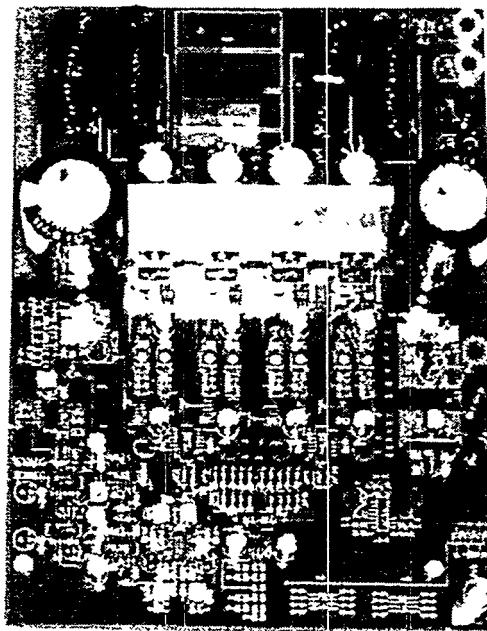

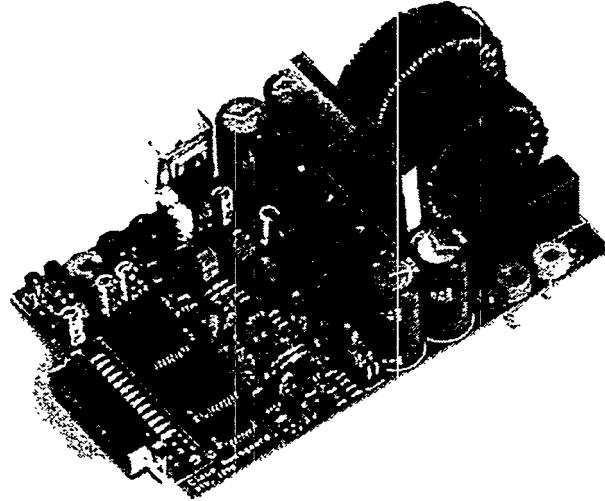

| 10.1                                              | Power Stage Implementation .....                          | 280 |

| 10.1.1                                            | The switching leg building block.....                     | 280 |

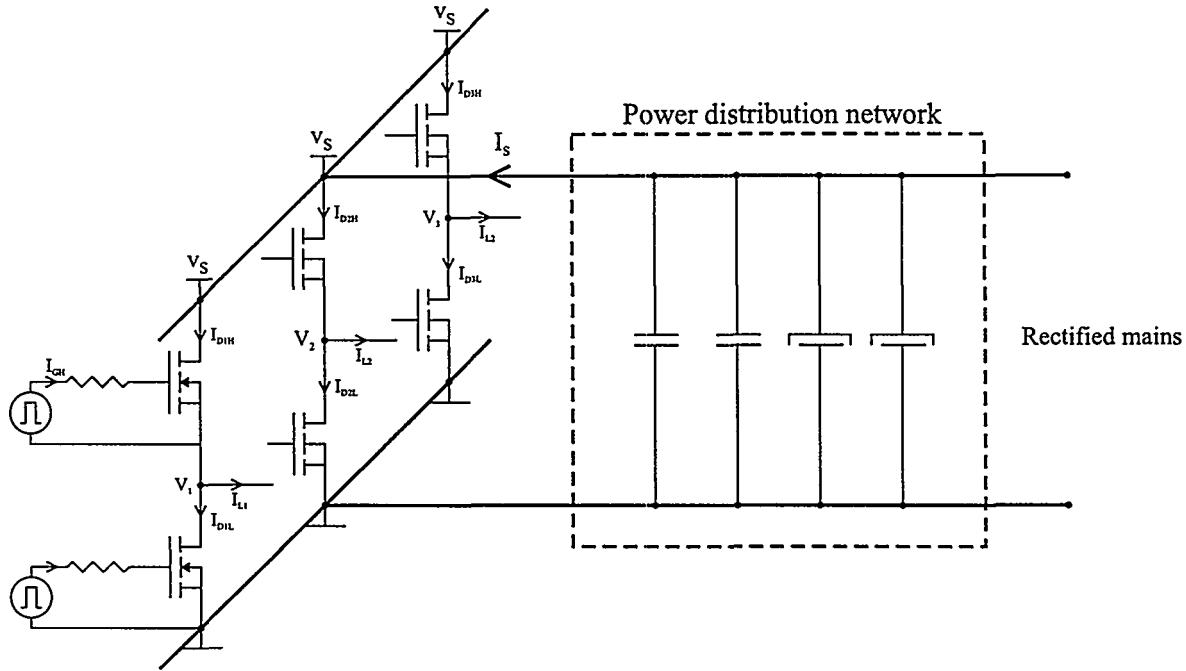

| 10.1.2                                            | Power distribution network considerations.....            | 281 |

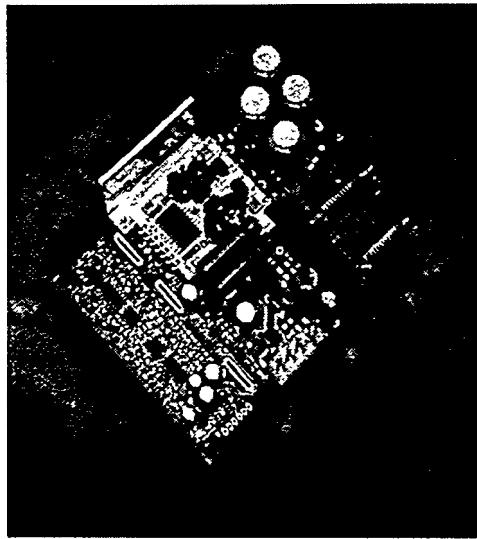

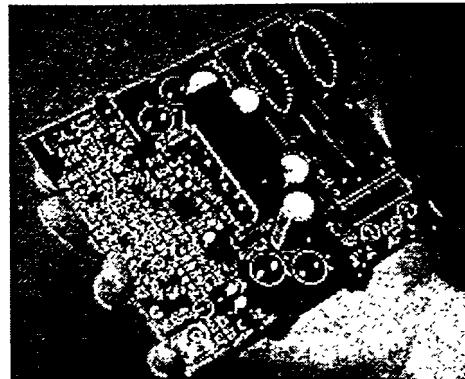

| 10.1.3                                            | Hybrid IC – Optimized power stage realization .....       | 283 |

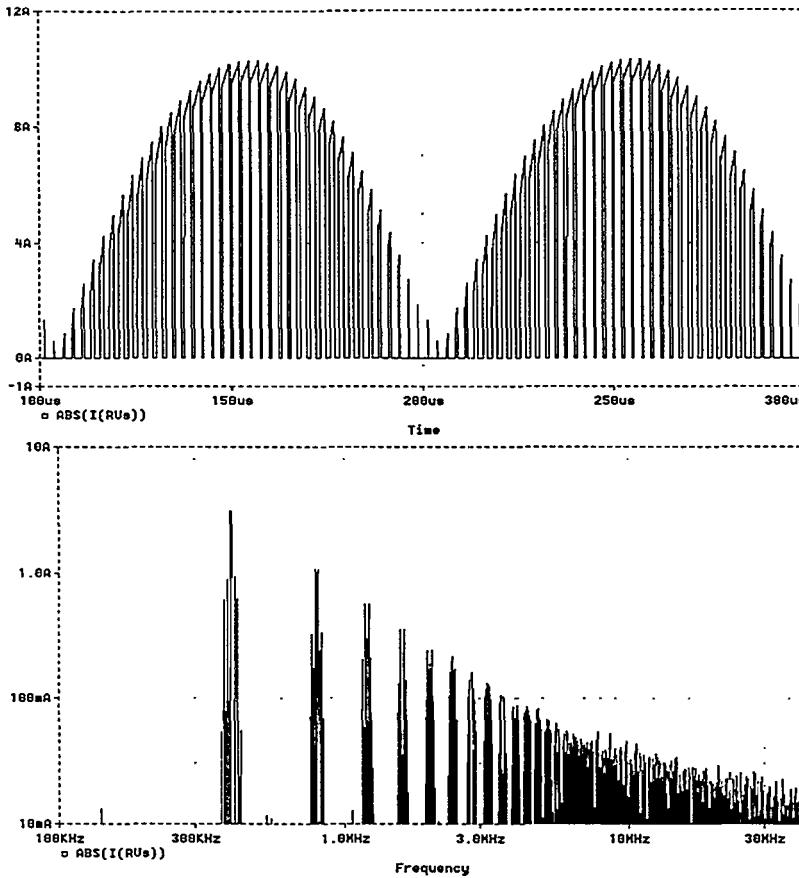

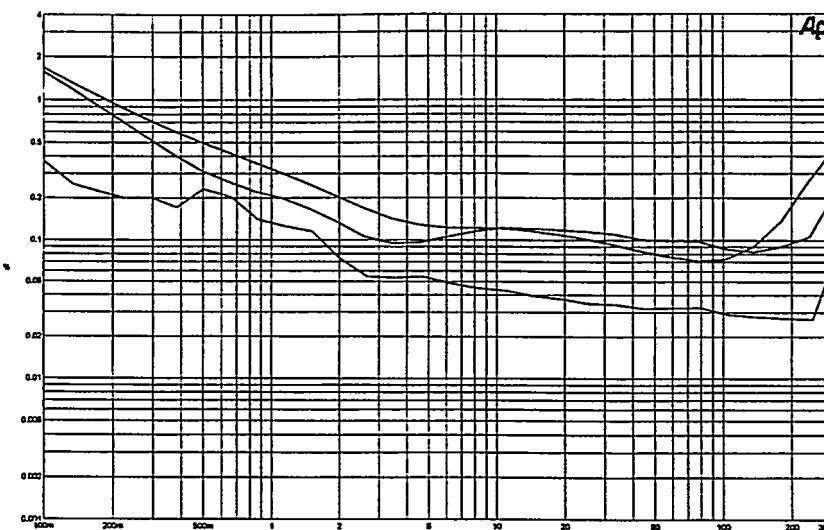

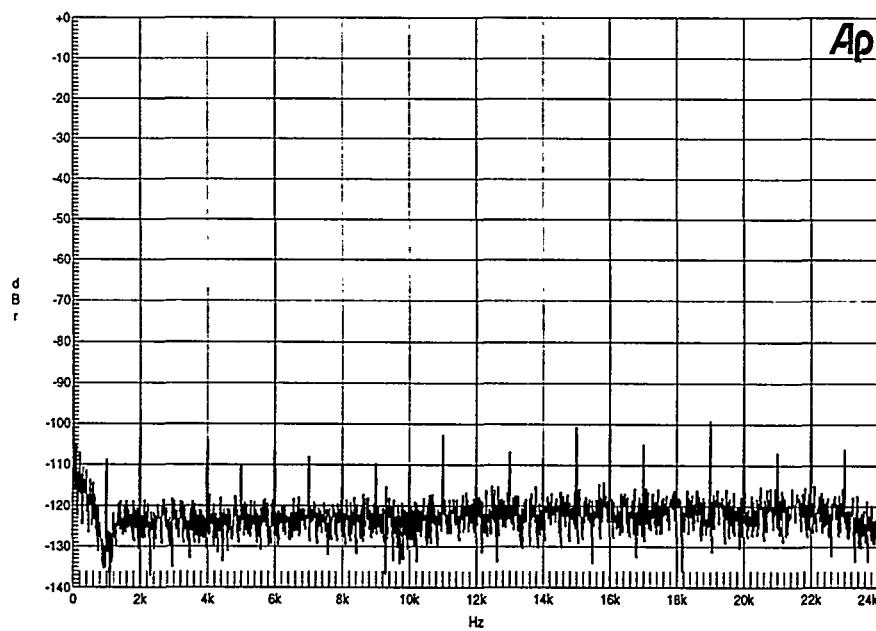

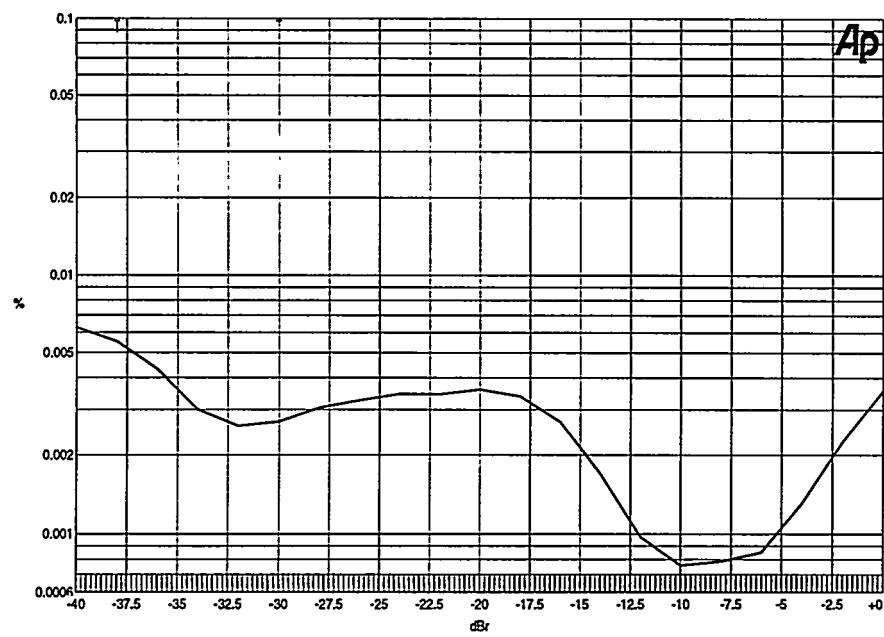

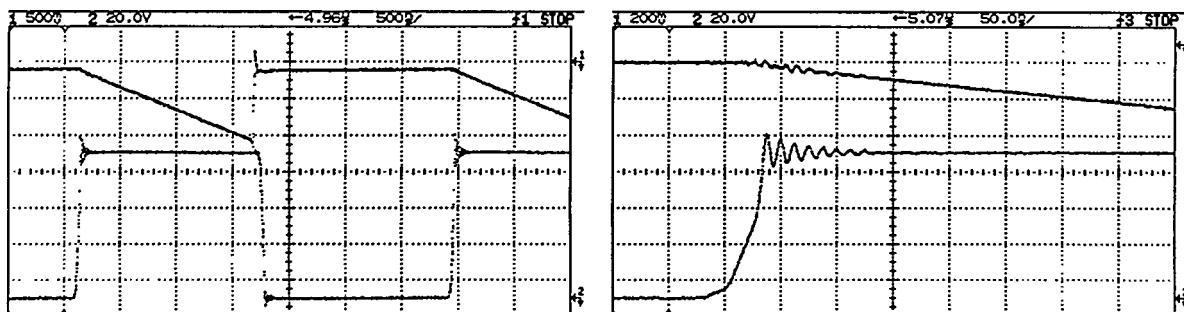

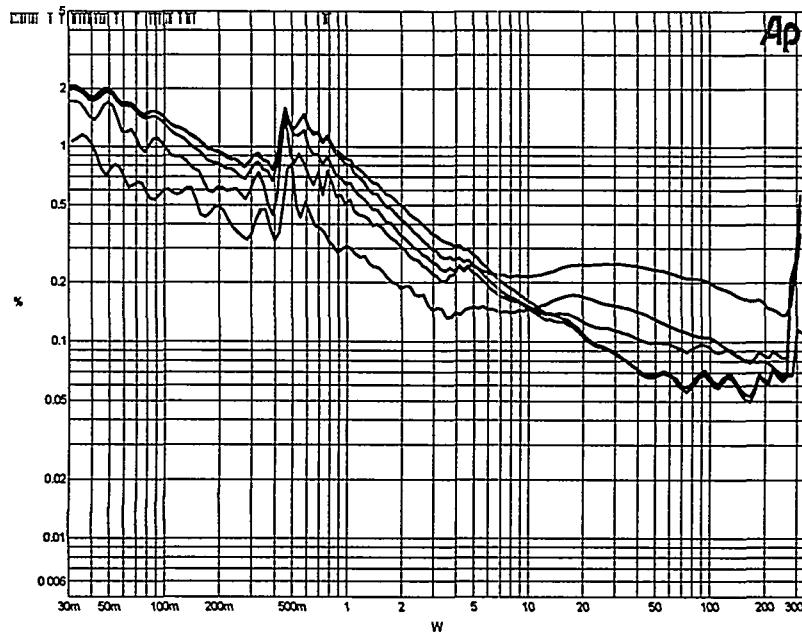

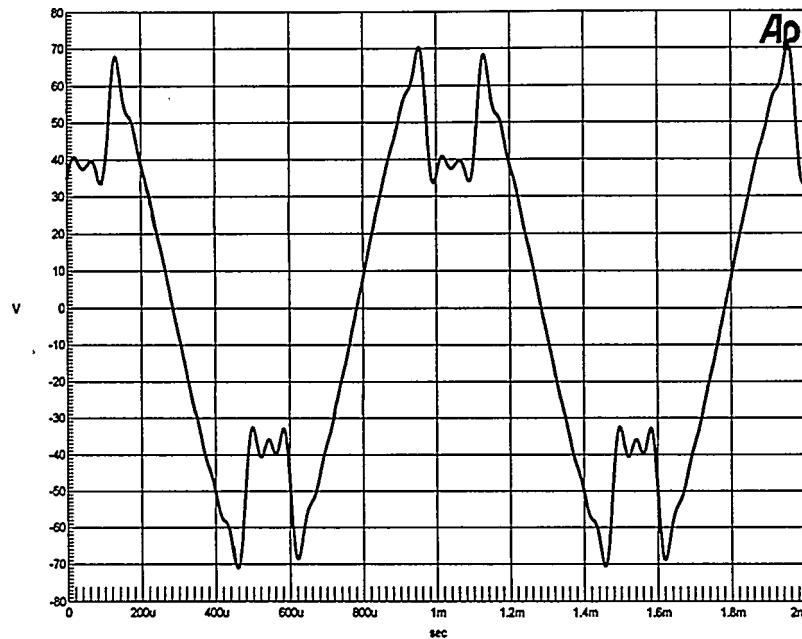

| 10.1.4                                            | Power stage performance.....                              | 284 |

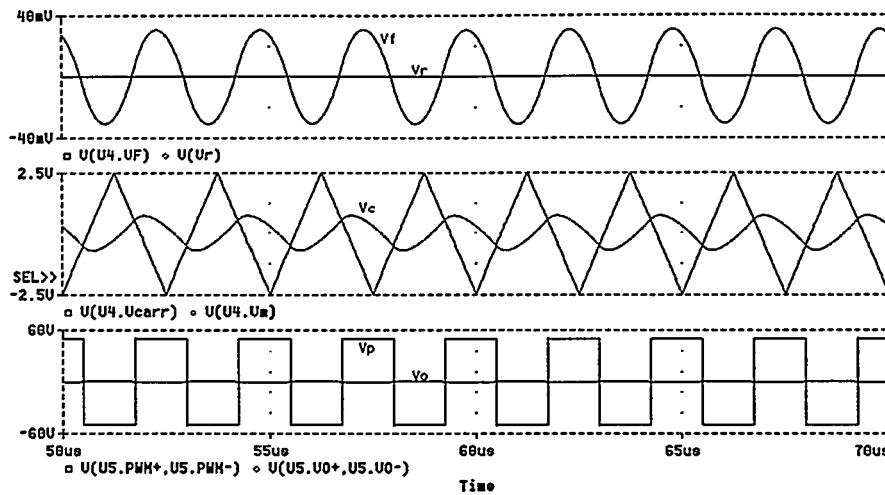

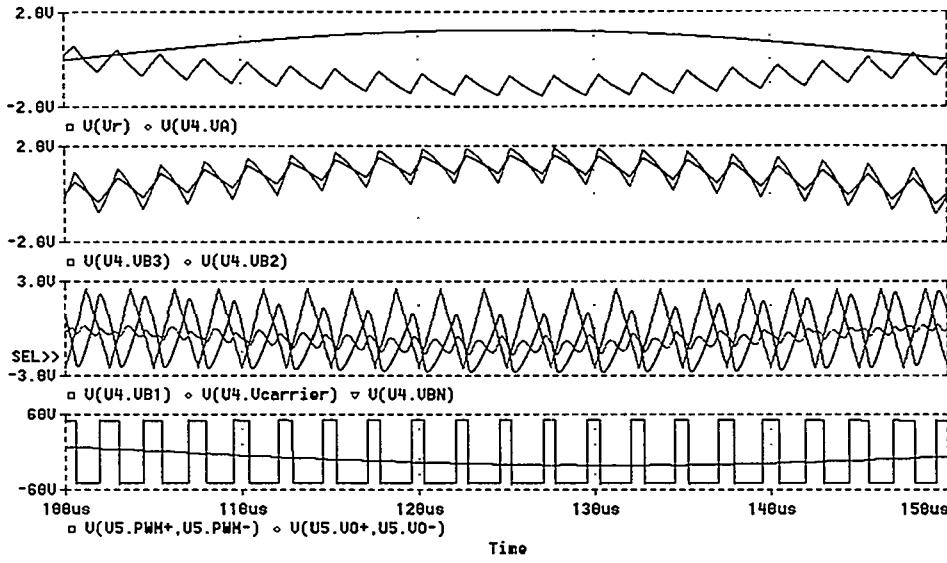

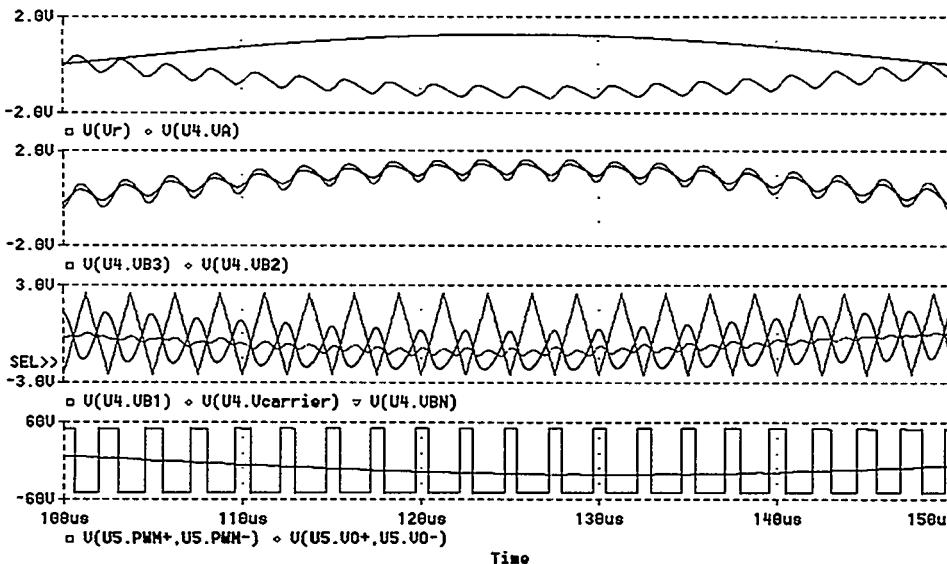

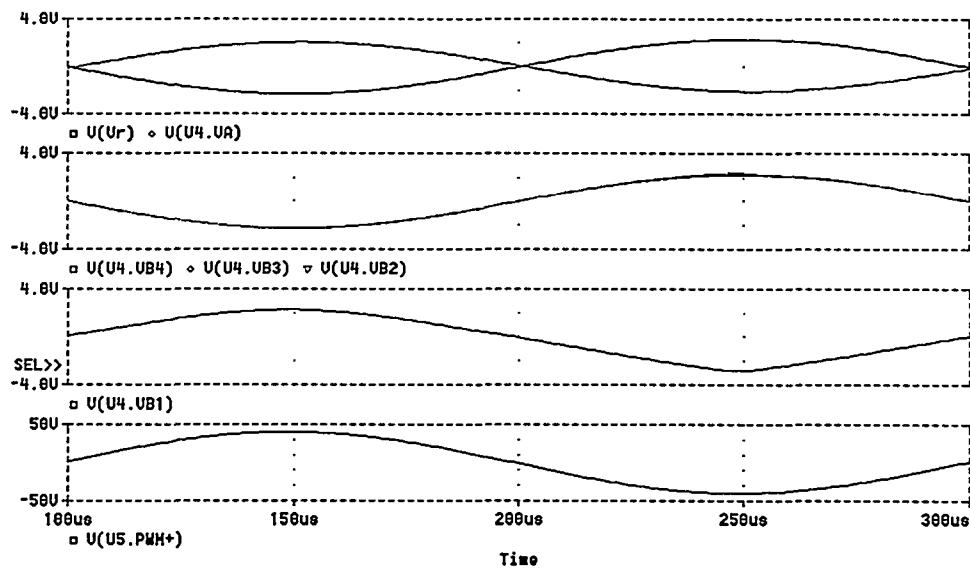

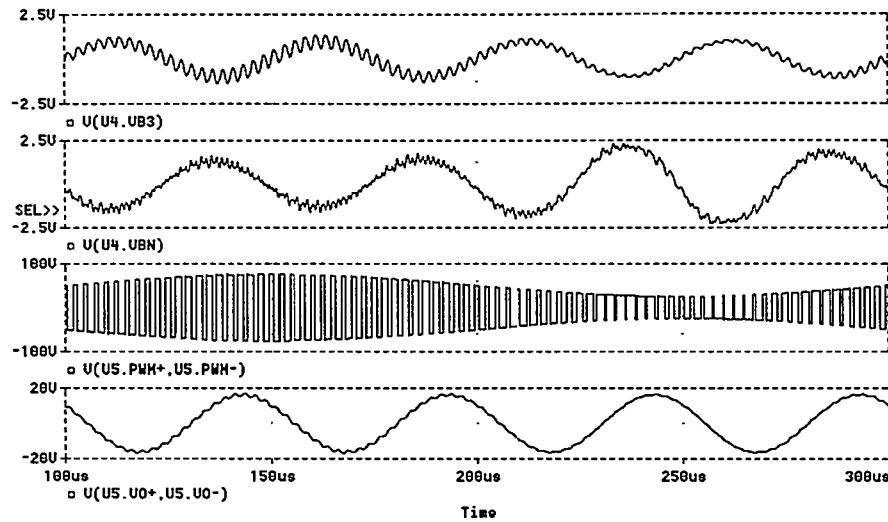

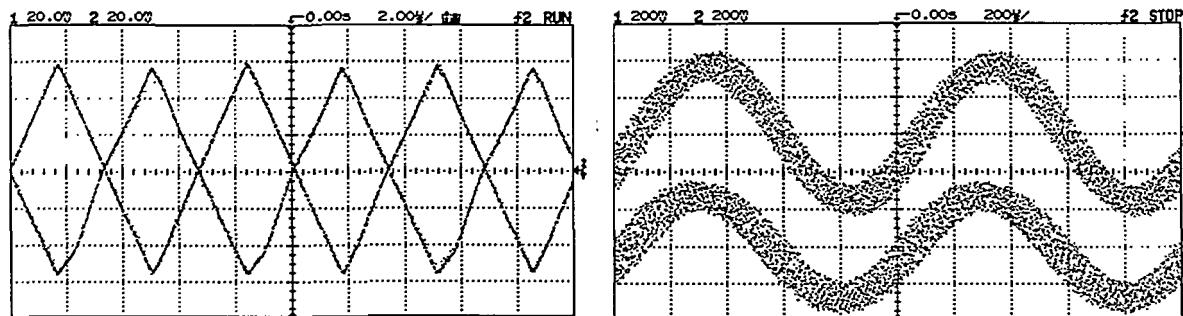

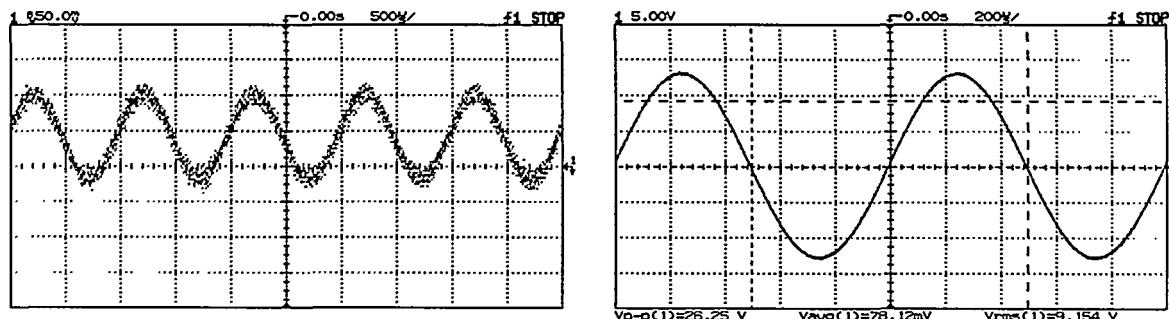

| 10.2                                              | PSCPWM Evaluation .....                                   | 287 |

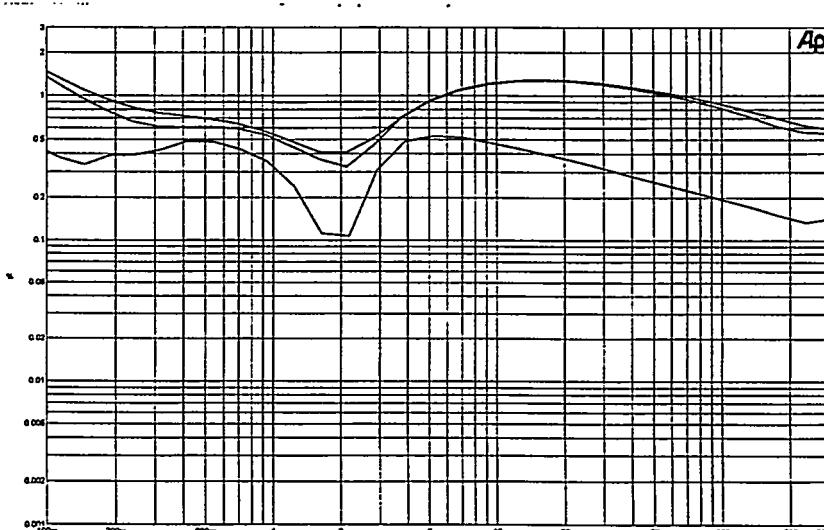

| 10.3                                              | VFC1/VFC2 evaluation .....                                | 290 |

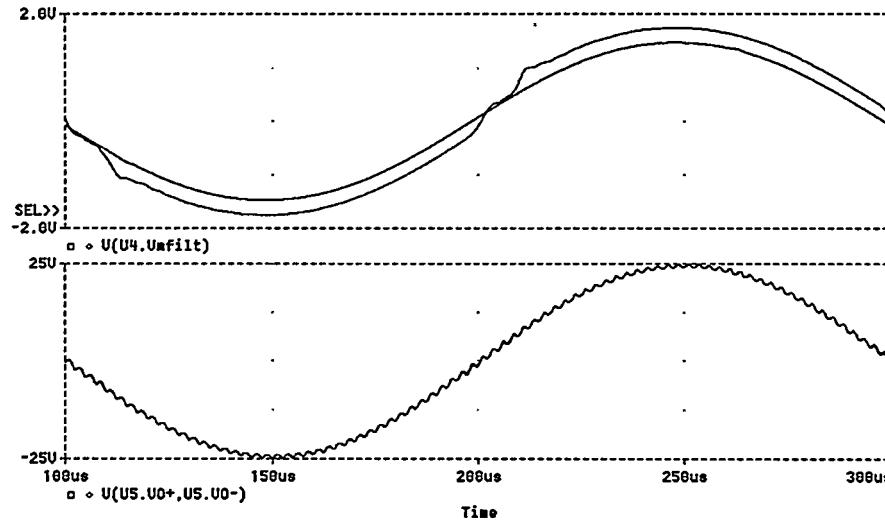

| 10.4                                              | CVFC Evaluation.....                                      | 292 |

|                                                  |                                          |            |

|--------------------------------------------------|------------------------------------------|------------|

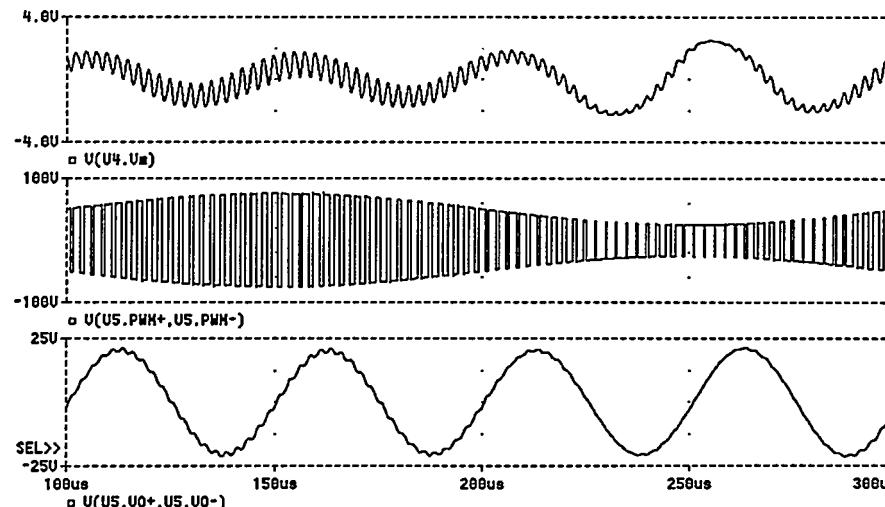

| 10.5                                             | MECC evaluation.....                     | 294        |

| 10.6                                             | Enhanced Non-linear Control (TOCC) ..... | 298        |

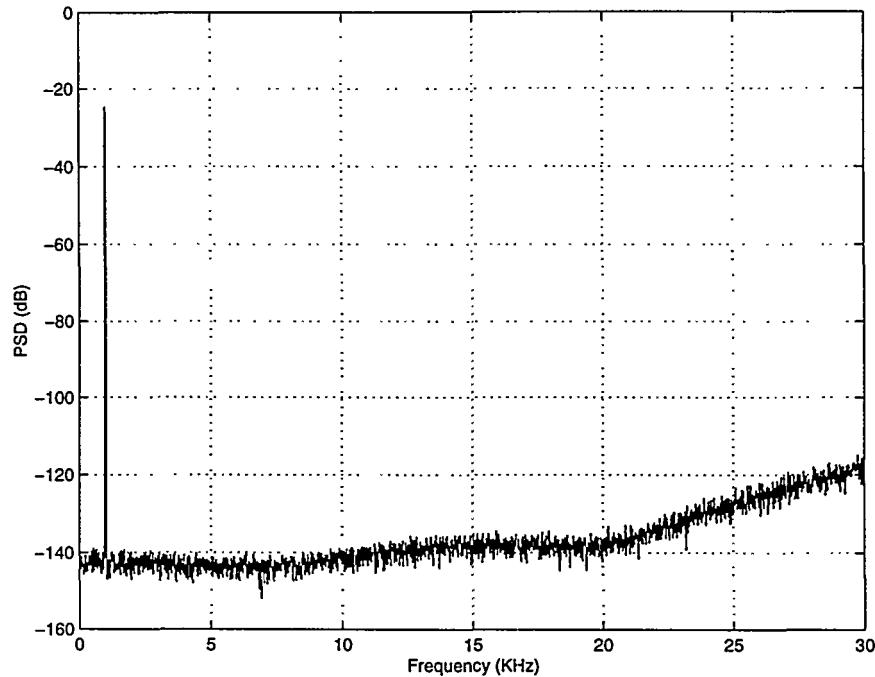

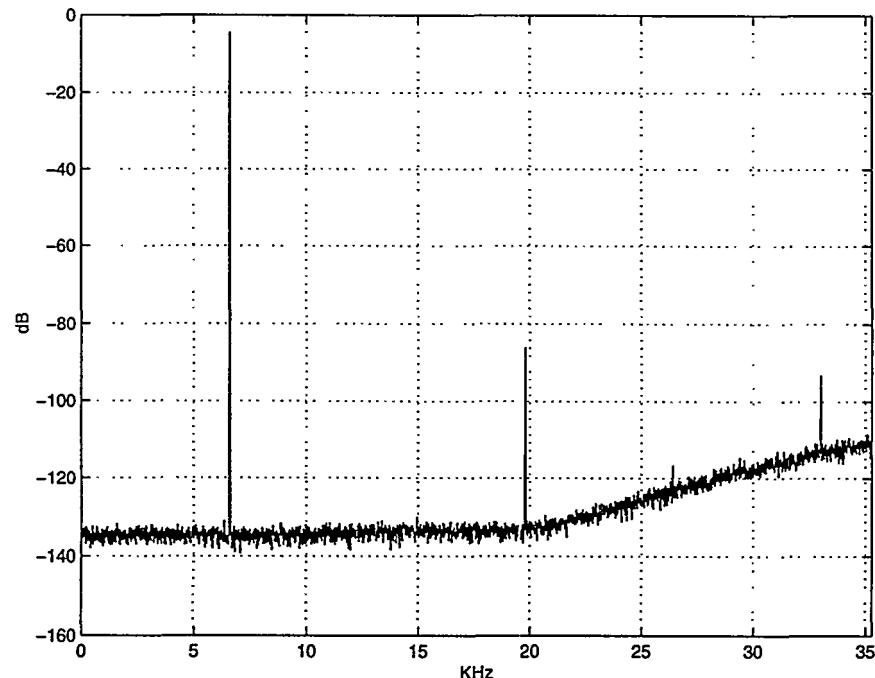

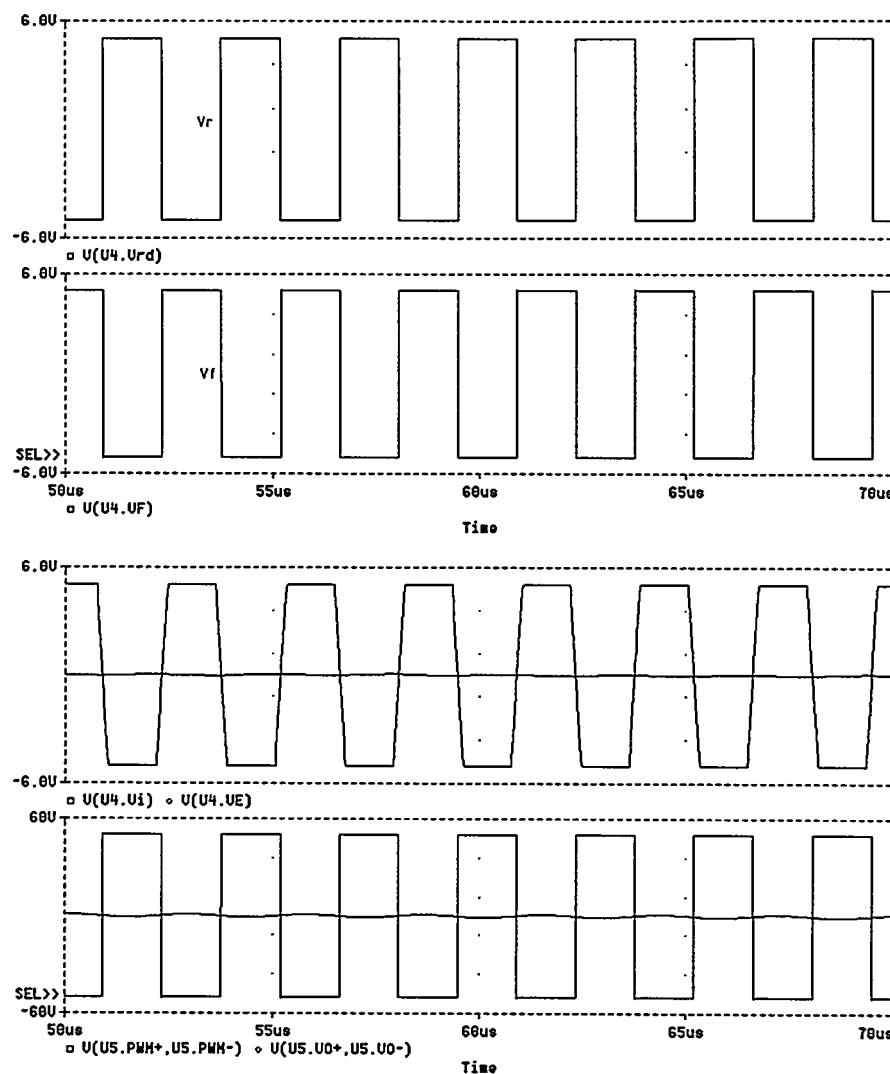

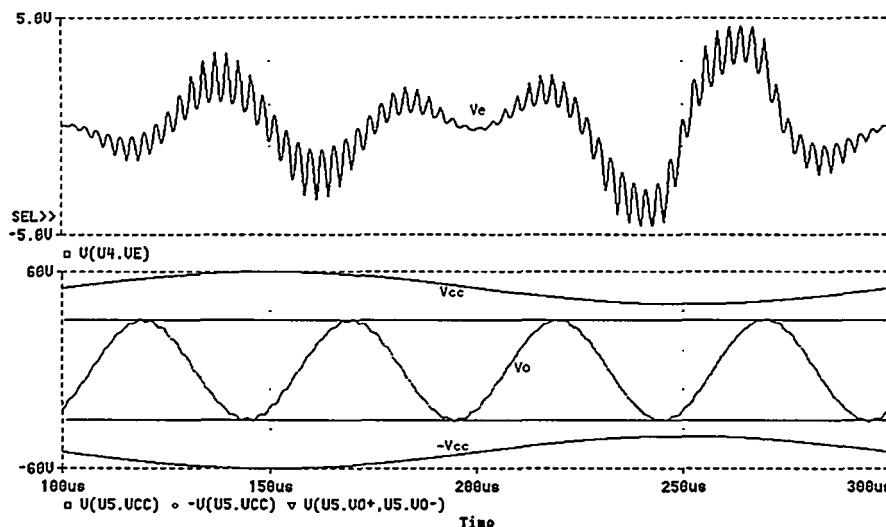

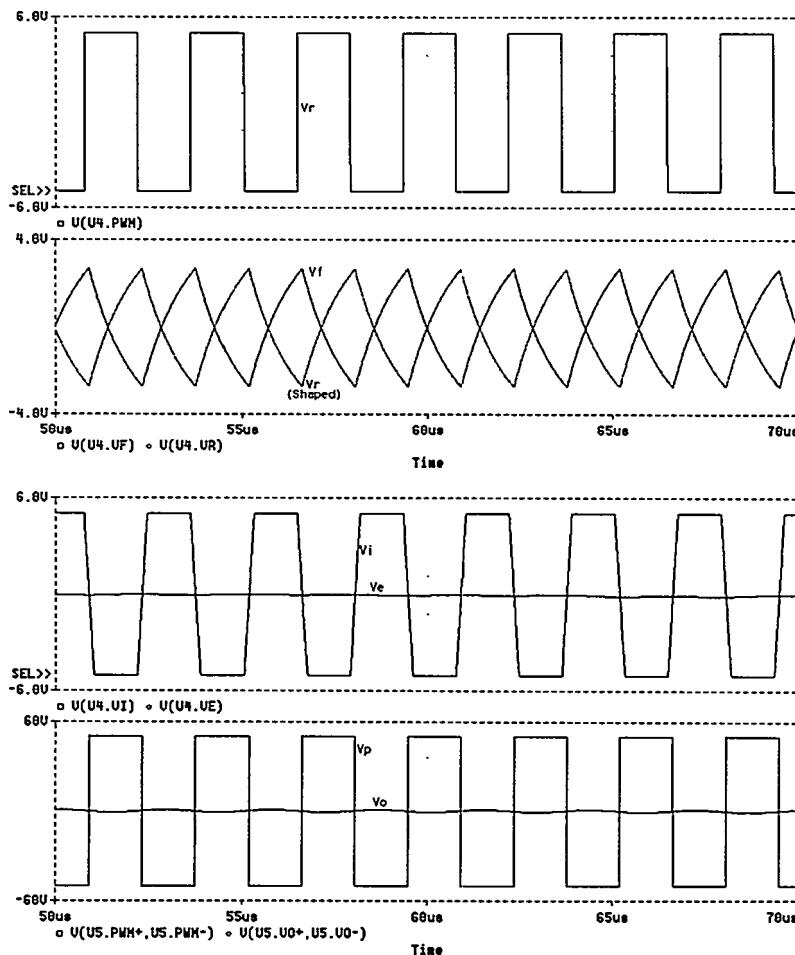

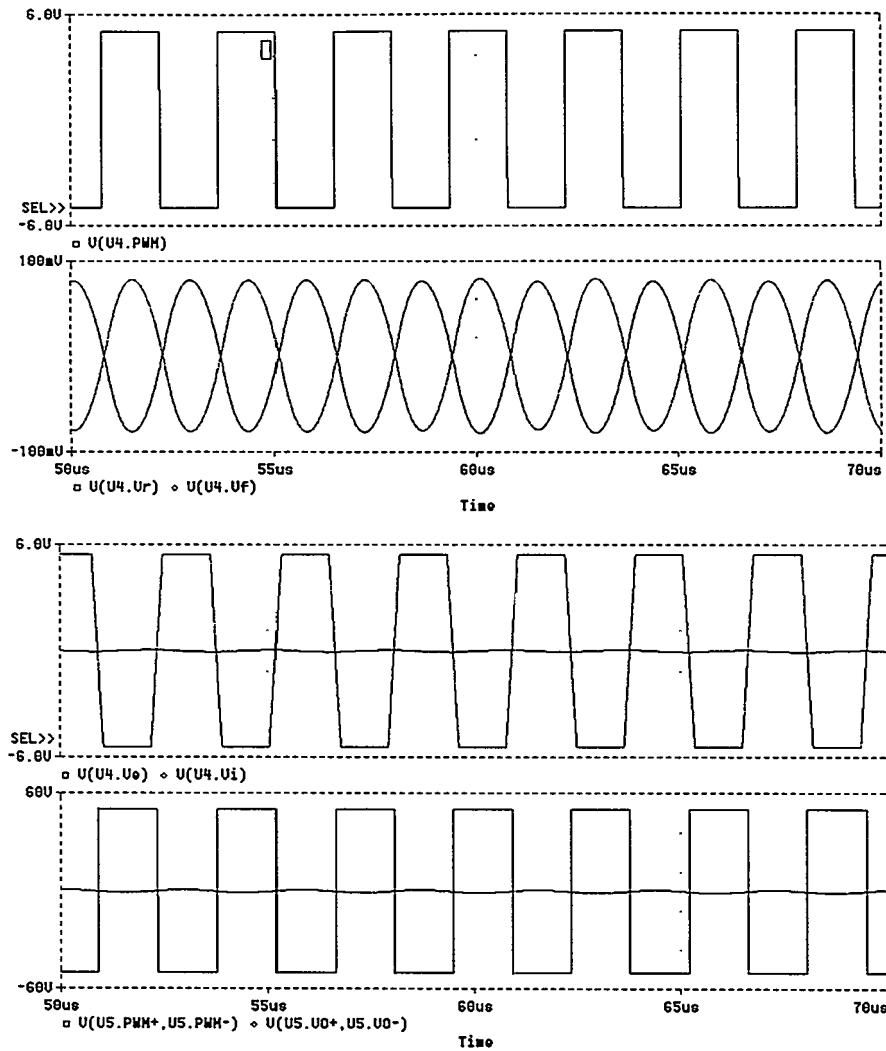

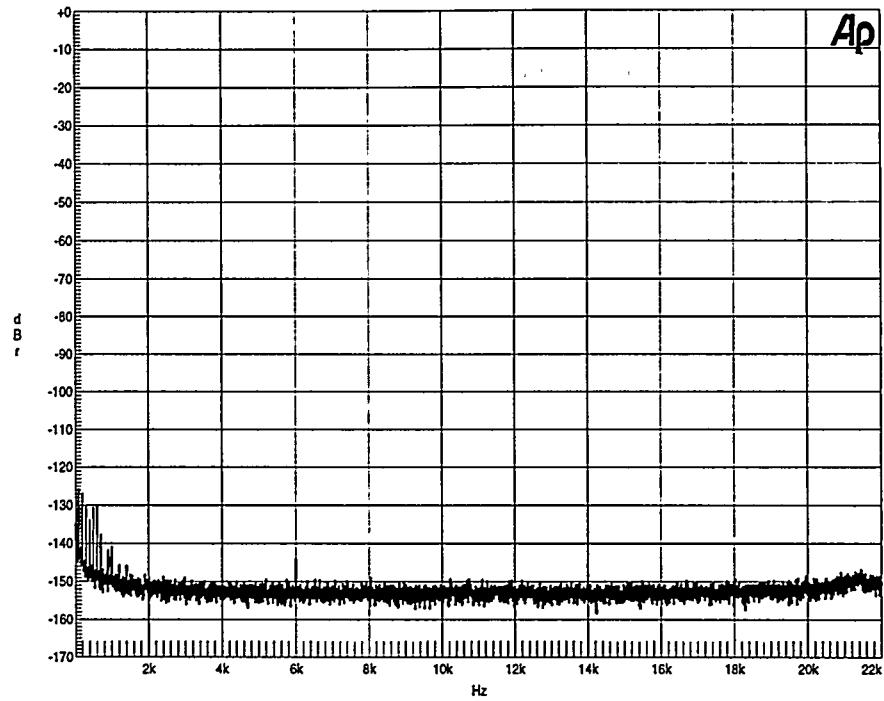

| 10.7                                             | PEDEC based Digital PMA .....            | 301        |

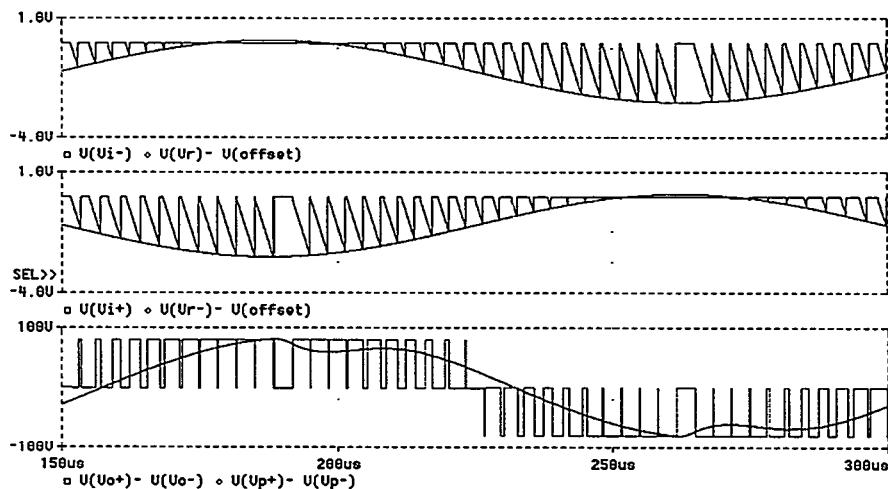

| 10.7.1                                           | Open loop performance.....               | 302        |

| 10.8                                             | Summary .....                            | 306        |

| <b>Chapter 11 – Summary and Conclusions.....</b> |                                          | <b>307</b> |

| <b>Bibliography .....</b>                        |                                          | <b>311</b> |

# Preface

This thesis is submitted to the Technical University of Denmark in partial fulfillment of the requirements for the Doctor of Philosophy degree (Ph.D degré). The work has been carried out at the Department of Applied Electronics, DTU (until 1/12-1997 Institute of Automation) and at Bang&Olufsen A/S, Denmark during the period April 1. 1995 to April 30. 1998. The project has involved four cooperating parties: Department of Applied Electronics, Bang&Olufsen A/S, CETEC and The Danish Energy Agency. All parties are thanked for the optimal working conditions in the project.

After receiving the M.Sc.E.E. degree in October 1994 at the Technical University of Denmark, I was recommended for the present project by assoc. professors Michael A. E. Andersen and John. Aa. Sørensen. I am deeply grateful for the confidence that made my participation in this exiting project possible. Michael A. E. Andersen has functioned as main supervisor in the project, and is thanked for the never failing support, and for sharing his knowledge in power electronics.

I should like to thank a number of people at Bang & Olufsen A/S for their contributions, help and support. Senior Technology Manager Palle Nissen is thanked for providing everything I needed during my stays at B&O. Audio Design Manager Egon Bjerre is thanked for sharing his invaluable knowledge on analog design. Everybody at the Electroacoustics R&D department are thanked for providing a stimulating frame during the numerous stays there. Especially, the assistance with practical implementation and subjective evaluation of various concepts has been of great value to the research.

My students at DTU during three years, in particular Frank. S. Christensen, Thomas Frederiksen, Thomas Taul, Poul Ciok, Søren Due, Niels Anderskov and Claus Neesgaard are thanked for their contributions to the present work. All have helped with the implementation and evaluation of various ideas and concepts during their M. Sc. and graduate projects. Furthermore, I am grateful to a number of other experts in the field with whom I have had enlightening discussions. Professor Keyue Smedley and Ph.D student Mark Smith Jr. are thanked for many interesting discussions on various topics at the University of California, Irvine during the four months I spent there in 1997. Professor John Vanderkooy, University of Waterloo, Canada, is thanked for inspiring discussions on various subjects in the field during his stay at B&O. My friend Mohammad Shajaan is thanked for his assistance in proofreading the manuscript.

Lastly, I should like to thank my fianceé and family for years of support and patience. This foundation has been of primary importance during the three years.

Lyngby, April 30, 1998

Karsten Nielsen

# Abstract

The audio power amplifier plays an essential role in every system that generates audible sound. General power amplifiers are voluminous, heavy, expensive, unreliable and have a very poor energy utilization, all due to a low efficiency. Solutions to this very fundamental problem is the topic of the present thesis. The ultimate goal is to develop practical methods for power amplification with a significantly higher efficiency at all levels of operation without compromises on the audio performance. The problem is addressed by investigating new methods for efficient power amplification using pulse modulation techniques. A general *Pulse Modulation Amplifier* (PMA) consists of a pulse modulator (analog or digital), a switching power stage for power conversion and a control system.

A fundamental study of both analog and digital pulse modulation methods is carried out. A novel class of multi-level pulse modulation methods - *Phase Shifted Carrier Pulse Width Modulation (PSCPWM)* - is introduced and shown to have several advantageous features, primarily caused by the much improved synthesis of the modulating signal. Enhanced digital pulse modulation methods for digital PMA systems are investigated, and a simple methodology for digital PWM modulator synthesis is devised. It is concluded, that the modulator performance is not a limitation in the system, regardless of the domain of modulator implementation.

Power conversion in PMA systems is addressed from the perspectives of both linearity and efficiency optimization. Based on detailed studies of the distortion mechanisms in the power conversion stage it is concluded, that this is the fundamental limitation on system performance due to several physical limitations. The analysis of general power stage efficiency concludes that dramatic improvements in energy efficiency are possible with PMA systems that are optimized for efficiency.

Control systems has been a focal point in the research. A control system design methodology is devised as a platform for synthesis of robust control systems. Investigations of three fundamental control structures show that even simple control systems offer a remarkable value, although the considered topologies also have their limitations which is verified by practical evaluation in hardware. A novel control method is introduced - *Multivariable Enhanced Cascade Control (MECC)*. Essentially, the topology offers a practical method for higher order control system implementation by an enhanced cascade structure. MECC provides flexible control over all essential system parameters and is furthermore simple in realization. Practical evaluation of a MECC based PMA shows state-of-the-art performance.

The application of non-linear control methods is investigated with the introduction of an enhanced non-linear control/modulator topology. Although the non-linear controller is theoretically interesting, the method proves to suffer from various practical limitations.

As a contribution to the field of digital PMA systems, a novel pulse referenced control method – *Pulse Edge Delay Error Correction (PEDEC)* – is introduced for enhanced amplification of an already pulse modulated signal. The principle proves to force equivalence between the digital modulator output and the digital PMA output. PEDEC is believed to be the first documented method for practical, efficient and high quality digital PMA realization including compensation for the non-linear power conversion.

# Resumé på dansk

Audio effektforstærkeren er en helt grundlæggende komponent overalt hvor der skal laves hørbar lyd. Generelle effektforstærkere er volumiøse, tunge, kostbare og har tillige en meget dårlig energivirkningsgrad, altsammen som følge af en dårlig effektivitet. Løsninger på dette helt fundamente problem er emnet for denne afhandling. Målet med projektet er således at udvikle praktiske metoder til effektforstærkning med et signifikant lavere effektab i alle brugssituationer uden at kompromittere kvaliteten. Problemet angribes ved at undersøge nye methoder for effektiv effektorstærkning baseret på pulsmodulations-teknikker. En generel *Pulse Modulation Amplifier* (PMA) er opbygget af en puls modulator (analog eller digital), en switchende effektomsætningsenhed og et reguleringssystem.

En fundamental analyse analoge og digitale pulsmodulationsmetoder gennemføres. En ny klasse af multi-niveau pulse bredde modulation methoder - *Phase Shifted Carrier Pulse Width Modulation (PSCPWM)* – introduceres herunder og viser at have flere fordelagtige egenskaber, primært skabt som følge af den meget forbedrede synthese af det modulerende signal. Metoder til realisering af digital pulsmodulation undersøges endvidere, og der udvikles en simpel design metodologi til digital PWM modulator syntese. Det konkluderes generelt, at modulatoren ikke er en begrænsning i systemet uanset hvilket domæne der vælges for implementeringen.

Effektomsætning til PMA systemer analyseres udfra såvel et linearitets- og effektivitetsperspektiv. På basis af detaljerede analyser af forvrængningskilder i effektomsætningen konkluderes det at dette element er den væsentlige begrænsning i systemet, som følge af en række fysiske begrænsninger. Analyserne af udgangstrin omfatter også en generaliseret teoretisk analysis af effektiviteten i effektomsætningen. Det komkluderes, det der kan opnås dramatiske forbedringer i energi effektivitet i PMA systemer optimeret mht. effektivitet.

Reguleringsmetoder udgør en helt central del af undersøgelserne. En metodologi til design af reguleringmetoder introduceres som en platform for syntese af robuste reguleringssystemer. Der undersøges tre basale reguleringstopologier, og det konkluderes at selv simple reguleringssystemer giver markante forbedringer af PMA systemet, selvom en evaluering af de tre metoder i hardware viser visse begrænsninger. Et nyt generelt reguleringsprincip introduceres – *Multivariable Enhanced Cascade Control (MECC)*. Princippet er en praktisk fremgangsmåde til realisering af højere orders reguleringssystemer under anvendelse af en *enhanced cascade* struktur. MECC giver flexibel kontrol over all væsentlige system parametre og er envidere simpel mht. realisering. Praktisk evaluering af en MECC baseret system viser state-of-the-art specifikationer.

Anvendelsen af ikke-lineære reguleringssystemer undersøges, ved introduktionen af et ikke lineært reguleringssystem der også fungerer som modulator. Til trods for teoretiske interessante egenskaber, viser metoden sig at lide under væsentlige fysiske begrænsninger.

Som et bidrag til området digitale PMA systemer, præsenteres en ny puls refereret reguleringsmetode – *Pulse Edge Delay Error Correction (PEDEC)* – for forbedret forstærkning af et allerede pulse moduleret signal. Det vises at at principippet fremtvinger ækvivalens mellem det puls modulerede indgangssignal og udgangssignalet. PEDEC menes at være den første dokumenterede metode for praktisk og effektiv realisering af højkvalitets digitale PMA systemer, der inkluderer kompensation for den ikke lineære effektomsætning.

# List of Abbreviations

The thesis defines a range of important abbreviations to ease the discussion and comparison of principles and methods. The abbreviations are described below for reference.

| Abbreviation | Description                                                                                                                                                                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMA          | Pulse Modulation (power) Amplifier. General definition of a system where the amplification is based on pulse modulation techniques and a switching power conversion stages. There are two alternatives: <i>Analog PMA</i> or <i>Digital PMA</i> referring to the use of analog or digital pulse modulation techniques. |

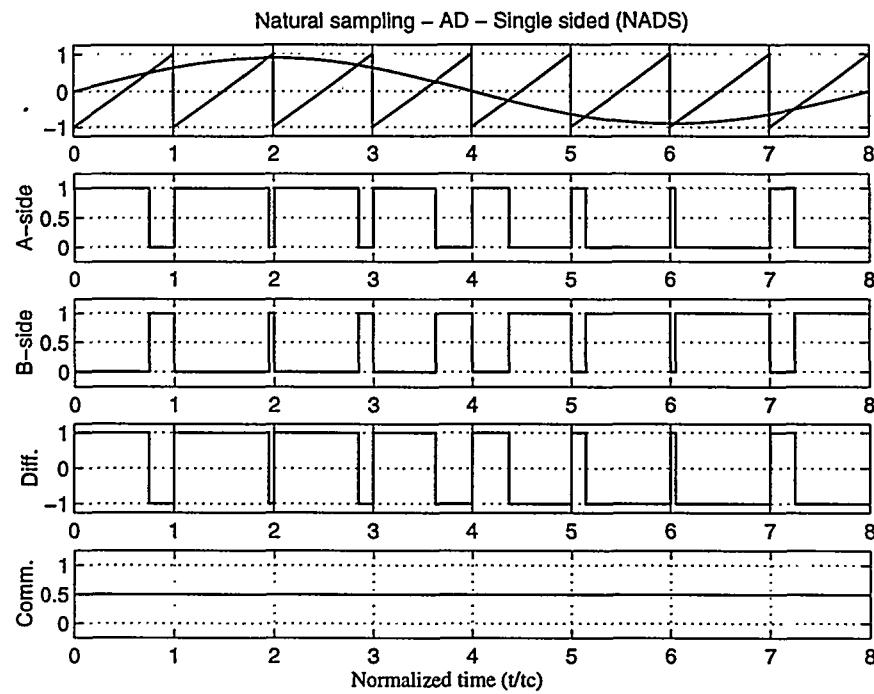

| NADS         | Natural sampling – AD – Single Sided                                                                                                                                                                                                                                                                                   |

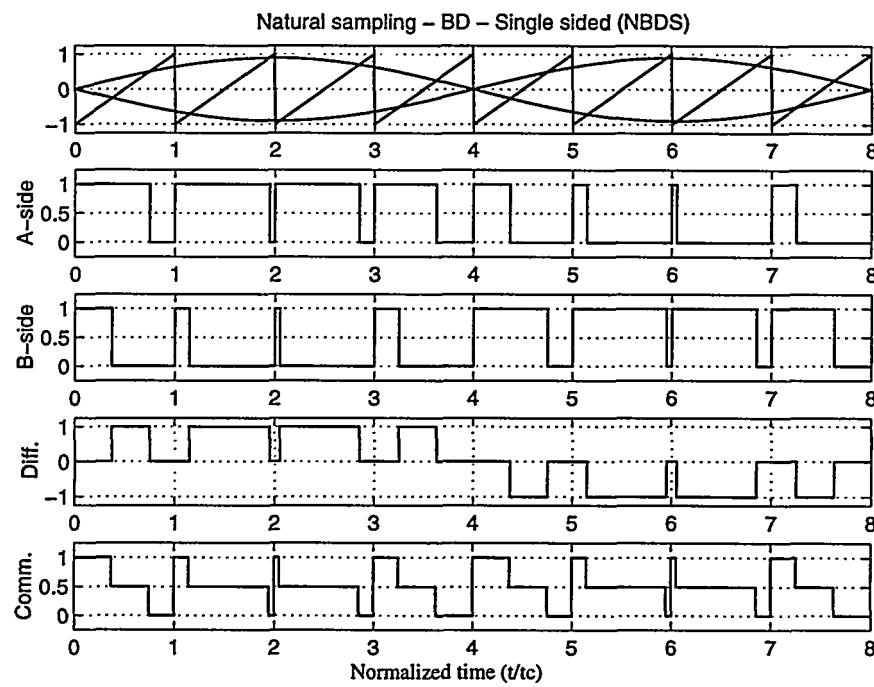

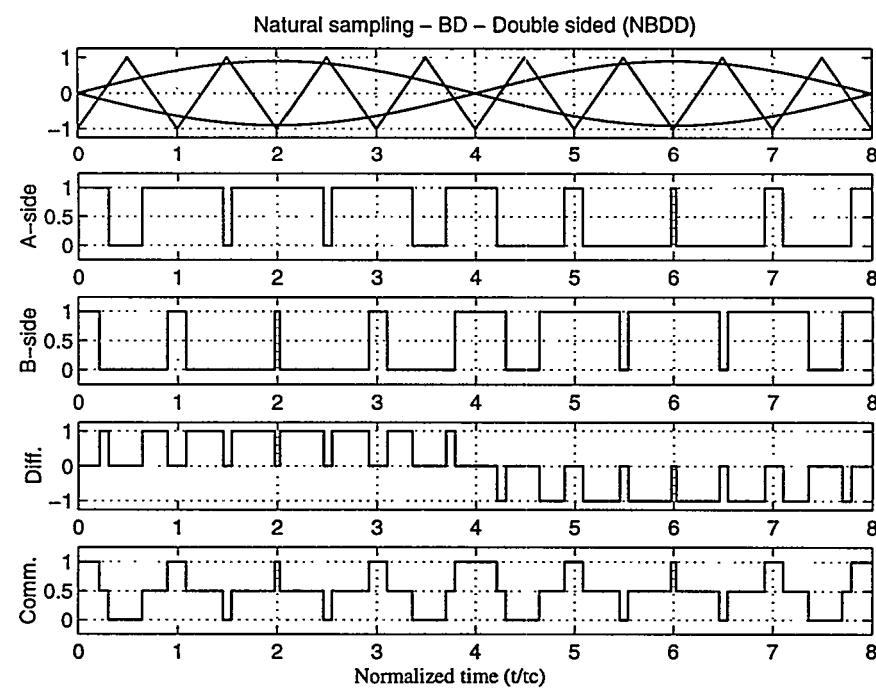

| NBDS         | Natural sampling – BD – Single Sided                                                                                                                                                                                                                                                                                   |

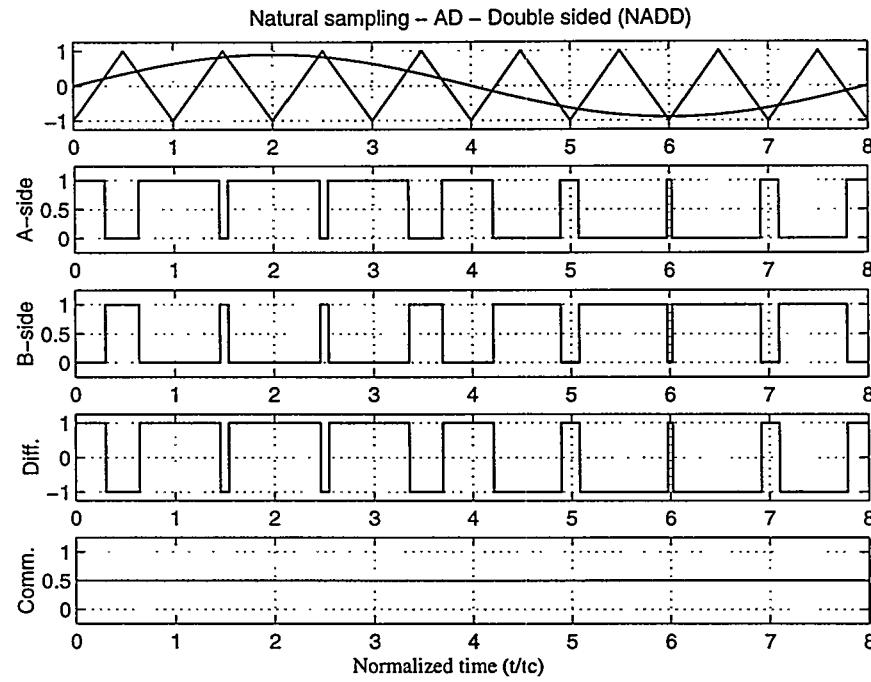

| NADD         | Natural sampling – AD – Double Sided                                                                                                                                                                                                                                                                                   |

| NBDD         | Natural sampling – BD – Double Sided                                                                                                                                                                                                                                                                                   |

| UADS         | Uniform sampling – AD – Single Sided                                                                                                                                                                                                                                                                                   |

| UBDS         | Uniform sampling – BD – Single Sided                                                                                                                                                                                                                                                                                   |

| UADD         | Uniform sampling – AD – Double Sided                                                                                                                                                                                                                                                                                   |

| UBDD         | Uniform sampling – BD – Double Sided                                                                                                                                                                                                                                                                                   |

| LADS         | Hybrid sampling – AD – Single Sided                                                                                                                                                                                                                                                                                    |

| LBDS         | Hybrid sampling – BD – Single Sided                                                                                                                                                                                                                                                                                    |

| LADD         | Hybrid sampling – AD – Double Sided                                                                                                                                                                                                                                                                                    |

| LBDD         | Hybrid sampling – BD – Double Sided                                                                                                                                                                                                                                                                                    |

| PSCPWM       | Phase Shifted Carrier Pulse Width Modulation.                                                                                                                                                                                                                                                                          |

| MLCPWM       | Multiple Leveled Carrier Pulse Width Modulation                                                                                                                                                                                                                                                                        |

| NS / US      | Naturally sampled Single Sided PSCPWM                                                                                                                                                                                                                                                                                  |

| ND / UD      | Naturally sampled Double Sided PSCPWM                                                                                                                                                                                                                                                                                  |

| BNDX / BUDX  | Balanced – Naturally/Uniformly sampled Double Sided PSCPWM                                                                                                                                                                                                                                                             |

| BNSX / BUSX  | Balanced – Naturally/Uniformly sampled Single Sided PSCPWM                                                                                                                                                                                                                                                             |

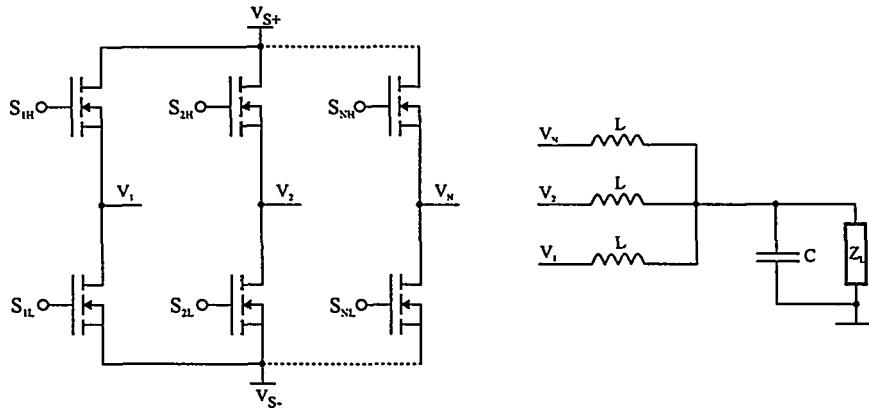

| PSC          | Power stage circuit topology for PSCPWM                                                                                                                                                                                                                                                                                |

| BPSC         | Balanced PSC power stage circuit topology for the balanced PSCPWM methods                                                                                                                                                                                                                                              |

| US           | Uncertainty set                                                                                                                                                                                                                                                                                                        |

| NS           | Nominal Stability                                                                                                                                                                                                                                                                                                      |

| NP           | Nominal Performance                                                                                                                                                                                                                                                                                                    |

| RS           | Robust Stability                                                                                                                                                                                                                                                                                                       |

| RP           | Robust Performance                                                                                                                                                                                                                                                                                                     |

| SRI          | Slew Rate Instability                                                                                                                                                                                                                                                                                                  |

| VFC1         | Voltage Feedback Control topology 1                                                                                                                                                                                                                                                                                    |

| VFC2         | Voltage Feedback Control topology 2                                                                                                                                                                                                                                                                                    |

| CVFC         | Current – Voltage Feedback Control topology                                                                                                                                                                                                                                                                            |

| PEDEC        | Pulse Edge Delay Error Correction.                                                                                                                                                                                                                                                                                     |

| PEDEC VFCX   | PEDEC Voltage Feedback topology X (X = 1, 2 and 3)                                                                                                                                                                                                                                                                     |

| TOCC         | Three level One Cycle Controller                                                                                                                                                                                                                                                                                       |

| PAE          | Pulse Amplitude Errors                                                                                                                                                                                                                                                                                                 |

| PTE          | Pulse Timing Errors                                                                                                                                                                                                                                                                                                    |

# **Chapter 1**

## **Introduction**

Fundamentally, only little has changed in the final stages of the audio reproduction chain for decades. The electrodynamic transducer as invented by C.W. Rice and E.W. Kellogg in 1925 still forms the basis for the majority of loudspeakers in use today and the principle has only seen marginal changes within nearly 75 years. The widespread use can not be justified by superior performance, in fact the principle of electric-acoustic conversion is limited by numerous fundamental problems, that makes this ultimate stage in the audio chain the weakest – by far. One essential limitation is the striking inefficiency. Generally, a given amount of acoustic power requires orders of magnitude higher power input delivered by the power amplifier. The power amplifier has the task of amplifying the audio signal to a level that, combined with sufficient current to move the coil, produces the desired acoustic level from the loudspeaker. The poor loudspeaker efficiency is very unfortunate, since power amplifiers generally have to be capable of delivering large amounts of undistorted power, to produce the subjective levels demanded by the consumer.

The field of audio power amplification has equally suffered from a lack of real breakthrough inventions for decades. Thus, sound reproduction today is founded on a few power amplifier principles that are characterized by a linear operation of the output transistors. The advantages include topological simplicity and good performance, but the linear amplifier principles suffer from low efficiency, which is critical since the power amplifier handles considerably amounts of power. Accordingly, power amplifiers are in general provided with massive heat sinks of extruded aluminum to cope with the heat development. Negative side effects of inefficient power amplification include high volume, weight, cost and reliability problems. Moreover, the power amplifier has low energy utilization, which is clearly not an attractive feature in this energy-conscious area.

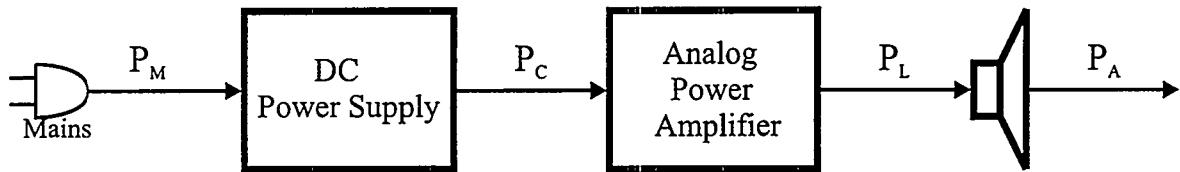

Fig. 1.1 Power flow in audio reproduction chain.

Consider the model of essential power flow in a typical audio system, shown in Fig. 1.1. To illustrate the low power utilization, a typical 100W power amplifier is considered. The power flow at two specific output levels is given below.

| Situation   | $P_M$ | $P_C$ | $P_L$ | $P_A$ |

|-------------|-------|-------|-------|-------|

| Typical     | 15W   | 10W   | 100mW | 1mW   |

| 1/3 of max. | 115W  | 90W   | 30W   | 300mW |

Clearly, the transducer is the fundamental source of the efficiency problems, i.e. an efficiency improvement by an order of magnitude would virtually eliminate the need for power amplification, as we know it today. However, most of the power is dissipated in the *power amplifier* due to low efficiency in this stage.

The primary objective of the research resulting in the present dissertation has been to invent practical power amplification methods with *significant* improvements in efficiency at all levels of operation – without any compromises on audio performance. Improving power amplifier efficiency isolated will have significant influences on overall system efficiency, especially at lower levels of operation where much can be gained.

It might seem paradoxical, that this level of efficiency is tolerated in the industry, especially since a low efficiency only has negative side effects. There are several answers to this apparent paradox. Principles for more high efficiency power amplification – so called Class D or switching power amplifiers – have been known for decades, however previous findings have shown several problems in terms of achieving the e.g. desired efficiency and audio specifications. On the other hand, methods to achieve sufficient levels of performance with linear power amplification are well known, and linear power amplification have over several decades of time established a reputation for good quality. A second problem is, that the audio community is highly conservative, often dominated by religious belief rather than scientific documentation and objective evaluation. Furthermore, only few have been interested in environmental issues despite the potential for dramatic improvements. Finally, amplifier weight, volume and energy consumption (!) has actually been considered a quality parameter (the larger and heavier the better), although there has never been any scientific documentation for any correlation between sound quality and these parameters. It is to expect however, that environmental issues will also reach consumer products. A high efficiency could become an attractive parameter in the future especially since labeling or standardization in consumer electronics is on its way [Ni95].

## 1.1 Audio power stage topologies

A brief introduction to commonly used circuit techniques for audio power amplification is given in the following with focus on their efficiency characteristics. It is common to differentiate between the different amplifier principles by their *class*. A list of used

| Class    | Characteristics                                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | Conducts signal current throughout the cycle of the signal waveform ( $360^\circ$ conduction)                                                   |

| B        | Conducts signal current exactly for one-half of the cycle of the input-signal waveform ( $180^\circ$ conduction)                                |

| AB       | Class B with bias to avoid crossover distortion.                                                                                                |

| C        | $<180^\circ$ conduction with resonant loading. This method is primarily for RF frequency, and is only rarely used in the audio frequency range. |

| D        | $0^\circ$ conduction. The power stage transistors are switched which in theory prevents the system from entering the active region.             |

| B2, G, H | Extension of class B where more complex power supply circuitry is used to improve efficiency.                                                   |

Fig. 1.2 Amplifier techniques reviewed.

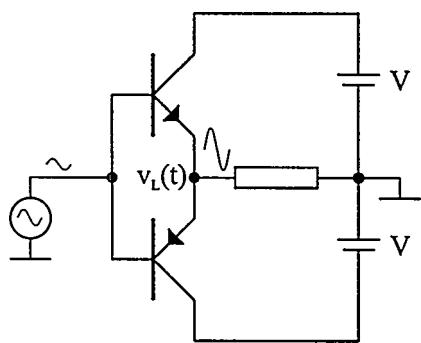

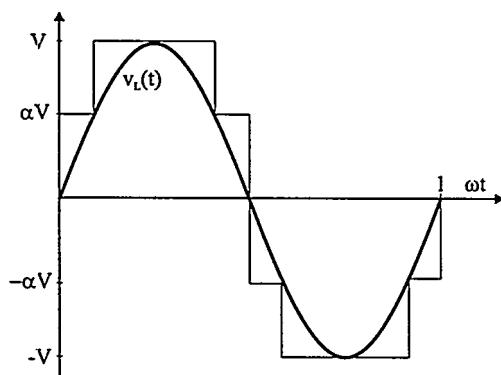

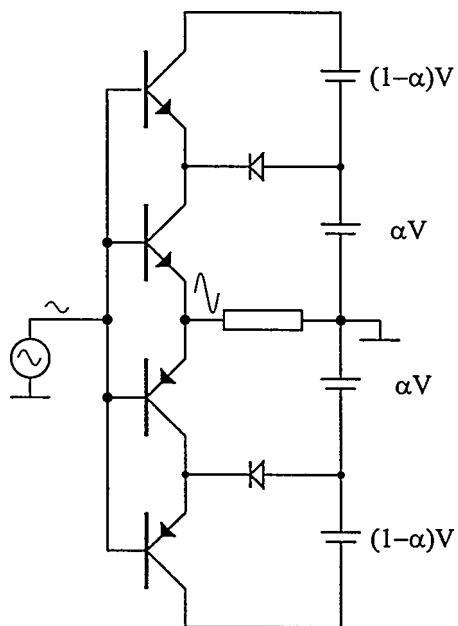

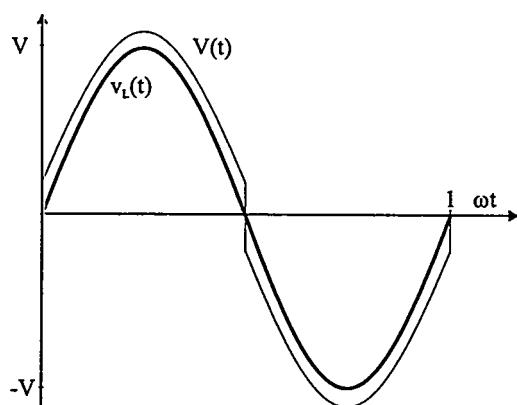

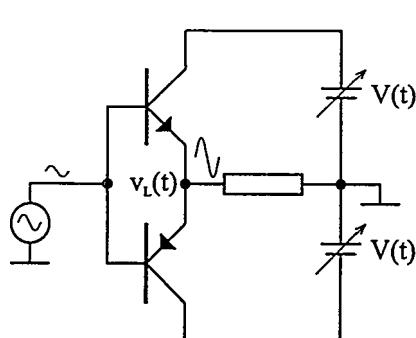

classifications is listed in Fig. 1.2, with a short description of the characteristics [Be88]. The Class AB and B output stage topology, shown in Fig. 1.3 (top), forms the basis for the majority of power amplifiers today, and design techniques to realize high quality class B amplifiers have been known for decades. However, since the output voltage is derived from the supply voltage via the output transistors, it follows that the difference between the output voltage and the rail voltage must be dropped *across* the output transistors. This results in a wasteful dissipation of energy in the output transistors. The effective voltage drop across the output stage transistors can be reduced by the complex class B2 or class G configuration shown in Fig. 1.3.

### 1.1.1 Power and energy efficiency

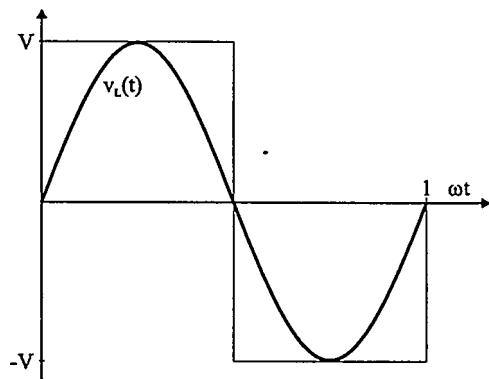

Since amplifier efficiency is an essential parameter throughout the thesis, the efficiency of the most widely used power amplifier principles is investigated and compared. It is trivial to derive analytic expression for the efficiency vs. relative output level as shown in Appendix A for the three amplifier principles. The *power efficiency* is the ratio of utilized power over the supplied power:

$$\eta_P(x) = \frac{P_L(x)}{P_S(x)} \quad (1.1)$$

Where  $x$  denotes the relative output level. The amplifier output power is:

$$P_L(x) = x^2 \frac{V^2}{2R_L} \quad (1.2)$$

As shown in appendix A, the efficiency for the three output stage configurations are:

$$\eta_B(x) = x \frac{\pi}{4} \quad (1.3)$$

$$\eta_{B2}(x, \alpha) = \begin{cases} \frac{\pi}{4} \frac{x}{\alpha} & (x < \alpha) \\ \frac{\pi}{4} x \frac{1}{\alpha + (1-\alpha) \int_{\alpha \sin(\frac{\pi}{x})}^{\frac{\pi}{2}} \sin(\omega t) d(\omega t)} & (x \geq \alpha) \end{cases} \quad (1.4)$$

Class B

Class B2

Class G

Fig. 1.3 Three widely used output stage configurations Class B, Class B2 and Class G.

$$\eta_G(x, \beta) = x \frac{\pi}{4} \left( \frac{1}{\beta + x \frac{\pi}{4}} \right) \quad (1.5)$$

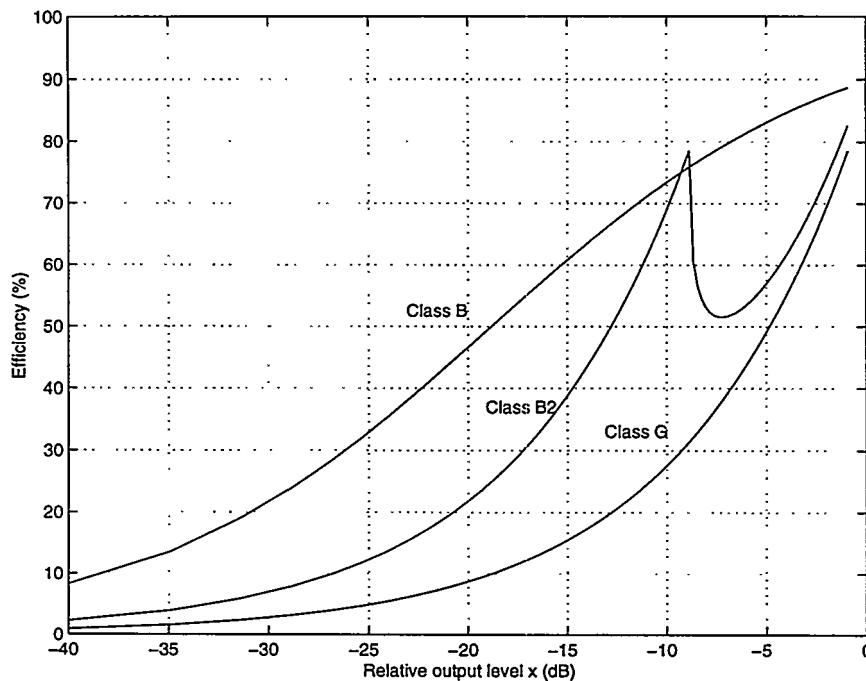

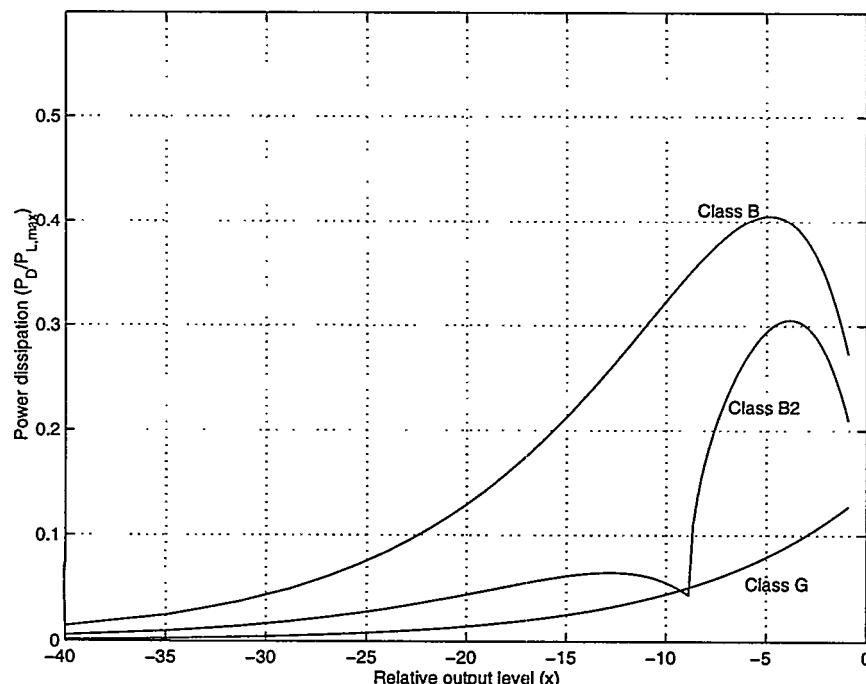

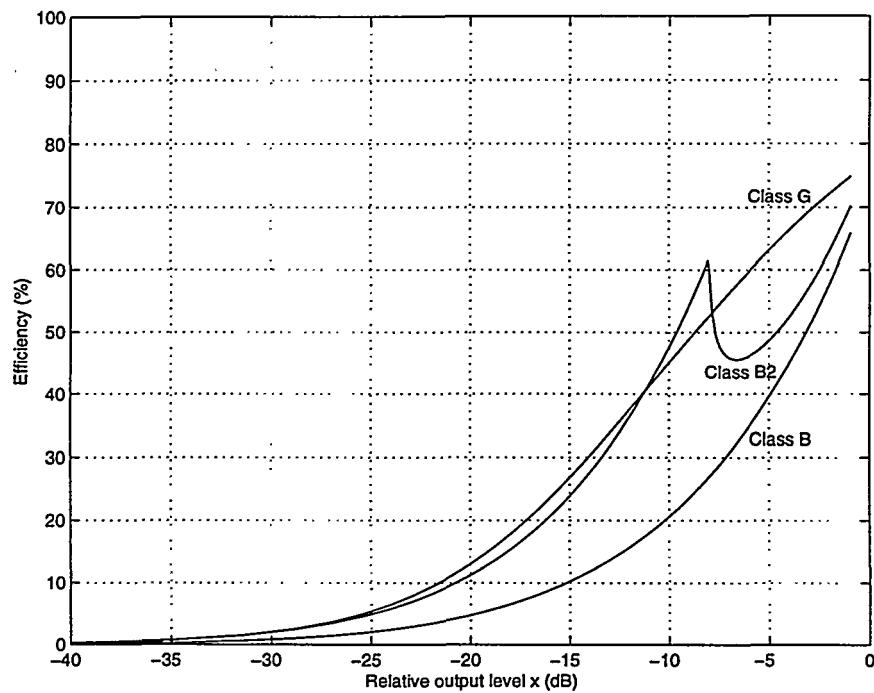

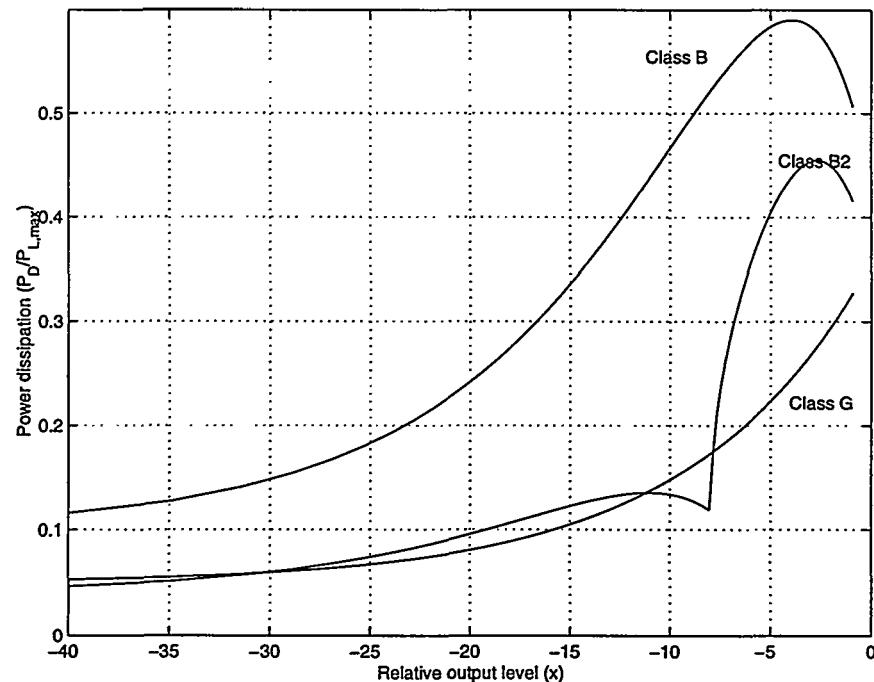

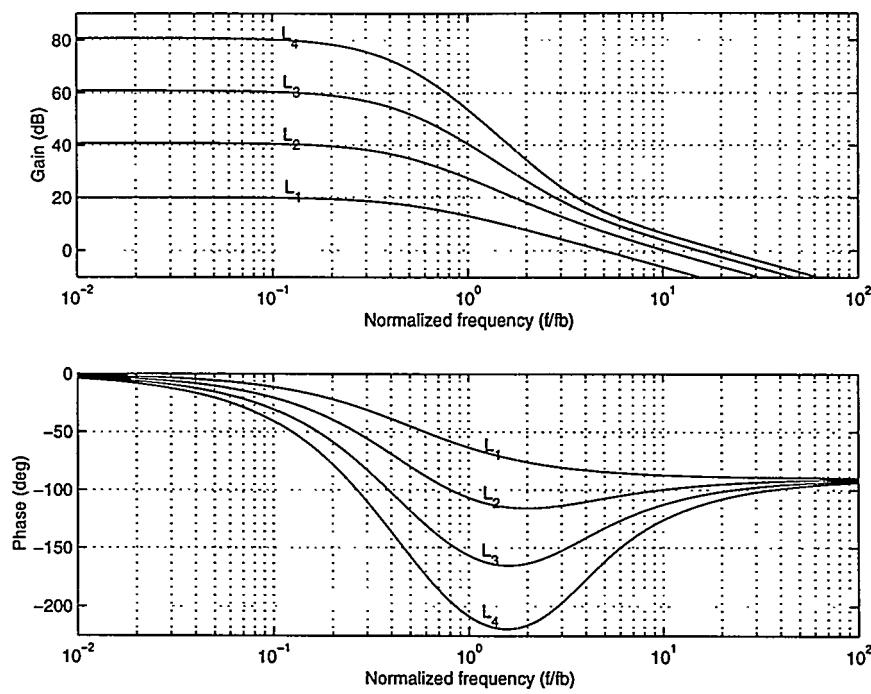

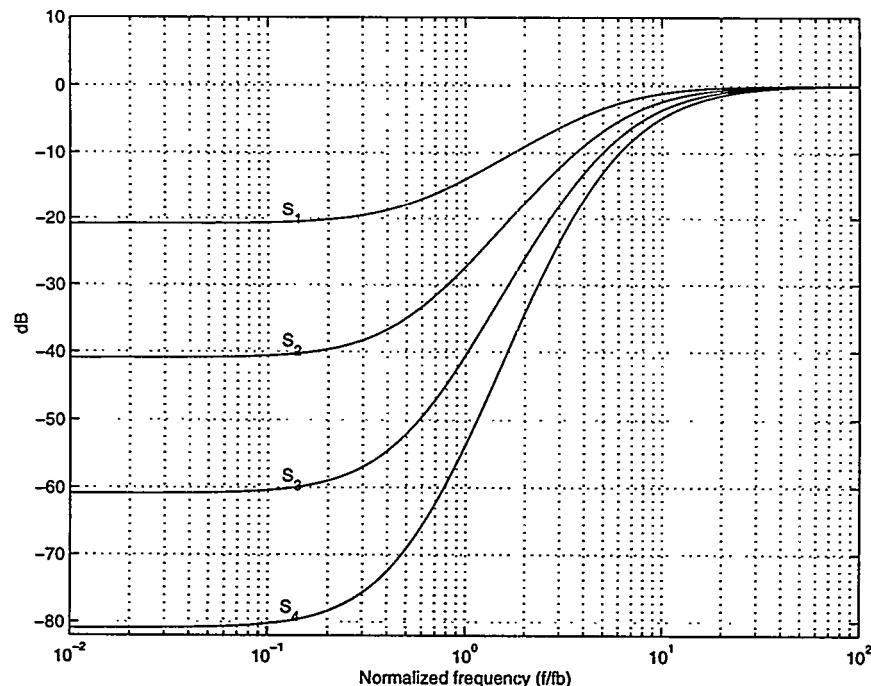

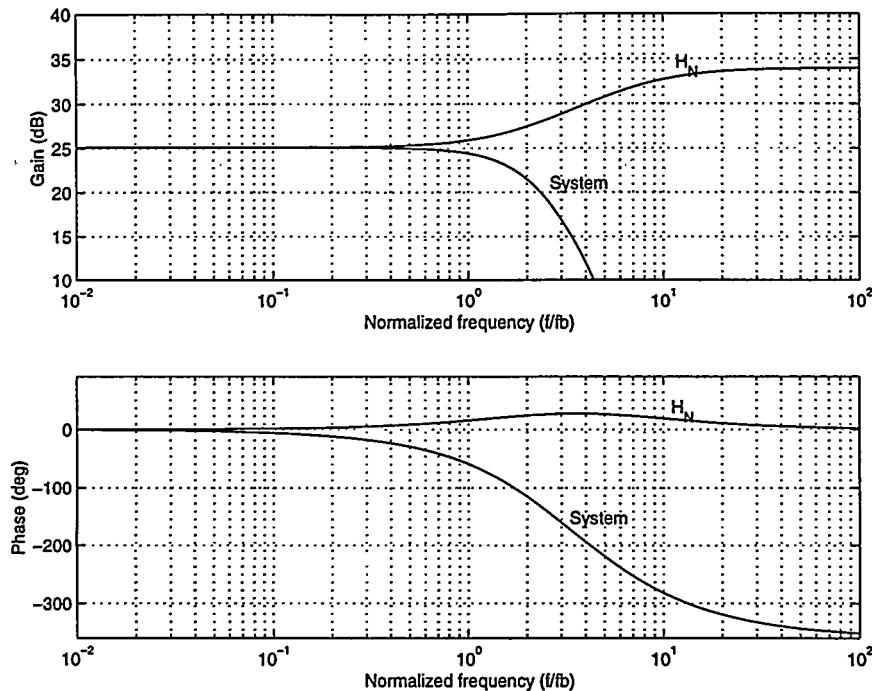

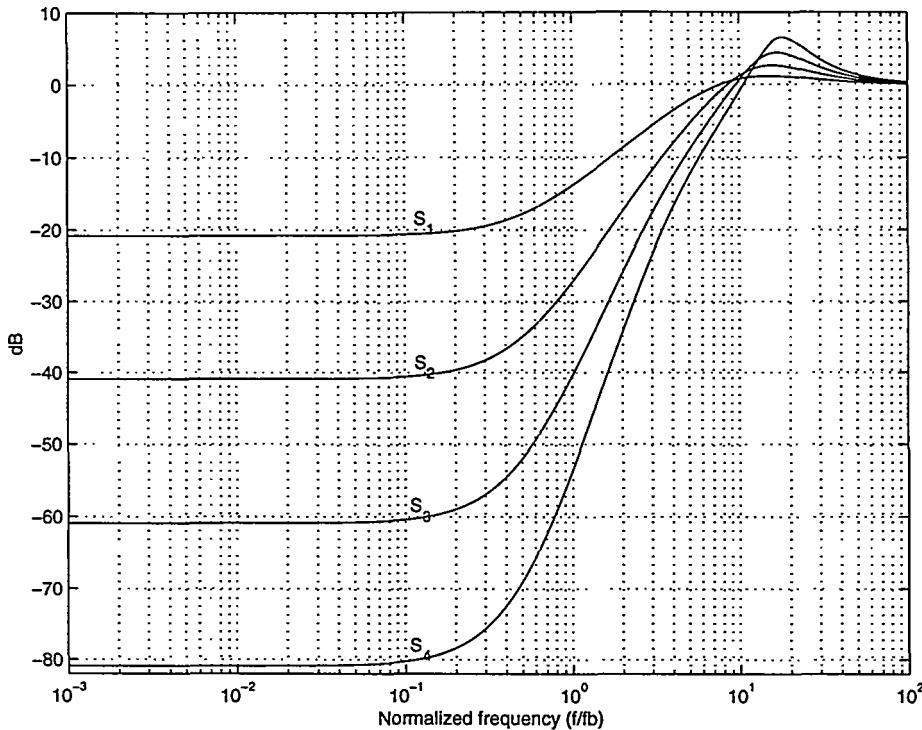

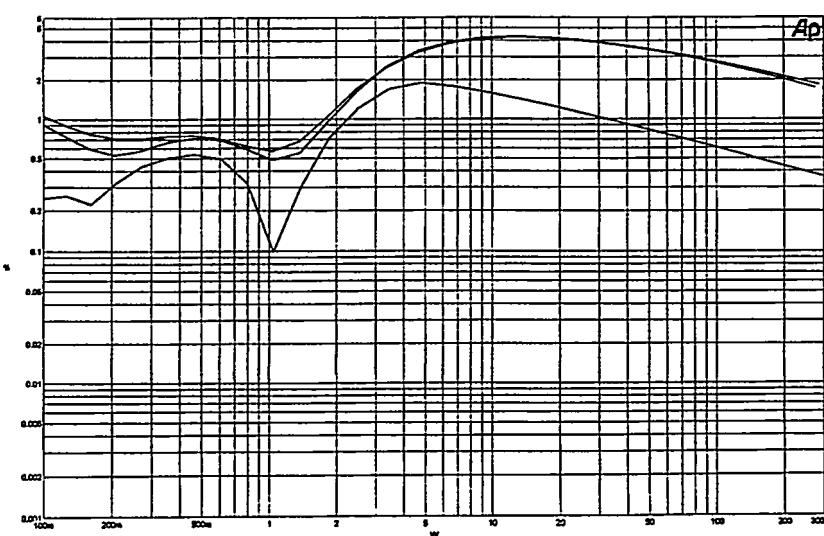

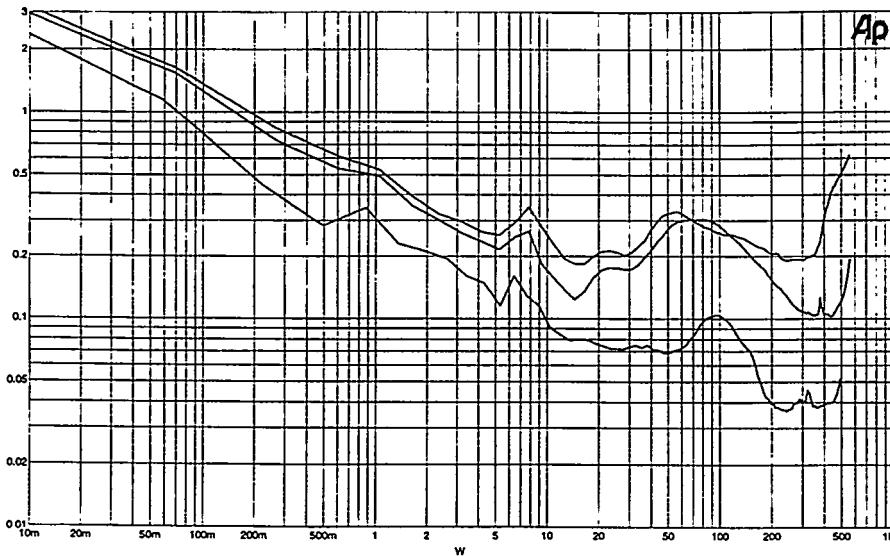

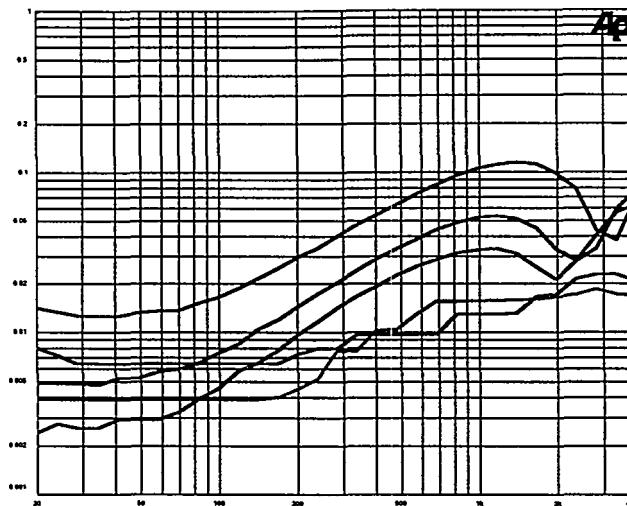

Fig. 1.4 shows the ideal efficiency vs. relative output level for the three amplifier principles, and Fig. 1.5 equally shows the relative power dissipation vs.  $x$ . Class B2 and G and achieve reasonable efficiencies at higher output powers, but all topologies still have significant power dissipation at all output levels. In more aspects, these idealized models are not sufficient to estimate the real output stage efficiency especially at lower output levels. There are practical limitations further decreasing the efficiency of the output stage topologies, such as the necessary quiescent current to linearize the output stage and the saturation voltages in the output stage transistors. Subsequently, more realistic models of the three output stage topologies have been investigated that incorporate these important effects. Fig. 1.6 and Fig. 1.7 shows the efficiency and relative power dissipation of these more realistic output stage topologies. Note how the typical efficiency of all topologies is extremely low, primarily due to the significant power loss at quiescence.

### 1.1.2 Energy efficiency considerations

There is only little correlation between power efficiency and the amplifier energy consumption, since the power efficiency is typically specified at the level of maximal power dissipation or at the maximal output level. An alternative efficiency measure - the energy efficiency - is defined in the following. The basis is investigations of the general consumer behavior in terms of an average time distribution of volume control positions. Such a distribution will vary as a consequence of e.g. loudspeaker sensitivity, room size, user age and numerous other parameters. However, it is possible to generalize [Ha94b] and define four subjective listening levels as given in Table 1.1. The distribution should be interpreted as: In 89% of the time, the average user listens to background music with an average output level of -40dB etc. Since the distribution might vary dependent on application (e.g. in professional systems the distribution would be different), a general time distribution is considered:

$$(n_1, P_{L,1}, P_{S,1}), (n_2, P_{L,2}, P_{S,2}), \dots, (n_N, P_{L,N}, P_{S,N}) \quad (1.6)$$

$(n_j, P_{L,j}, P_{S,j})$  refers to that the output power in average is  $P_{S,j}$  in  $n_j$  percent of the time and  $P_{S,j}$  refers to the supplied power at the given output power. The *energy efficiency* is derived as the ratio of the average output power and the average supplied power:

$$\eta_E = \frac{\sum_{i=1}^N n_i \cdot P_{L,i}}{\sum_{i=1}^N n_i \cdot P_{S,i}} \quad (1.7)$$

| Distribution in time | Output level (rel.) | Subjective level |

|----------------------|---------------------|------------------|

| 0 %                  | 0 dB                | Clipping         |

| 1 %                  | -9 dB               | Party            |

| 10 %                 | -24 dB              | Listening        |

| 89 %                 | -40 dB              | Background       |

Table 1.1 Average time distribution of volume control positions.

Fig. 1.4 Efficiency vs. relative output level for ideal power amplifier output stages.

Fig. 1.5 Power dissipation vs. relative output level for ideal power amplifier output stages.

Fig. 1.6 Efficiency and power dissipation for realistic models of class B, B2 and G power amplifier output stages topologies.

Fig. 1.7 Efficiency and power dissipation for realistic models of class B, B2 and G power amplifier output stages topologies.

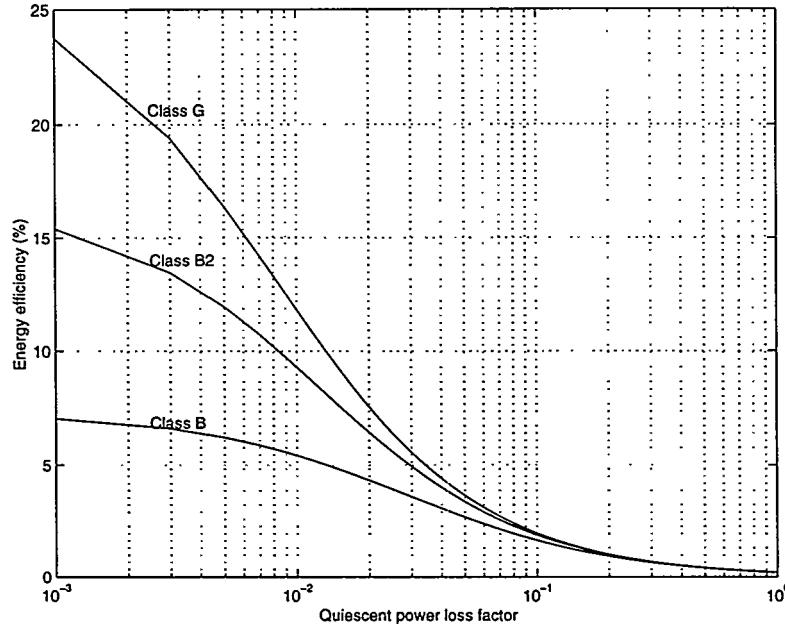

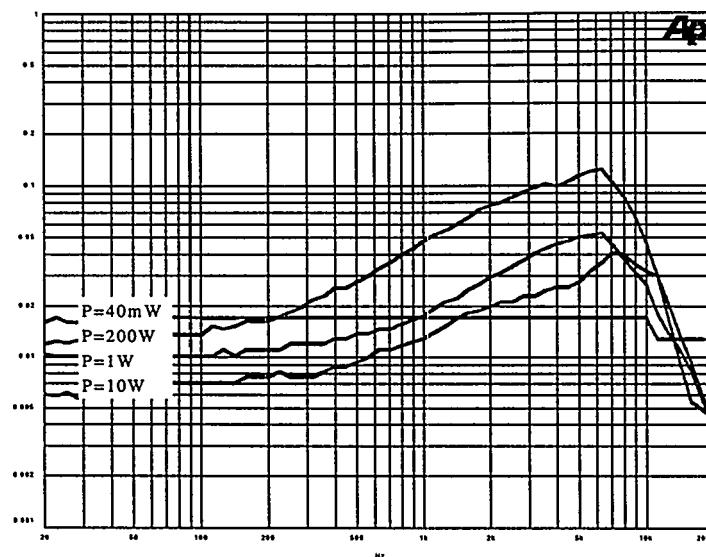

Fig. 1.8 Energy efficiency of Class B, Class B2 and Class G.

The parameter can be used to minimize the energy consumption in any system. Let the *quiescent power loss factor*  $\lambda$  be defined as:

$$\lambda = \frac{P_s(0)}{P_{L,\max}} \quad (1.8)$$

Fig. 1.8 illustrates the energy efficiency for the realistic models of class B, B2 and G power output stages, as a function of  $\lambda$ . The typical energy efficiency for a class B output stage is only:

$$n_E \approx 1 - 2\% \quad (1.9)$$

This holds for  $\lambda$  between 0.1 and 0.2, which is typical for a class B output stage. Note that the energy efficiency for an *ideal* class B amplifier is only 7.1%, due to the inherent losses bound to the linear operation of the output transistors. Since the power amplifier operates in the “background music” mode most of the time, the important parameters in terms of energy efficiency are not surprisingly the power dissipation at low output levels and especially the quiescent power dissipation. The energy efficiency of class B2 and class G can be made considerably better (see Fig. 1.8) if the  $\lambda$  is sufficiently low. However, this is not easy to obtain in any of the two alternatives. For class B2, lowering  $\alpha$  will compromise the efficiency at higher output levels (no gain compared to class B) and for class G, the switching power supplies will cause the quiescent power loss  $\lambda$  factor to be high. To conclude, all output stages have their limitations, and more than a doubling in energy efficiency by optimization cannot be expected.

### 1.1.3 The switching (Class D) power stage topology

Based on this initial investigation of output stage topologies it is concluded that considerable improvements in efficiency cannot be achieved with output transistors operating in the linear range. A completely switching power stage is needed. This approach

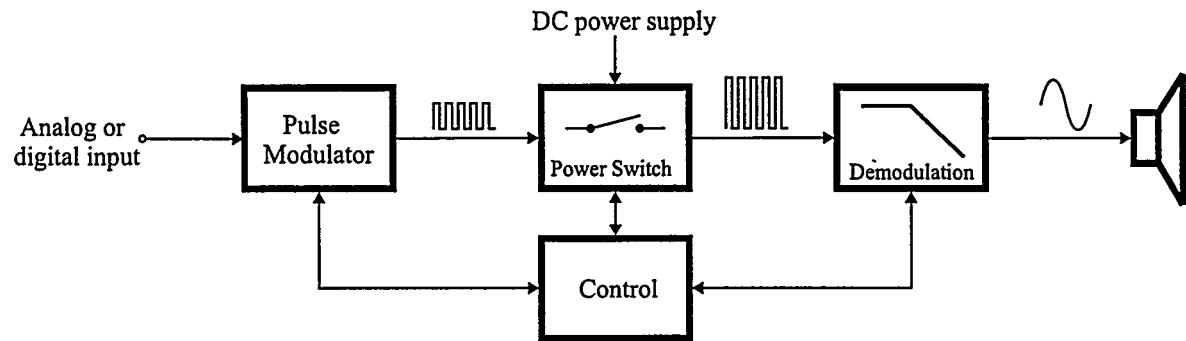

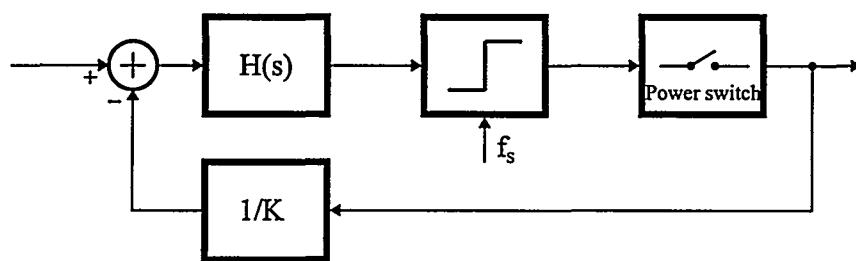

Fig. 1.9 General Pulse Modulation Amplifier (PMA) utilizing a class D power stage.

has the inherent advantage of a 100% theoretical efficiency. With the continuing improvements in power switching devices, the efficiency will converge towards this theoretical optimum as time progresses. Throughout the years the fundamental principle of power amplification using switching technology has been called class D, switching power amplification, digital power amplification and PWM power amplification. Recently, what is believed to be a more suitable and general designation – Pulse Modulation Amplifiers (PMA) – has been introduced by the author [Ni97a]. This general designation will be used henceforth.

## 1.2 The Pulse Modulation Amplifier (PMA)

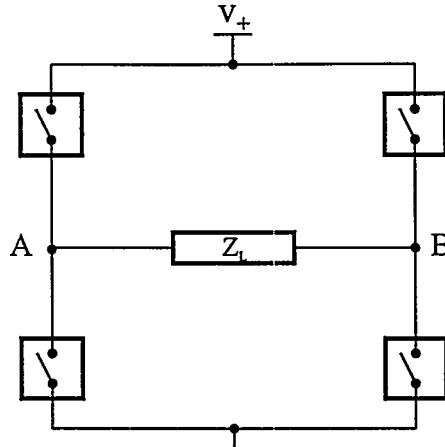

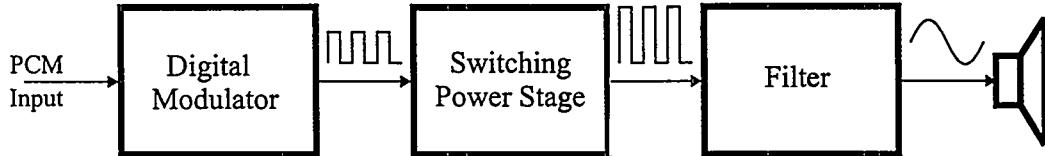

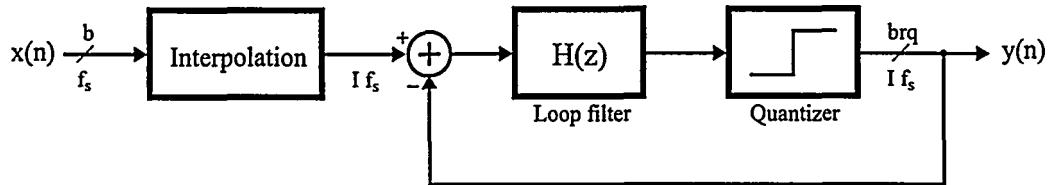

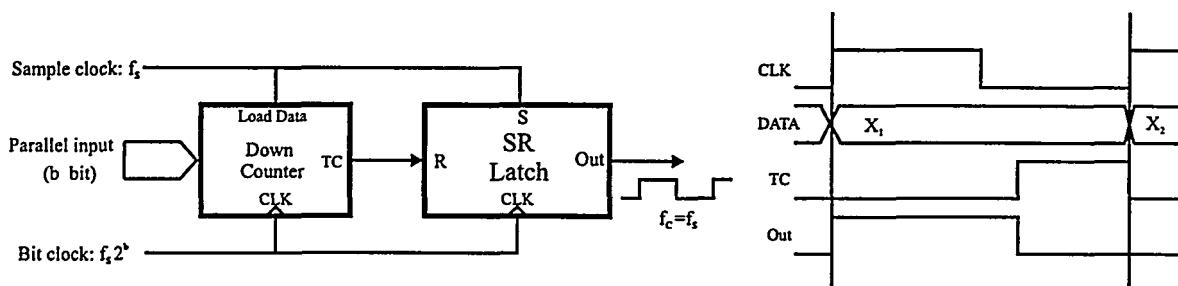

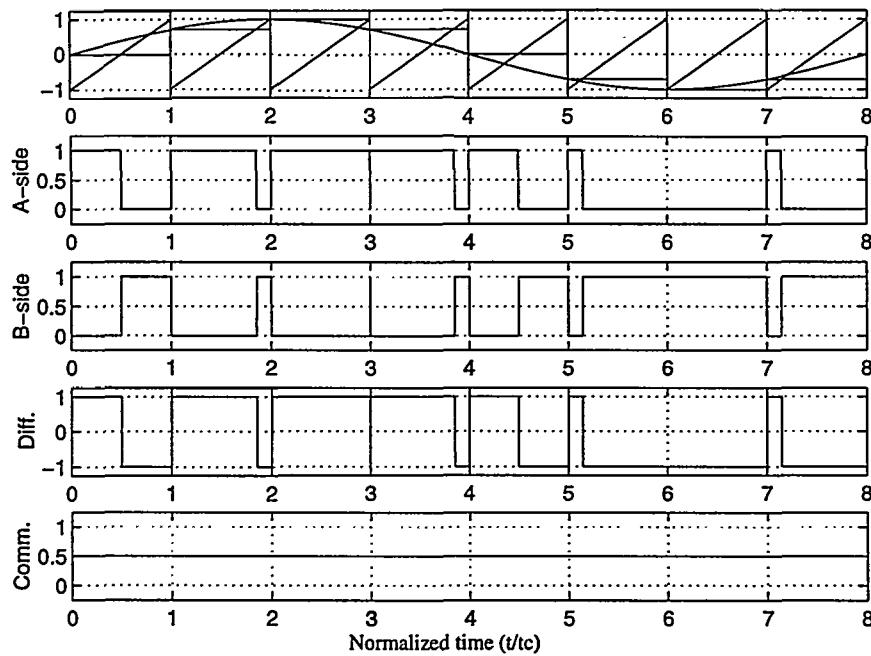

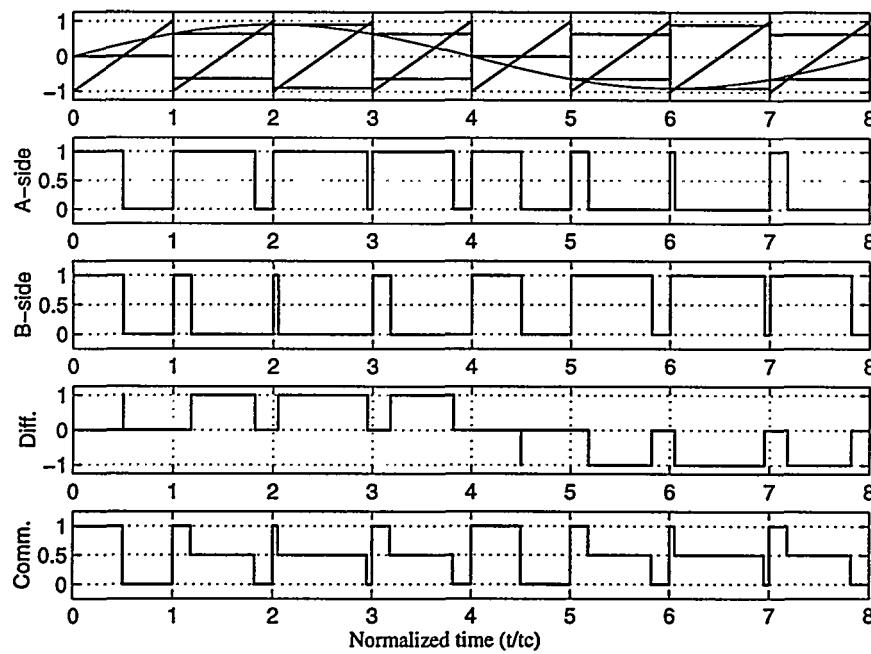

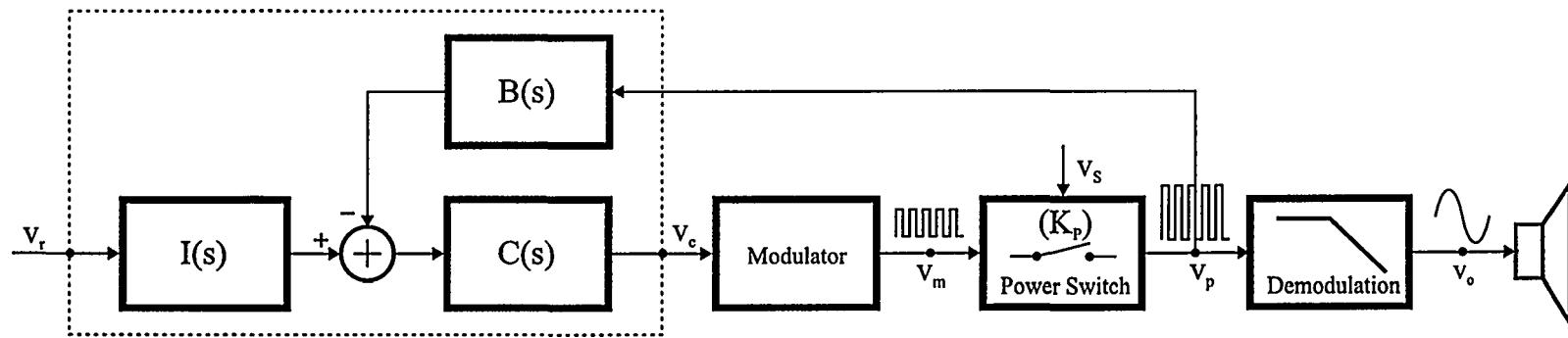

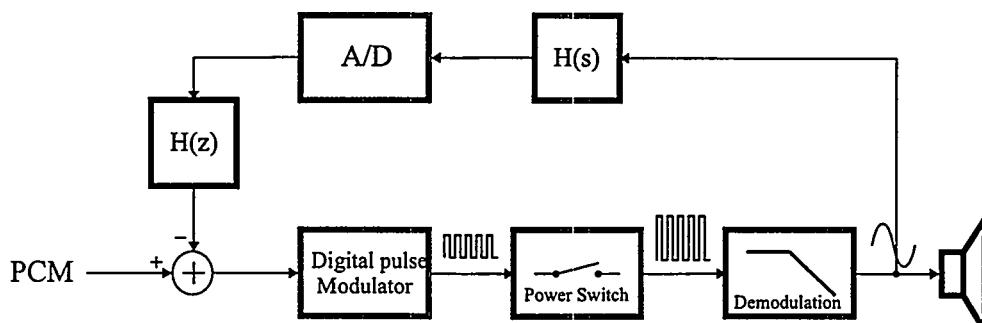

Fig. 1.9 shows the general PMA topology. The four fundamental blocks are the *pulse modulator*, the *switching power stage*, the *demodulation filter* and the *error correction* block. The pulse modulator may be based on either analog or digital pulse modulation techniques, correspondingly referenced to as analog PMA and digital PMA systems. The power switch converts the pulse modulated signal to power level. Following, the power pulse modulated signal is feed to a filter to reconstitute the modulated signal. The control system serves to compensate any errors that are introduced in each of the three essential blocks of the system.

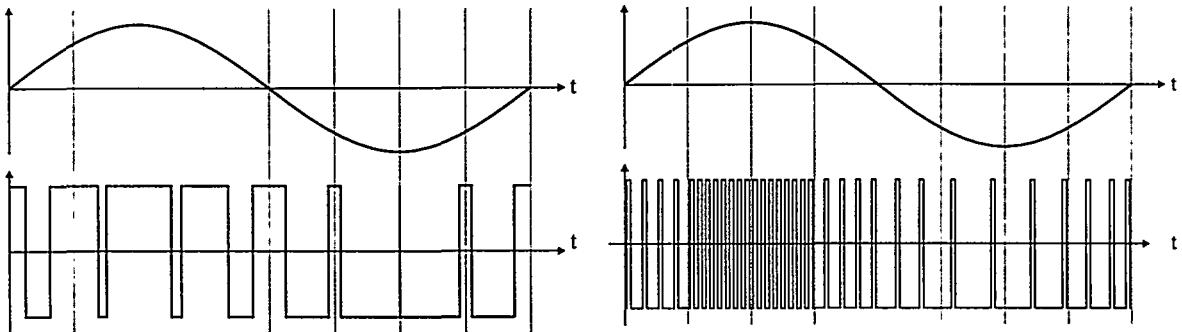

The pulse modulator is the heart of the PMA system. Two analog pulse modulation methods for PMAs are PWM and PDM, shown in Fig. 1.10. The methods may be implemented in both the analog and digital domain. The modulator output generally contains three distinct elements:

- The modulated signal.

- Distortion components related to the modulated signal.

- A high frequency spectrum.

The high frequency output is composed of either discrete components related to the carrier, noise shaped noise or a combination of both. The pulse modulator can be based any scheme performing a coding of the modulating signal to a pulse modulated form. One of the objectives of this thesis is to research in coding schemes that provides optimal PMA performance.

Power amplification based on pulse modulation techniques in combination with a switching class D power stage have been known for decades. Some of the first designs were already presented by e.g. Sinclair and Johnson [Jo67], [Jo68] some 30 years ago. However, until recently the research has been quite modest with only a few noteworthy publications as e.g. [At83], [Ha91]. Within the last decade, the field has “resurrected” now with focus on digital pulse modulation methods for digital PMA systems. An exhaustive

Fig. 1.10 PWM and PDM pulse modulation methods.

set of publications exists on this specific subject, e.g. [Sa86], [Le91], [Go91], [Go92], [Ha92] and [Hi94]. The digital PMA approach was considered a break-through in audio power amplification. Nevertheless, it has proven very difficult to realize the acceptable audio performance in both analog PMA and digital PMA system. The problems relate to the non-linear power conversion and demodulation.

### 1.2.1 Design problems and challenges

PMA systems and audio power amplifiers in general are complex non-linear systems. Thus, power amplifiers are subject to varying input signals, generally drive reactive loads, are most often supplied by non-regulated power supplies which supply the other channels for sound reproduction. Furthermore, power amplifiers might be subjected to overload situations if not prevented. No power amplifier can be optimized without a simultaneous consideration of a broad range of desired specifications. Furthermore, the tolerance of these specifications has to be considered. The essential issues to consider when designing and evaluating power amplifier systems are outlined below.

#### Gain

*A specification of the insertion gain of the system typically specified in dB.*

#### Frequency response / Bandwidth

*The ability of amplifier to amplify signals over a range of frequencies, with defined source and load. Specifications are generally a -3dB bandwidth, and a tolerance on the deviation from the desired response at any frequency up to the bandwidth limit.*

#### Harmonic distortion / Intermodulation distortion

*The non-linear behavior of the amplifier causes harmonic distortion (THD) and intermodulation distortion (IMD). Moreover, the distortion will in general depend on parameters as signal level, frequency and load parameters. Distortion has to be well controlled within this parameter space. Distortion is normally specified in percentage or dB. Various IMD measurement methods exist as the two-tone CCIF, SMPTE or Transient Intermodulation Distortion (TIM).*

#### Noise / Signal-to-noise ratio / Dynamic range

*All amplifiers have internal noise sources that contribute to the output noise. Typical specifications are the residual noise referred to the output with terminated input or the Signal-to-noise ratio relative to a given output level e.g. 1W. Also frequently used is the dynamic range, which is the relationship between the maximal RMS voltage output before clipping and the RMS of the residual noise.*

## Output impedance / Loading

*The load impedance is generally frequency dependent with resonant peaks etc. The influences of a variable load in system frequency response should be minimized. Furthermore, the amplifier output impedance should be as low as possible to cope with variations in nominal load impedance.*

## Power Supply Rejection

*The power amplifier has to cope with the inevitable power supply perturbations. The amplifier should be able to suppress these perturbations such that the output is not influenced. A widely used specification is the power supply rejection ratio (PSRR), which is the sensitivity of the output to perturbations on the power supply. The rejection of such perturbations has to be controlled over the complete bandwidth.*

## Stability

*A control system is generally required to secure robust performance for the power amplifier. This introduces a potential risk of instability. The amplifier should be prevented from instability under all circumstances, since this will generally have dramatic consequences as a burn out of the speaker of the amplifier itself.*

There are no definitive margins between what is required to be acceptable and unacceptable. However, a set of parameters corresponding to satisfying performance in most applications can be specified:

| Parameter          | Condition                  | Value    |

|--------------------|----------------------------|----------|

| Bandwidth          | -3dB                       | > 60KHz  |

| Power bandwidth    | -3dB                       | > 20KHz  |

| Frequency response | 20Hz – 20KHz               | <± 0.2dB |

| THD                | @ 1W / 1KHz                | < 0.01 % |

| THD                | 20Hz-20Hz (complete range) | < 0.05 % |

| IMD                | CCIF two tone              | < 0.01%  |

| SNR                | A weighted @ 0dBW          | >90 dB   |

| Dynamic range      | A weighted                 | > 110dBA |

| Load range         |                            | 2-16 Ω   |

| PSRR               | All frequencies            | > 40dB   |

A power amplifier with a reasonable power handling capability (e.g. 100W) is considered.

### 1.2.2 Other considerations

The application range for high efficiency power amplification is very broad. Active speaker systems with dedicated speakers and power amplifiers for each frequency band is a specifically interesting application. This enclosed environment offers some special advantages:

- The load and amplifier can be matched perfectly. Load variations (typically 2, 4 and 8 ohms) do not have to be considered.

- Connection wires from amplifier to speaker can be minimized.

- Bandwidth limited amplification can be utilized to optimize the efficiency.

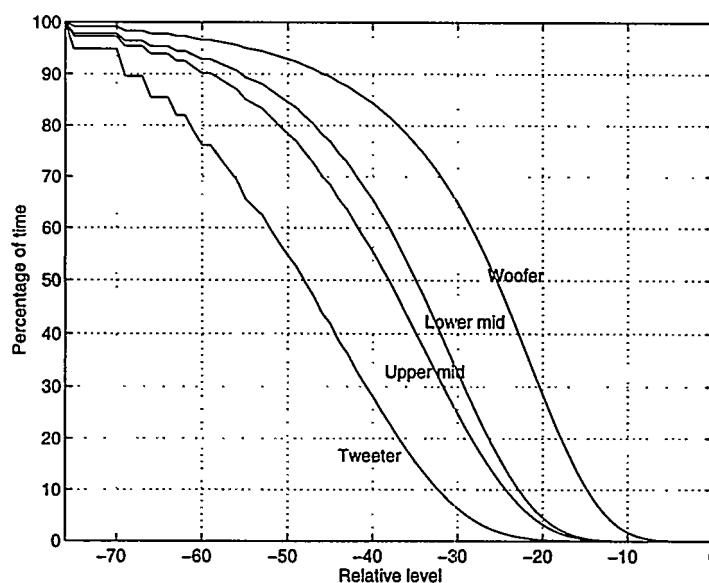

The general spectral amplitude distribution of music material only emphasizes that the technology has certain advantages in active speaker systems. Almost independent of music material, the average acoustic power in the tweeter band 4KHz – 20KHz is much lower

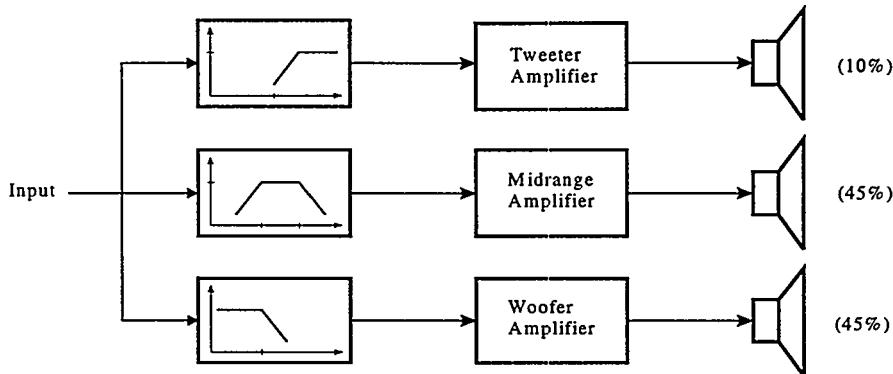

Fig. 1.11 An active speaker system (here 3 way) based on separate amplifiers for each band.

than in the other bands. Fig. 1.12 illustrates a more specific analysis. This will be reflected in the power amplifier size for each band as illustrated with a typical active 3-way speaker system in Fig. 1.11. Thus, the power handling capability is only around 10-15% of the total power in the tweeter band. Optimization of energy efficiency in active speaker systems can as such be carried out by improving efficiency in the lower 20% of the frequency band only. In this particular environment, the PMA design challenge is clearly somewhat different from the general case.

### 1.3 Thesis structure

The primary objective of the research resulting in the present dissertation has been to invent practical power amplification methods with significantly improved efficiency at all levels of operation – without any compromises in terms of audio performance. It will become apparent when reading the thesis, that this has required multi-disciplinary research involving such diverse fields as e.g.; analog and digital modulation theory, power electronics, DSP, semi-conductor physics and control systems.

The thesis is divided in two volumes, the main part consisting of 11 chapters divided in four parts, and a second volume consisting of the three appendices A, B and C.

Fig. 1.12 An example of the distribution of signal levels on a CD in four bands. The bands are divided at 650hz, 1500hz and 4.5KHz. The programme material is "The Division Bell" by Pink Floyd.

Chapter 1 has introduced the motivating factors and the foundation for the research.

**Part I** (Chapters 2-3) presents a comprehensive analysis of analog and digital pulse modulation methods suitable for analog PMAs and digital PMAs, respectively.

Chapter 2 is devoted to analog pulse modulation methods. A broad set of pulse modulations methods are subjected to a fundamental analysis of their suitability in analog PMA systems. The chapter contributes to fundamental modulation theory by introducing a novel family of modulation methods – Phase Shifted Carrier Pulse Width Modulation (PSCPWM).

Chapter 3 is devoted to digital pulse modulation methods for digital PMAs. Previously presented methods are reviewed. A simple design methodology is presented for digital PWM modulators.

**Part II** (Chapters 4-5) continues to the second major block of the PMA - the power stage. Power stage structures are synthesized and analyzed, and methods for optimal power stage implementation are devised.

Chapter 4 is dedicated to a fundamental analysis of error sources within PMA systems. It is shown how the power conversion stage seriously effects all the important parameters of the system, i.e. linearity, noise and efficiency. Modulator error sources are also investigated.

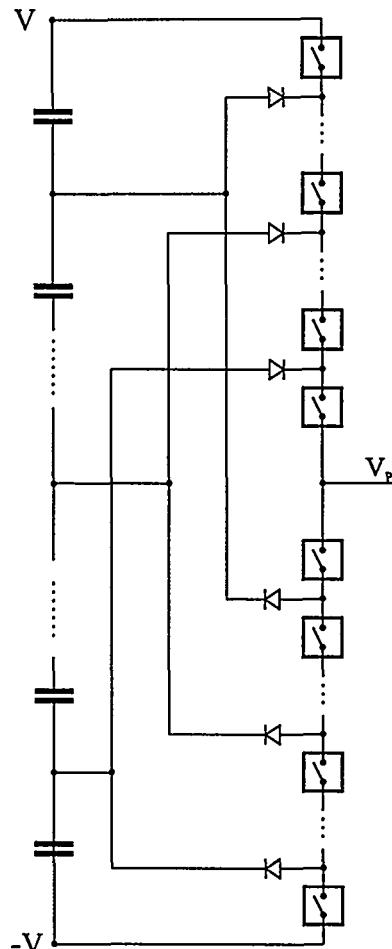

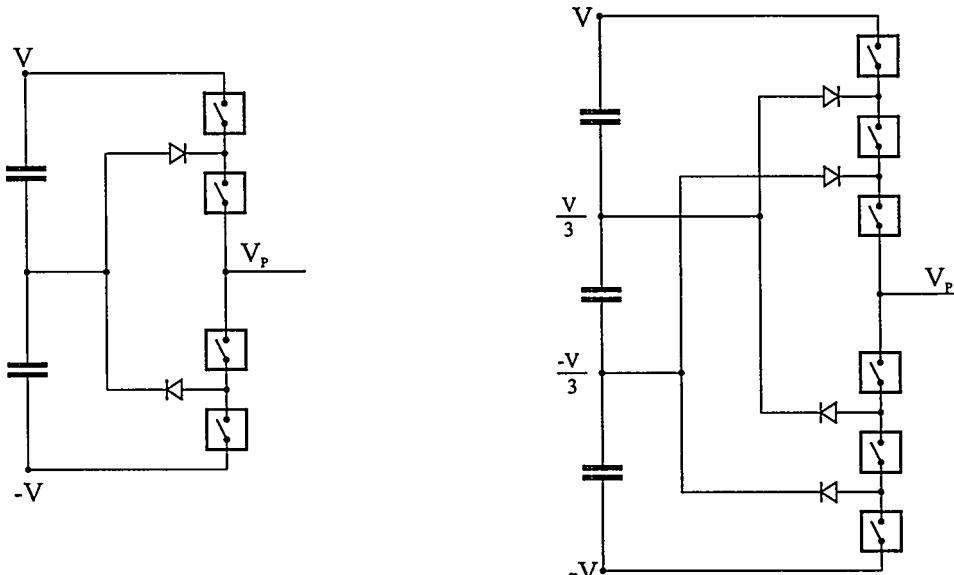

Chapter 5 is devoted to efficiency optimization in the power conversion stage of PMAs. Starting with a simple switching leg, the analysis extends to the general multi-level PSCPWM power stage topologies.

**Part III** (Chapters 6-9) continues to the third major block of the PMA – control system design.

Chapter 6 investigates the application of robust linear control to analog PMA systems. A methodology for control system design is introduced. Three fundamental linear control methods are investigated, and robust case example designs are synthesized and analyzed.

Chapter 7 is devoted the presentation of a control method, dedicated to solve the fundamental problems in analog PMA systems – Multivariable Enhanced Cascade Control (MECC).

Chapter 8 investigates the application of non-linear control methods for analog PMAs. The focus is on a new non-linear modulator/controller structure – Three level One Cycle Control (TOCC). Advantages and disadvantages compared with linear control are emphasized.

Chapter 9 is dedicated to the complex issues of error correction in digital PMA systems. A new control method for enhanced power amplification of a pulse modulated signal is presented – Pulse Edge Delay Error Correction (PEDEC). PEDEC based digital PMA topologies are presented and evaluated.

**Part IV** (Chapter 10) is devoted to implementation and evaluation.

Chapter 10 is dedicated to the practical evaluation of all investigated principles and topologies. Performance specifications for the various prototypes developed during the project are presented.

Chapter 11 summarizes the essence of the thesis and draws the essential conclusions.

Volume II contains three appendices:

Appendix A supplements Chapter 1. Investigations of power and energy efficiency for various amplifier concepts are carried out.

Appendix B supplements Chapter 2. Details of the derivation of analytical double Fourier series expressions for a broad range of analog pulse modulation methods are given.

Appendix C is a complete reproduction of the conference and journal papers that have been published at during the project.

## Part I

### Chapter 2

## Analog Pulse Modulation

This chapter is dedicated to *analog* pulse modulation characterized by the use of an analog reference input to the pulse modulator. It is attempted to devise modulation strategies that will lead to the optimal PMA performance. This is carried out by a fundamental review and comparison of known pulse modulation methods, followed by investigations of new enhanced pulse modulation methods with improved characteristics. The analysis is based on the derivation of Double Fourier Series (DFS) expressions for all considered methods, and the introduction for a spectral analysis tool – the Harmonic Envelope Surface (HES) – based on the analytical DFS expressions. The HES offers detailed insight in the (for PMAs) interesting aspects and the tool proves indispensable of a coherent analysis and comparison of extensive set of pulse modulation methods that are investigated throughout this central chapter. A new multi-level modulation method – Phase Shifted Carrier Pulse Width Modulation (PSCPWM) [Ni97b] – is introduced and subjected to a detailed investigation. A suite of PSCPWM methods are defined each with distinct characteristics, and it will appear that the principle provides optimal pulse modulation for PMAs from a theoretical point of view.

### 2.1 Fundamental pulse modulation methods

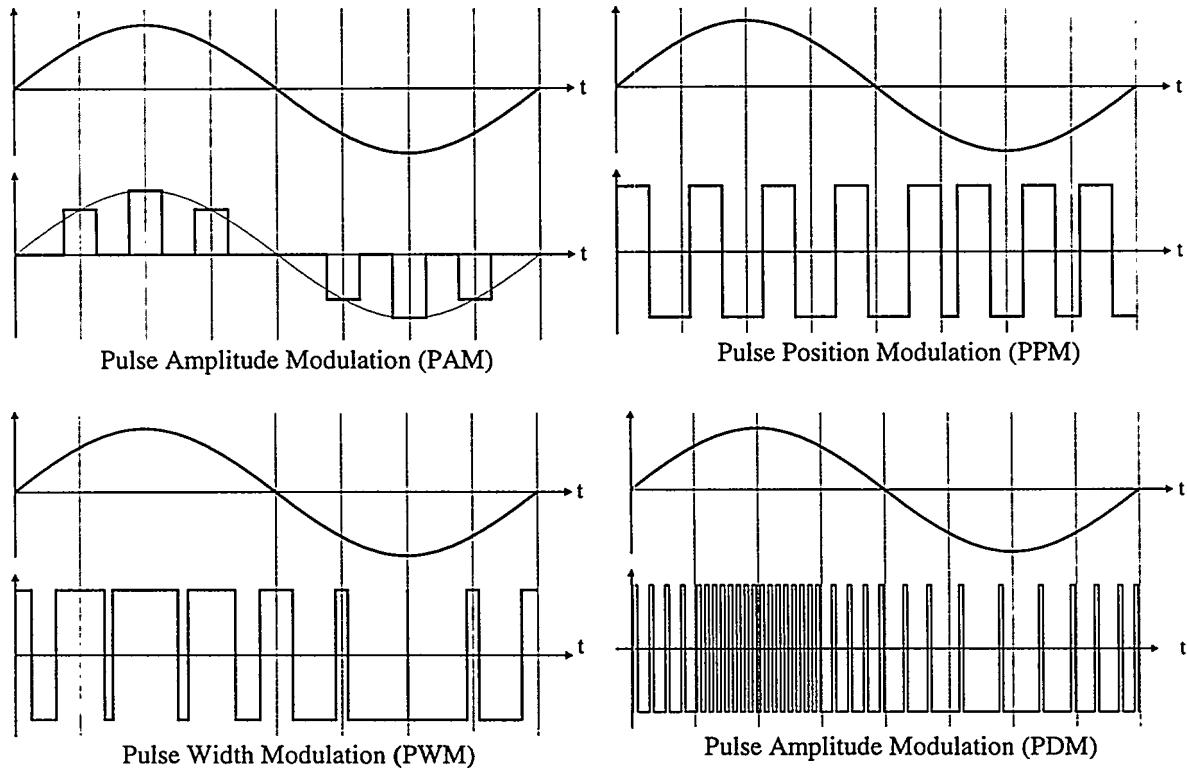

Pulse modulation systems represent a message-bearing signal by a train of pulses. The four basic pulse modulation techniques are [Bl53] *Pulse Amplitude Modulation* (PAM), *Pulse Width Modulation* (PWM), *Pulse Position modulation* (PPM) and *Pulse Density*

Fig. 2.1 Fundamental pulse modulation methods

**Modulation (PDM).** Fig. 2.1 illustrates these four fundamental principles of analog pulse modulation. Pulse Amplitude Modulation (PAM) is based on a conversion the signal into a series of amplitude-modulated pulses as illustrated in Fig. 2.1. The bandwidth requirements are given by the Nyquist sampling theorem, so the modulated signal can be uniquely represented by uniformly spaced samples of the signal at a rate higher or equal to two times the signal bandwidth. An attractive feature of PAM is this low bandwidth requirement resulting in a minimal carrier frequency, which would minimize the power dissipation in a switching power amplification stage. Unfortunately, PAM is limited by the requirements for pulse amplitude accuracy. It turns out to be problematic to realize a high efficiency power output stage that can synthesize the pulses with accurately defined amplitude. If only a few discrete amplitude levels are required, as it is the case with the other three pulse modulation methods, the task of power amplification of the pulses is much simpler.

Pulse Width Modulation (PWM) is dramatically different form PAM in that it performs sampling *in time* whereas PAM provides sampling in amplitude. Consequently, the information is coded into the pulse time position within each switching interval. PWM only requires synthesis of a few discrete output levels, which is easily realized by topologically simple high efficiency switching power stages. On the other hand, the bandwidth requirements for PWM are typically close to an order of magnitude higher than PAM. This penalty is well paid given the simplifications in the switching power stage / power supply.

Pulse Position Modulation (PPM) differs from PWM in that the value of each instantaneous sample of a modulating wave is caused to vary the position in *time* of a pulse, relative to its non-modulated time of occurrence. Each pulse has identical shape independent of the modulation depth. This is an attractive feature, since a uniform pulse is

| Type | Bandwidth Requirements | Modulation depth | Efficiency | Complexity |

|------|------------------------|------------------|------------|------------|

| PAM  | +                      | +                | -          | -          |

| PPM  | -                      | -                | -          | -          |

| PWM  | -                      | +                | +          | +          |

| PDM  | -                      | +                | +          | +          |

Table 2.1 Qualitative comparison of basic pulse modulation methods

simple to reproduce with a simple switching power stage. On the other hand, a limitation of PPM is the requirements for pulse amplitude level if reasonable powers are required. The power supply level of the switching power stage will have to be much higher than the required load voltage. This leads to sub-optimal performance on several parameters as efficiency, complexity and audio performance.

Pulse Density Modulation is based on a unity pulse width, height and a constant time of occurrence for the pulses within the switching period. The modulated parameter is the *presence* of the pulse. For each sample interval it is determined if the pulse should be present or not, hence the designation *density* modulation. It is appealing to have a unity pulse since this is easier to realize by a switching power stage. Another advantage is the simplicity of modulator implementation. However, PDM requires excess bandwidth generally beyond what is required by e.g. PWM.

A qualitative comparison of the four fundamental methods is shown in Table 2.1. Only PDM and PWM are considered relevant, i.e. potential candidates to reach the target objectives.

## 2.2 Analog Pulse Density Modulation (PDM)

Pulse density modulation is now investigated more closely. A simple way to realize a PDM based amplifier is the use of a conventional analog pulse density modulator with a linear loop filter, followed by a switching power stage [KI92]. However, by integrating a switching amplification stage in the noise shaping loop an interesting power PDM topology arrives as shown in Fig. 2.2. This power PDM was first introduced as a method for switching amplifiers in [KI92] followed by subsequent investigations in [KI93] and recently in [Iw96]. Unfortunately, there are several inherent complications with PDM for pulse modulated power amplifier systems. The loop filter has to be of higher order for satisfactory performance within the target frequency band, due to the immense amount of noise generated by the pulse modulating quantizer. The realization of higher order loop filters for both analog and digital pulse density modulators have received much attention in previous research. An attractive higher order topology was presented in [Ch90], and is shown in Fig. 2.3. This higher order structure is suited for analog power PDM systems as

Fig. 2.2 Power SDM topology.

Fig. 2.3 Higher order analog PDM loop filter realization.

shown in [kl93]. Unfortunately, there are limits on filter order when implemented in the analog domain due to tolerances and other analog imperfections. A fourth (or higher) order filter is generally necessary for optimal implementation of power PDM system in reasonable quality. Even with a fourth order filter, the resulting sampling frequency is in the range 2.5MHz - 3MHz for reasonable audio performance in the general case where the target bandwidth is 20KHz. Subsequently, the pulse repetition frequency will be 50-100 times the bandwidth limit of a full audio range system [Kl92]. This is problematic since physical limitations within the switching power amplification stage will introduce switching losses and error that increase with switching frequency. Especially the quiescent power dissipation will be compromised by a high switching frequency. A further drawback is the limits on modulation depth with a higher order PDM [Kl92, Kl93]. This will further compromise efficiency and quiescent power dissipation since the pulse amplitude levels will get relatively higher. In conclusion, the simple and elegant analog power PDM topology is compromised by several essential limitations, mostly relating to the power amplification stage. Consequently, analog PDM is not considered optimal for PMA implementation since PWM as it will become apparent does not suffer from such drawbacks to the same degree.

## 2.3 Analog Pulse Width Modulation

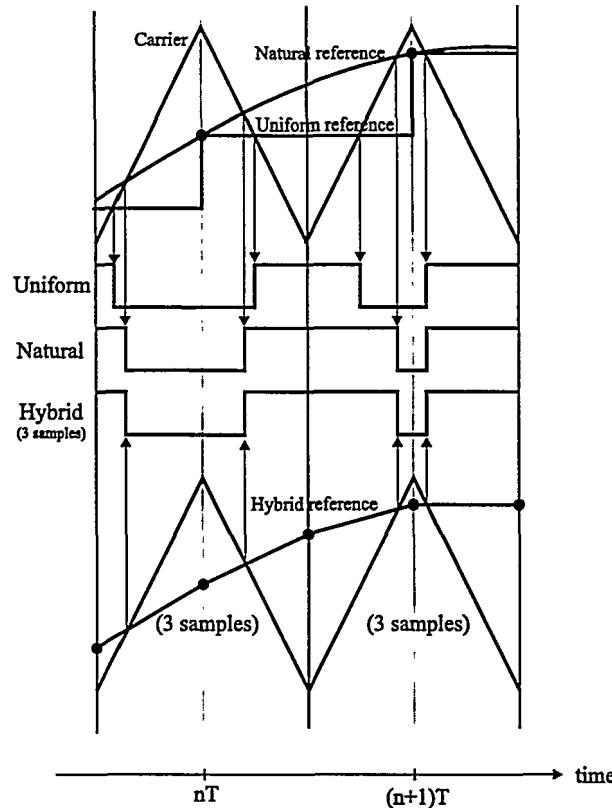

In general, previous research in the field of pulse width modulation as e.g. [Bl53], [Ma67], [Bo75a], [Bo75b], [Se87], [Me91], [Go92], [Hi94] has focused on a limited set of schemes. No coherent work exists with a comprehensive analysis and comparison of pulse width modulation methods, and certainly not with PMAs as a specific application. Further motivating factors for a detailed review and comparison of PWM methods schemes is that interesting characteristics of the more known modulation schemes have not drawn sufficient attention. Traditionally, pulse width modulation is categorized in two major classes by the sampling method: natural sampled PWM (NPWM) and uniform sampled PWM (UPWM). Alternative sampling methods exists which can be categorized as hybrid sampling methods since the nature of sampling lies between the natural and uniform sampling. The principles of the different sampling methods are illustrated in Fig. 2.4. This section focuses on inherently analog pulse modulation methods. The “digital” UPWM and hybrid sampled PWM are discussed in the next chapter. Besides the sampling method, PWM is traditionally also differentiated by the *edge modulation* and by the *class*. The edge modulation may be *single sided* or *double sided*. The modulation of both edges doubles the information stored in the resulting pulse train, although the pulse train frequency is the same. *Class AD* and *Class BD* are the (somewhat misleading but standardized)

Fig. 2.4 Samplings methods in PWM.

abbreviations to differentiate between two-level and three-level switching as introduced in [Ma70]. Although the approach of synthesizing three-level waveforms here differ from the method in [Ma70], the designation BD is kept during this fundamental analysis for coherence with previous work. The resulting four fundamental NPWM schemes are summarized in Table 2.2. An abbreviation has been assigned for each scheme in order to able to differentiate between the methods:

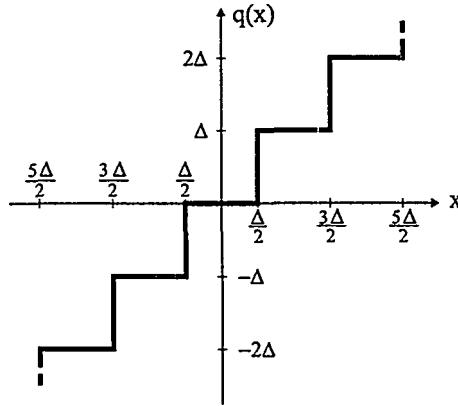

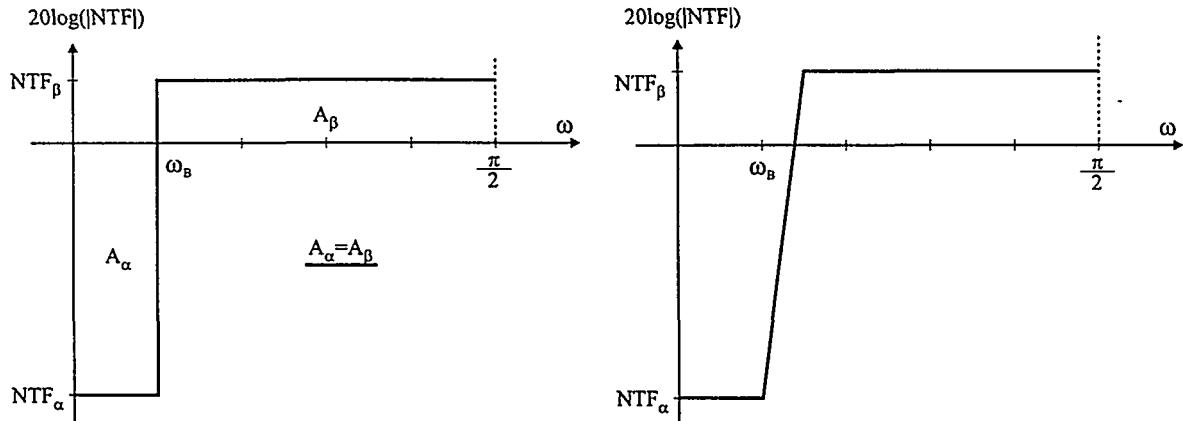

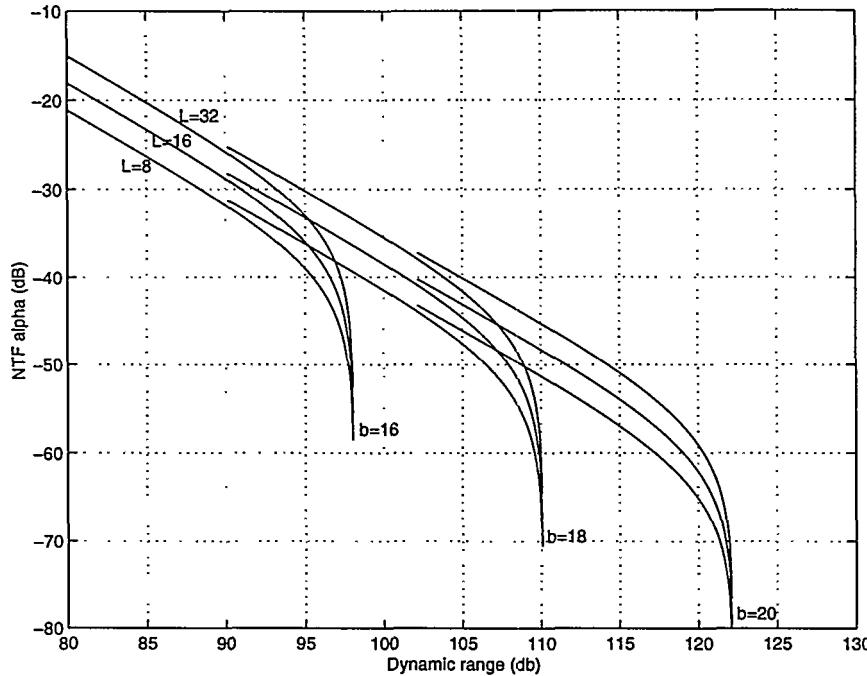

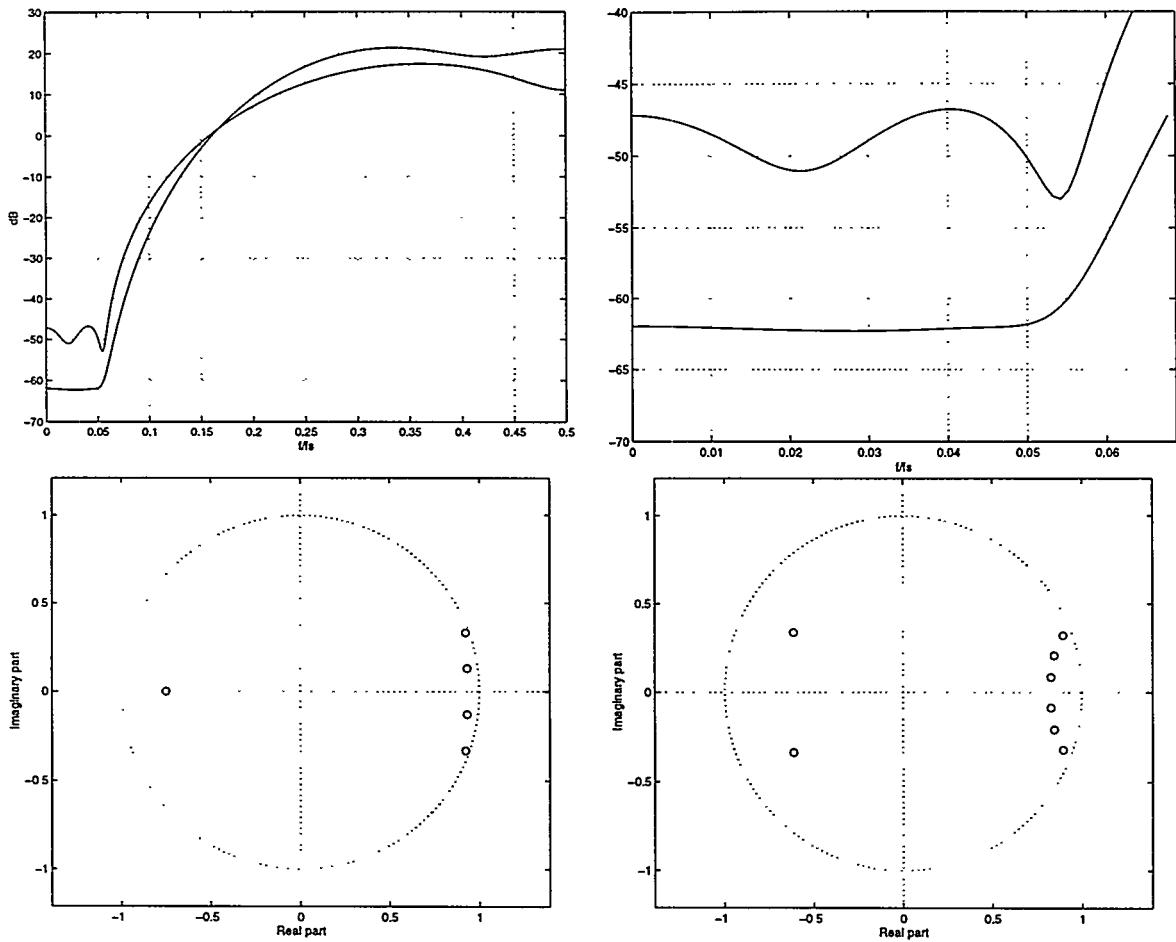

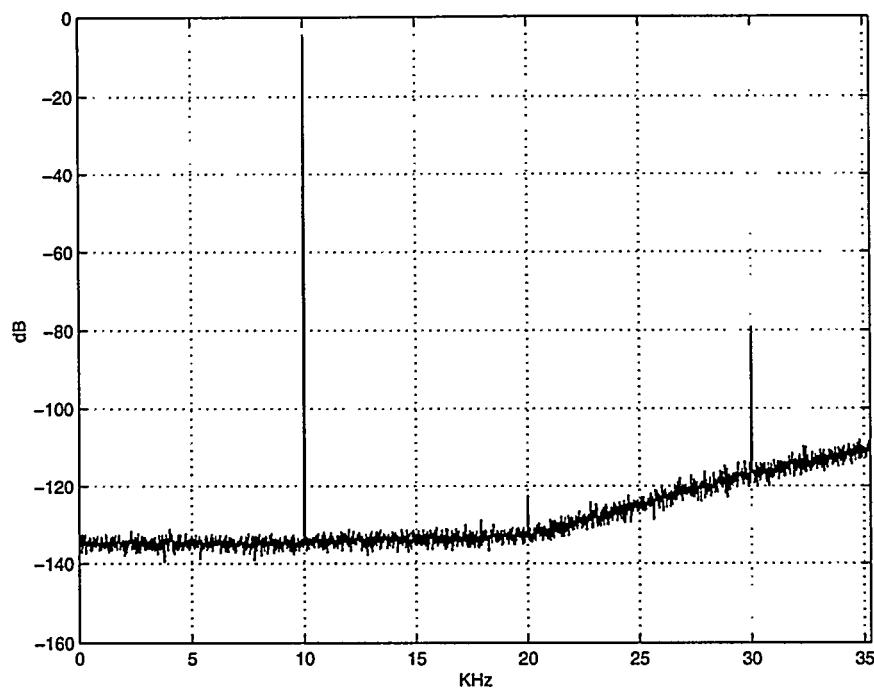

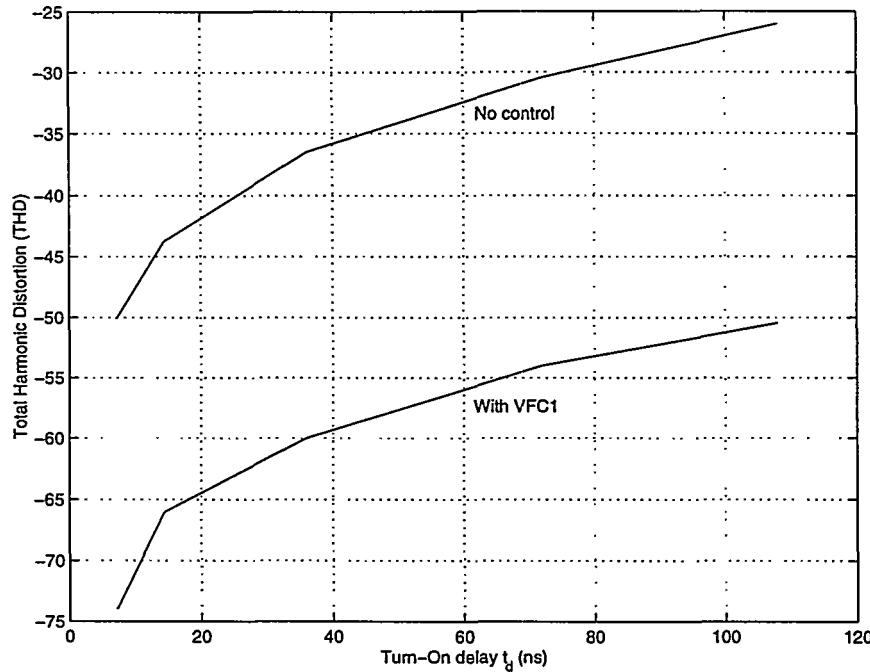

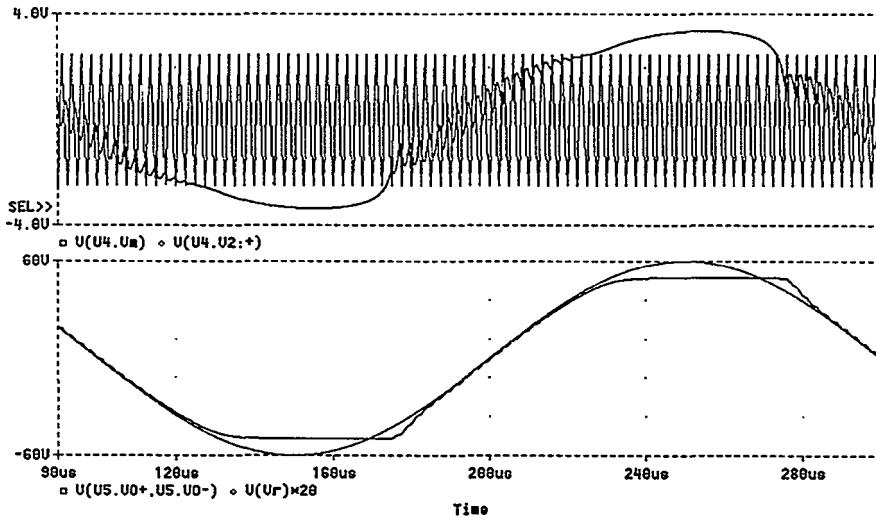

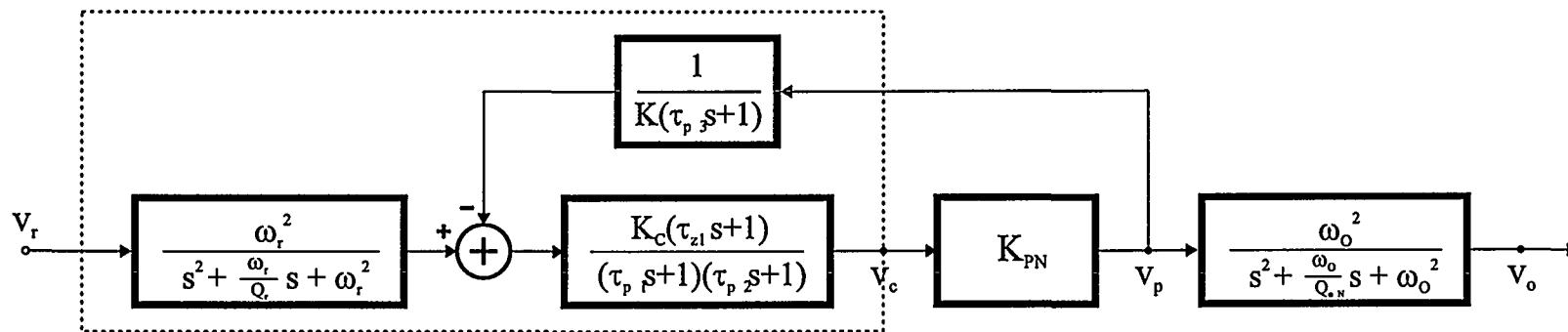

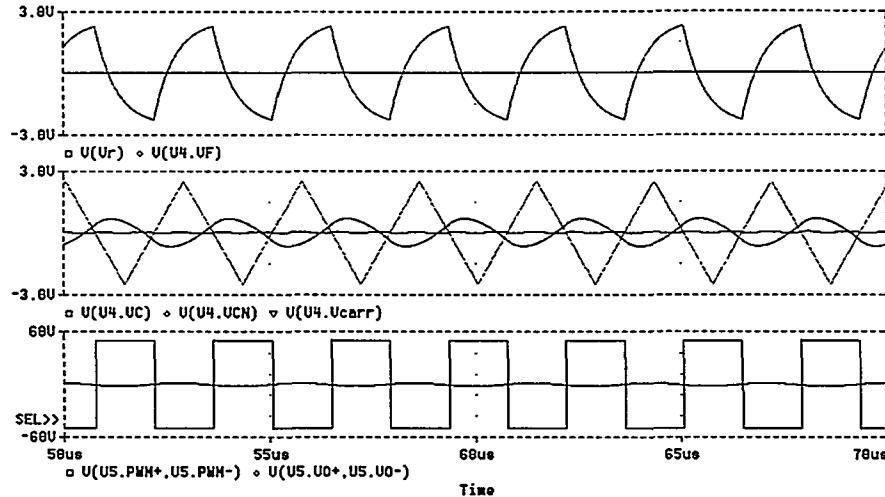

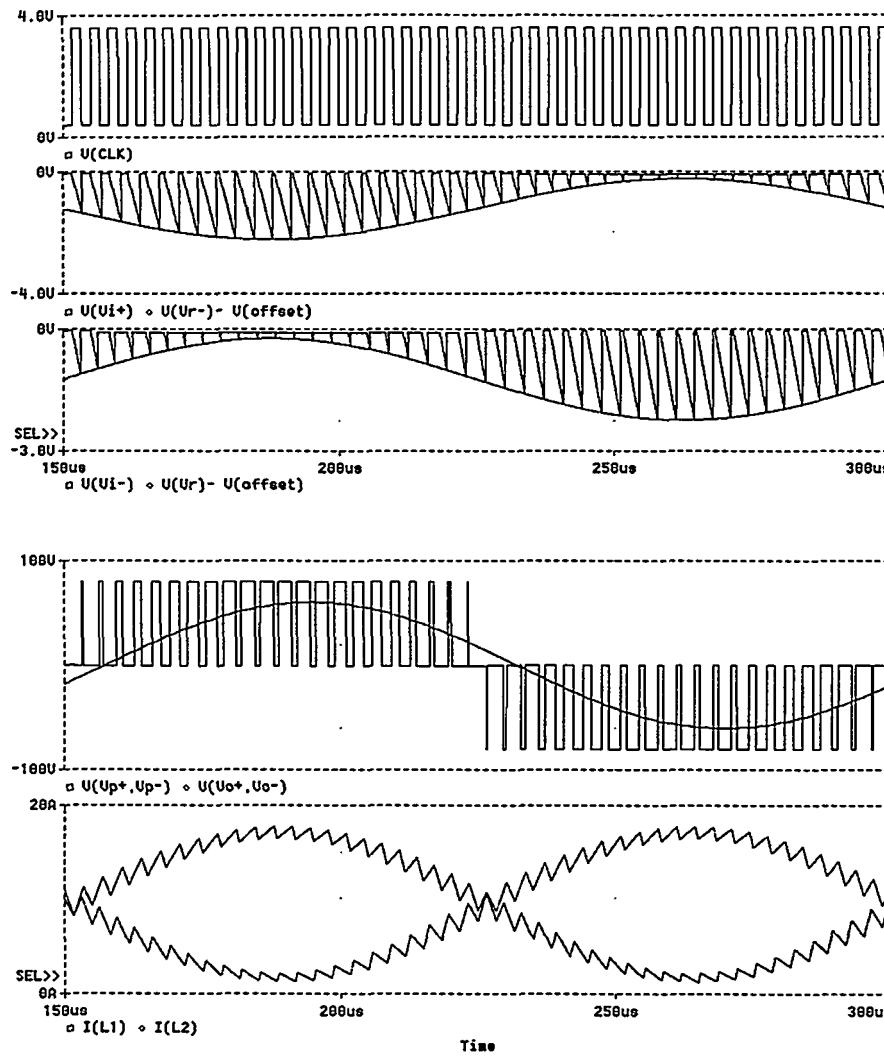

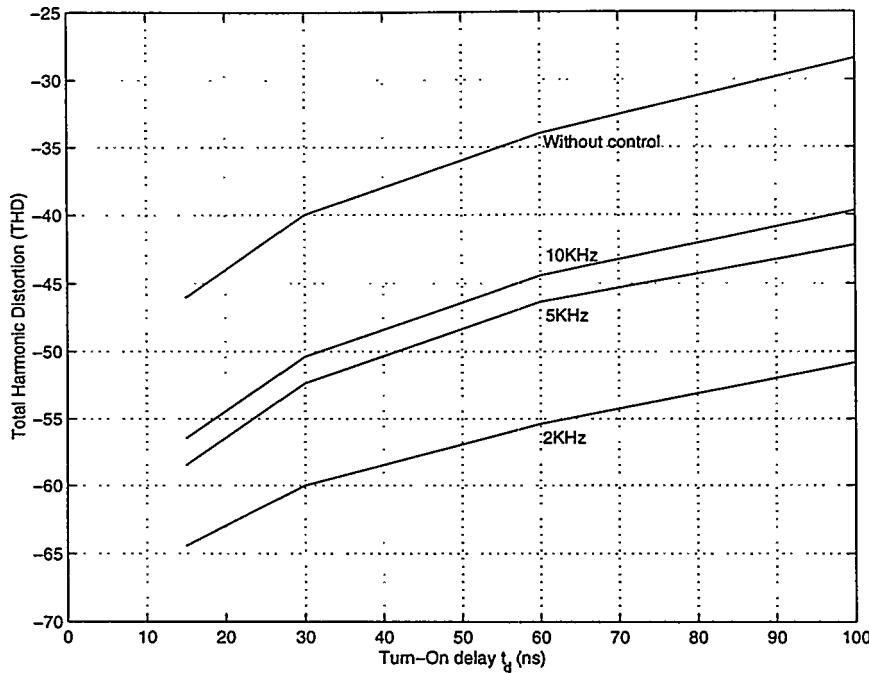

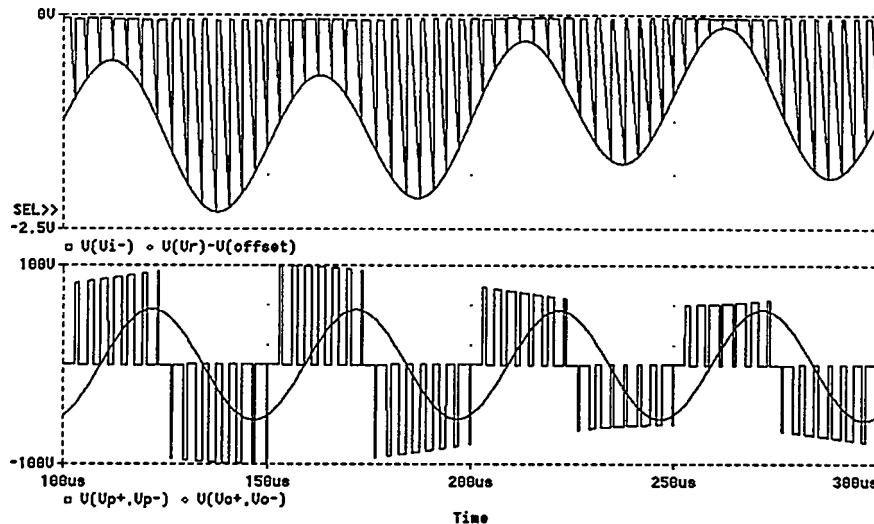

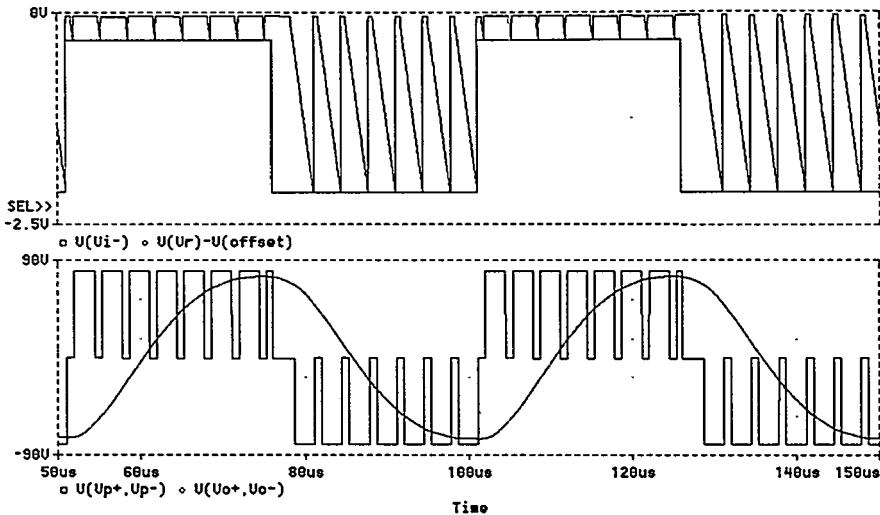

{Sampling Method}{Switching}{Edge}