NANDFlashSim: High-Fidelity, Microarchitecture-Aware NAND Flash Memory Simulation [NANDFlashSim: Intrinsic Latency Variation Aware NAND Flash Memory System Modeling and Simulation at Microarchitecture Level]

Abstract

As the popularity of NAND flash expands in arenas from embedded systems to high-performance computing, a high-fidelity understanding of its specific properties becomes increasingly important. Further, with the increasing trend toward multiple-die, multiple-plane architectures and high-speed interfaces, flash memory systems are expected to continue to scale and cheapen, resulting in their broader proliferation. However, when designing NAND-based devices, making decisions about the optimal system configuration is nontrivial, because flash is sensitive to a number of parameters and suffers from inherent latency variations, and no available tools suffice for studying these nuances. The parameters include the architectures, such as multidie and multiplane, diverse node technologies, bit densities, and cell reliabilities. Therefore, we introduce NANDFlashSim, a high-fidelity, latency-variation-aware, and highly configurable NAND-flash simulator, which implements a detailed timing model for 16 state-of-the-art NAND operations. Using NANDFlashSim, we notably discover the following. First, regardless of the operation, reads fail to leverage internal parallelism. Second, MLC provides lower I/O bus contention than SLC, but contention becomes a serious problem as the number of dies increases. Third, many-die architectures outperform many-plane architectures for disk-friendly workloads. Lastly, employing a high-performance I/O bus or an increased page size does not enhance energy savings.

- Authors:

-

- Yonsei Univ., Incheon (Korea)

- Pennsylvania State Univ., University Park, PA (United States)

- Intel, Santa Clara, CA (United States)

- Panasas, Pittsburgh, PA (United States)

- Lawrence Berkeley National Lab. (LBNL), Berkeley, CA (United States)

- Publication Date:

- Research Org.:

- Lawrence Berkeley National Lab. (LBNL), Berkeley, CA (United States)

- Sponsoring Org.:

- USDOE Office of Science (SC)

- OSTI Identifier:

- 1525132

- Grant/Contract Number:

- AC02-05CH11231

- Resource Type:

- Journal Article: Accepted Manuscript

- Journal Name:

- ACM Transactions on Storage

- Additional Journal Information:

- Journal Volume: 12; Journal Issue: 2; Journal ID: ISSN 1553-3077

- Publisher:

- Association for Computing Machinery (ACM)

- Country of Publication:

- United States

- Language:

- English

- Subject:

- 97 MATHEMATICS AND COMPUTING; non-volatile memory; NAND flash memory; cycle-level simulation; solid state disk; performance evaluation

Citation Formats

Jung, Myoungsoo, Choi, Wonil, Gao, Shuwen, Wilson, III, Ellis Herbert, Donofrio, David, Shalf, John, and Kandemir, Mahmut Taylan. NANDFlashSim: High-Fidelity, Microarchitecture-Aware NAND Flash Memory Simulation [NANDFlashSim: Intrinsic Latency Variation Aware NAND Flash Memory System Modeling and Simulation at Microarchitecture Level]. United States: N. p., 2016.

Web. doi:10.1145/2700310.

Jung, Myoungsoo, Choi, Wonil, Gao, Shuwen, Wilson, III, Ellis Herbert, Donofrio, David, Shalf, John, & Kandemir, Mahmut Taylan. NANDFlashSim: High-Fidelity, Microarchitecture-Aware NAND Flash Memory Simulation [NANDFlashSim: Intrinsic Latency Variation Aware NAND Flash Memory System Modeling and Simulation at Microarchitecture Level]. United States. https://doi.org/10.1145/2700310

Jung, Myoungsoo, Choi, Wonil, Gao, Shuwen, Wilson, III, Ellis Herbert, Donofrio, David, Shalf, John, and Kandemir, Mahmut Taylan. 2016.

"NANDFlashSim: High-Fidelity, Microarchitecture-Aware NAND Flash Memory Simulation [NANDFlashSim: Intrinsic Latency Variation Aware NAND Flash Memory System Modeling and Simulation at Microarchitecture Level]". United States. https://doi.org/10.1145/2700310. https://www.osti.gov/servlets/purl/1525132.

@article{osti_1525132,

title = {NANDFlashSim: High-Fidelity, Microarchitecture-Aware NAND Flash Memory Simulation [NANDFlashSim: Intrinsic Latency Variation Aware NAND Flash Memory System Modeling and Simulation at Microarchitecture Level]},

author = {Jung, Myoungsoo and Choi, Wonil and Gao, Shuwen and Wilson, III, Ellis Herbert and Donofrio, David and Shalf, John and Kandemir, Mahmut Taylan},

abstractNote = {As the popularity of NAND flash expands in arenas from embedded systems to high-performance computing, a high-fidelity understanding of its specific properties becomes increasingly important. Further, with the increasing trend toward multiple-die, multiple-plane architectures and high-speed interfaces, flash memory systems are expected to continue to scale and cheapen, resulting in their broader proliferation. However, when designing NAND-based devices, making decisions about the optimal system configuration is nontrivial, because flash is sensitive to a number of parameters and suffers from inherent latency variations, and no available tools suffice for studying these nuances. The parameters include the architectures, such as multidie and multiplane, diverse node technologies, bit densities, and cell reliabilities. Therefore, we introduce NANDFlashSim, a high-fidelity, latency-variation-aware, and highly configurable NAND-flash simulator, which implements a detailed timing model for 16 state-of-the-art NAND operations. Using NANDFlashSim, we notably discover the following. First, regardless of the operation, reads fail to leverage internal parallelism. Second, MLC provides lower I/O bus contention than SLC, but contention becomes a serious problem as the number of dies increases. Third, many-die architectures outperform many-plane architectures for disk-friendly workloads. Lastly, employing a high-performance I/O bus or an increased page size does not enhance energy savings.},

doi = {10.1145/2700310},

url = {https://www.osti.gov/biblio/1525132},

journal = {ACM Transactions on Storage},

issn = {1553-3077},

number = 2,

volume = 12,

place = {United States},

year = {Thu Jan 28 00:00:00 EST 2016},

month = {Thu Jan 28 00:00:00 EST 2016}

}

Web of Science

Figures / Tables:

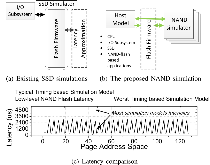

Fig. 1: Concept of a $$μ$$arch-level NAND flash simulation model (NANDFlashSim). While existing SSD simulators are highly coupled to flash firmware emulation with simplified latency model, NANDFlashSim simulates NAND flash memory system itself with independently synchronous clock domains and detailed NAND operation timing models aware of latency variation.

Fig. 1: Concept of a $$μ$$arch-level NAND flash simulation model (NANDFlashSim). While existing SSD simulators are highly coupled to flash firmware emulation with simplified latency model, NANDFlashSim simulates NAND flash memory system itself with independently synchronous clock domains and detailed NAND operation timing models aware of latency variation.

Works referenced in this record:

Real-time garbage collection for flash-memory storage systems of real-time embedded systems

journal, November 2004

- Chang, Li-Pin; Kuo, Tei-Wei; Lo, Shi-Wu

- ACM Transactions on Embedded Computing Systems, Vol. 3, Issue 4

Characterizing flash memory: anomalies, observations, and applications

conference, January 2009

- Grupp, Laura M.; Caulfield, Adrian M.; Coburn, Joel

- Proceedings of the 42nd Annual IEEE/ACM International Symposium on Microarchitecture - Micro-42

FlashSim: A Simulator for NAND Flash-Based Solid-State Drives

conference, September 2009

- Kim, Youngjae; Tauras, Brendan; Gupta, Aayush

- 2009 First International Conference on Advances in System Simulation

Modeling and simulating flash based solid-state disks for operating systems

conference, January 2010

- El Maghraoui, Kaoutar; Kandiraju, Gokul; Jann, Joefon

- Proceedings of the first joint WOSP/SIPEW international conference on Performance engineering - WOSP/SIPEW '10

A case for flash memory ssd in enterprise database applications

conference, January 2008

- Lee, Sang-Won; Moon, Bongki; Park, Chanik

- Proceedings of the 2008 ACM SIGMOD international conference on Management of data - SIGMOD '08

Exploiting Internal Parallelism of Flash-based SSDs

journal, January 2010

- Seon-yeong Park,

- IEEE Computer Architecture Letters, Vol. 9, Issue 1

Modeling Power Consumption of NAND Flash Memories Using FlashPower

journal, July 2013

- Mohan, V.; Bunker, T.; Grupp, L.

- IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 32, Issue 7

Latency lags bandwith

journal, October 2004

- Patterson, David A.

- Communications of the ACM, Vol. 47, Issue 10

Performance impact and interplay of SSD parallelism through advanced commands, allocation strategy and data granularity

conference, January 2011

- Hu, Yang; Jiang, Hong; Feng, Dan

- Proceedings of the international conference on Supercomputing - ICS '11

Figures / Tables found in this record: